VOLUME 46 ISSUE V 2025 AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION SILICONSEMICONDUCTOR.NET MATERIAL SCIENCE INNOVATIONS FOR ADVANCED PACKAGING APPLICATIONS

#### IR LayerRelease™ Technology

- Replacement for mechanical debonding thanks to through-silicon IR laser

- Enabling ultra-thin film or layer transfer from silicon carriers

- Nanometer-precision release of bonded, deposited or grown layers

- Front-end compatibility through silicon carriers and inorganic release materials

- Supporting future roadmaps in advanced packaging and transistor scaling

### BY PHIL ALSOP EDITOR

### The cost of doing something versus the cost of doing nothing

The news pages in this issue of Silicon Semiconductor neatly encapsulate the ongoing dilemma facing individual countries, wider regions and the semiconductor companies themselves when it comes to how best to respond to the significant challenges facing the sector – with geopolitics top of the agenda. Reshoring/onshoring may well be an attractive proposition in terms of taking back control, but the cost of such a policy is colossal – whatever the mix of government and private company investment. Additionally, policies which are intended to promote the idea of local supply chain security might just backfire, as in the story on Page 8 – 'US export controls on AI chips boost domestic innovation in China'. And it is China that seems to dominate the semiconductor landscape at the current time. The Yole report on Page 9 outlines the likely, significant increase in Chinese foundries over the next few years.

Additionally, it would seem that Chinese foundries' ability to manufacture semiconductors at a low price level which others cannot match is having a significant impact on strategic decisions being taken by other players.

More generally, the simple presence of China in the semiconductor market is proving a catalyst for many new initiatives within the industry, which one could argue may or may not have happened in any case. So, China may be seen as a threat by many, but it is also focusing the minds of the competition.

The news on Page 10 – (UK) TechWorks and Canadian Semiconductor Council sign MoU – is a case in point. Would such collaboration have happened pre the current geopolitical uncertainties? And, as on Page 12, would Qatar now be interested in the semiconductor space if the status quo of a few years ago remained today?

What remains to be seen is just what the various semiconductor manufacturing countries and regions, mature

and emerging, do want to do and what they don't want to do in terms of the overall supply chain. And, importantly, once they have made a plan, how can it be implemented effectively?

As the article on Page 46 makes clear, delivering on a strategy is not easy.

'It is very unlikely that the EU will meet its target of a 20 % share of the global market for microchips by 2030, according to a new report by the European Court of Auditors. While the 2022 EU Chips Act has brought new momentum to the European microchip sector, the investments driven by it are unlikely to significantly enhance the EU's position in the field'.

Intriguingly, the report points out that, whatever the EU does itself (and this applies elsewhere to other governments), it is largely at the 'mercy' of the semiconductor companies who, ultimately, will make the crucial investment decisions. Yes, of course, those in charge can offer various incentives (carrots and sticks!), but they cannot force private companies to invest if they do not wish to.

And that perhaps is why China is such a looming presence at the present time, as the link between its government and its semiconductor industry is incredibly close.

Looking ahead, it will be fascinating to see what transpires - to see who wants to play at the very top table, and who wants to identify and occupy smaller, more specialised parts of the semiconductor market.

For your free weekly e-news roundup go to: siliconsemiconductor.net

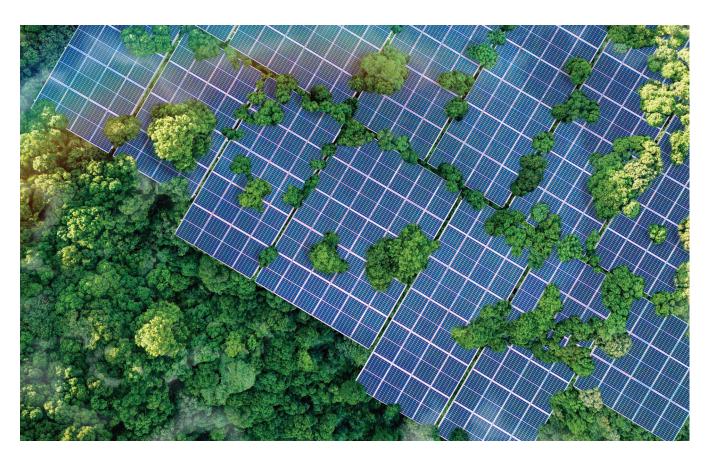

### 14 Accelerating the green transition in the semiconductor industry

SEMI Europe has announced a new three-year Memorandum of Understanding (MoU) with Stockholm Environment Institute (SEI), which will serve as a knowledge partner in the green transition of the semiconductor industry

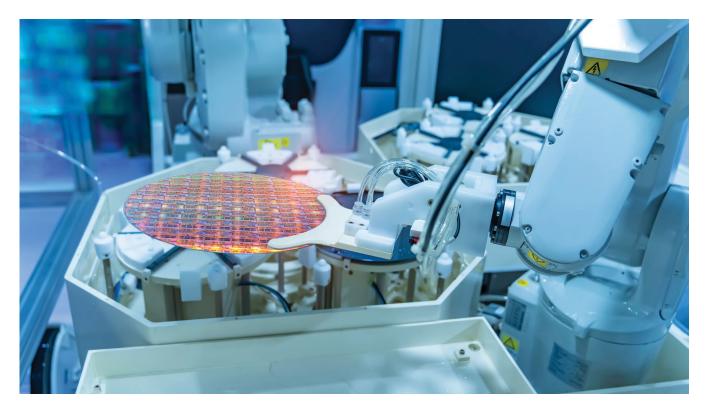

### 18 Semiconductor manufacturing equipment market: endless potential in chip making

The global semiconductor manufacturing equipment market is currently at the forefront of a major technological shift led by the rapid rise of applications like AI, 5G, IoT, automotive electronics, and advanced packaging

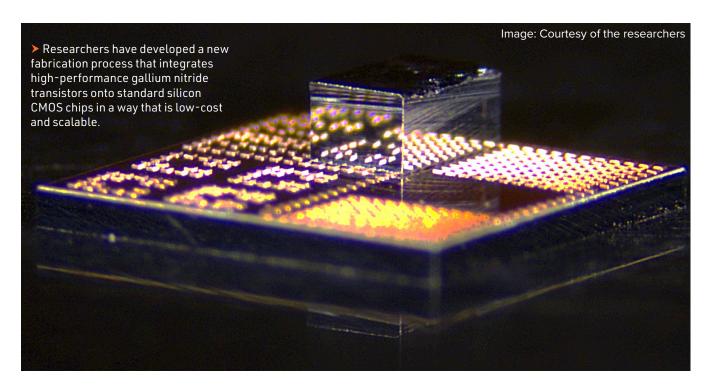

### 20 New 3D chips could make electronics faster and more energy-efficient

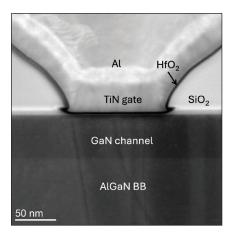

Researchers have developed a new fabrication process that integrates high-performance gallium nitride transistors onto standard silicon CMOS chips in a way that is low-cost and scalable

Terecircuits outlines company's decision to join the US's National Semiconductor Technology Center, contributing its considerable expertise in the synthesis, characterization and delivery of polymers, encapsulants and thin film coatings for advanced packaging

### 22 Applied Materials and CEA-Leti expand joint lab to drive innovation in specialty chips

Based at CEA-Leti, collaboration focuses on materials engineering solutions to enable more energy-efficient Al data centres

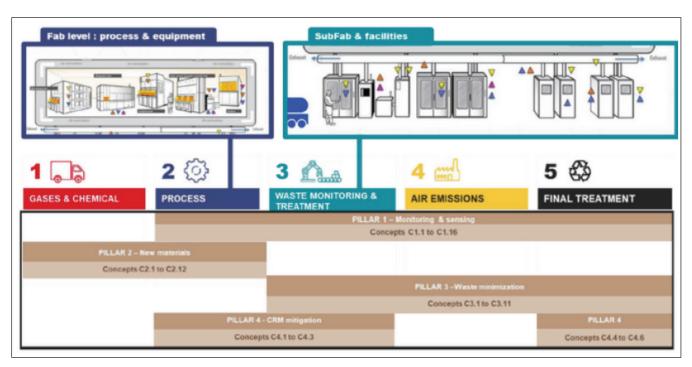

#### 24 GENESIS project launches to lead Europe's transition to sustainable semiconductor manufacturing

58 partners charged with implementing cutting-edge solutions for emission control, materials innovation, waste reduction and raw material reuse

#### 26 EU Project ELENA pioneers LNOI Platform for next-gen photonic circuits

Capacity to deliver millions of TFLN chips annually 'firmly positions Europe as a global leader in photonic chip manufacturing'

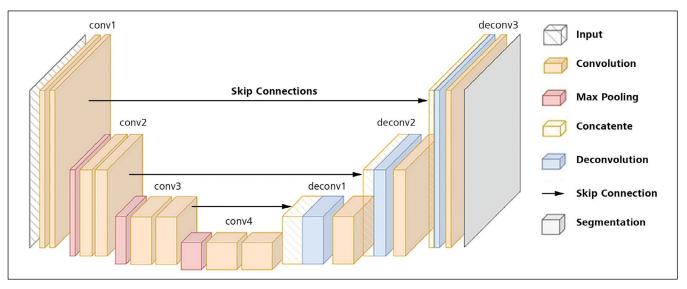

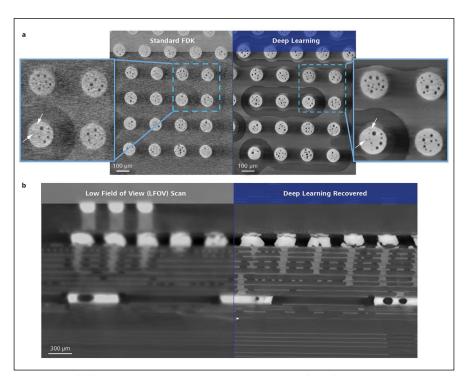

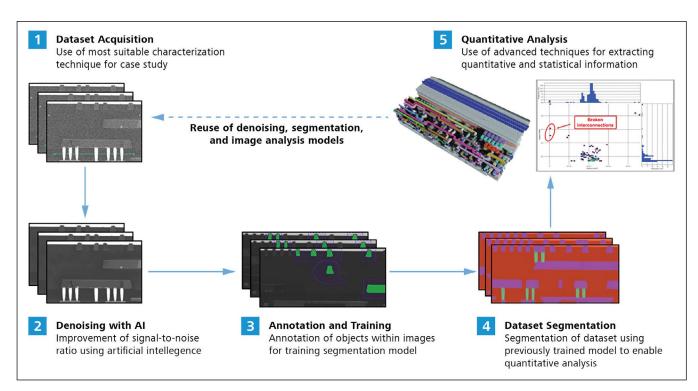

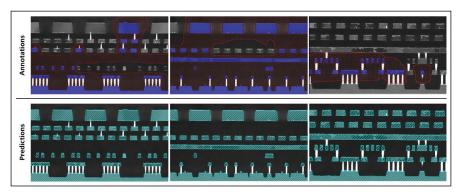

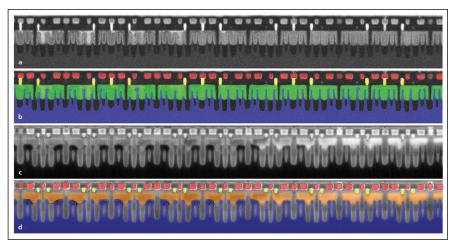

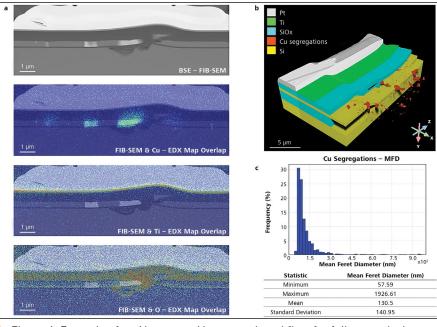

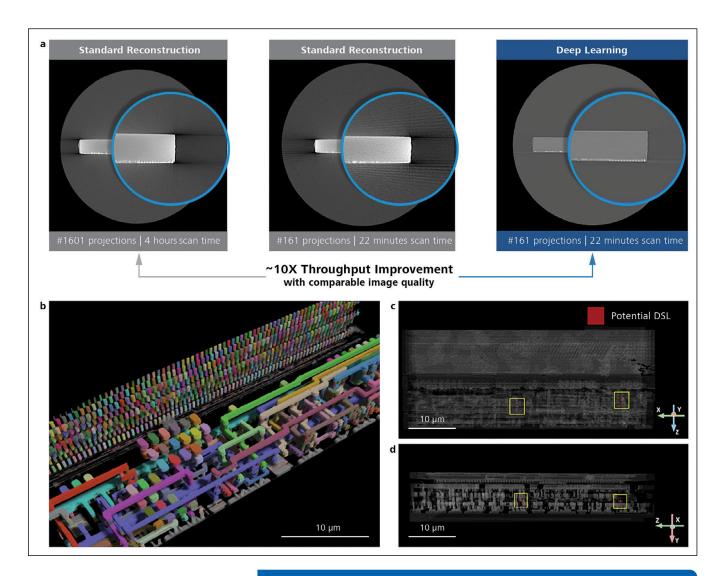

### 28 Artificial intelligence in multimodal microscopy workflows

Examining how the wealth of interconnected data will fuel the development of Al-based predictive models

### 34 Building trust in GenAl for semiconductor design

While Generative AI (GenAI) technologies are already transforming software development and have great potential to improve semiconductor design

#### 42 Scaling quantum

How Cryo-CMOS blueprints bridge the gap to scalable quantum computers.

#### 44 Expert insights on choosing the right test methods for accurate thin film

Measurlabs is a laboratory testing provider with specialised services for the semiconductor industry, offering seamless access to all analytical techniques through a single point of contact

#### 46 EU off the pace in a global race

The target of 20 % global market share by 2030 appears out of reach. Member states and the private sector account for the lion's share of investment

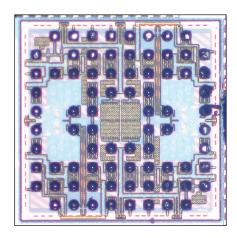

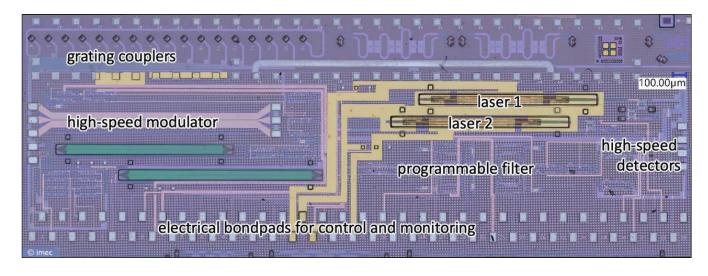

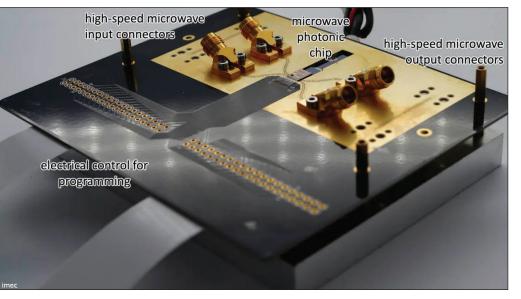

### 50 GaN-on-Si transistor performance, single-chip microwave photonics and DAC

Recent imec research work includes record-breaking RF GaN-on-Si transistor performance for high-efficiency 6G power amplifiers

#### **NEWS**

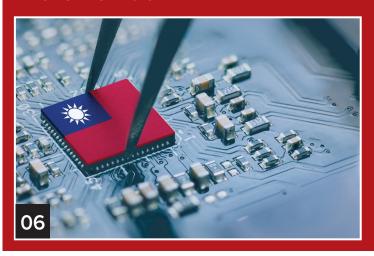

- **06** Strategic silicon: how geopolitics is redirecting semiconductor investment

- **07** High bandwidth memory market is projected to surpass \$25.9 bn by 2034

- **08** US export controls on AI chips boost domestic innovation in China

- **09** Semiconductor foundry landscape to transform by 2030

- 10 TechWorks and Canadian Semiconductor Council sign MoU

- 11 NY CREATES and Fraunhofer Institute to advance memory devices at the 300mm wafer scale

- 12 Invest Qatar partners with Ardian and Silian Partners

Publisher Jackie Cannon

Editor Phil Alsop

Sales & Marketing Manager Shehzad Munshi

Director of Logistics Sharon Cowley

Design & Production Manager Mitch Gaynor

Chief Executive Officer Sukhi Bhadal

Chief Technical Officer Scott Adams

jackie.cannon@angelbc.com phil.alsop@angelbc.com shehzad.munshi@angelbc.com sharon.cowley@angelbc.com mitch.gaynor@angelbc.com sukhi.bhadal@angelbc.com scott.adams@angelbc.com +44 (0)1923 690205

+44 (0)1923 690215

+44 (0)1923 690200 +44 (0)1923 690214 +44 (0)2476 718970

+44 (0)2476 718970

Directors Jackie Cannon, Sharon Cowley

**Published by** Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK.

T: +44 (0)2476 718 970 E: info@angelbc.com

Silicon Semiconductor is published ten times (6x print and 4x video issues) a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00 per annum (UK), £60.00 per annum (Europe), \$90 per annum (air maili)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright versights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2025. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Silicon Semiconductor, Air Business Ltd, v/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, mages, branding, mages, typographic renderings, logos (or similar) when such references/image their names or the images/text used to represent the companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Convintor 2025.

### Strategic silicon: how geopolitics is redirecting semiconductor investment

Geopolitical tensions are redirecting global investments in advanced semiconductor technologies, reshaping the semiconductor supply chain in pursuit of technological sovereignty, according to IDTechEx

THE VAST MAJORITY of the world's most advanced silicon chips are manufactured in Taiwan by a single company - Taiwan Semiconductor Manufacturing Company (TSMC). These chips power everything from data centers to smartphones.

However, Taiwan's central role has become a geopolitical vulnerability. Mounting tension between China and Taiwan, paired with the growing strategic value of advanced semiconductors, has raised global concerns.

In response, governments and corporations have launched a sweeping wave of reshoring efforts. In the U.S. alone, over \$480 billion in semiconductor-related investments were announced between 2024 and 2025. Major contributors include Texas Instruments (\$60B), Micron (\$200B), GlobalFoundries (\$16B), TSMC (\$165B), and Samsung (\$40B), many supported by The Chips Act subsidies. These projects are strategically positioned to develop capabilities across advanced silicon nodes, high-bandwidth memory (HBM), advanced semiconductor packaging, and silicon photonics, all critical to the AI era.

Across Europe, the EU Chips Act is catalyzing local semiconductor ecosystems. TSMC, alongside Bosch, Infineon, and NXP, is co-investing in a 22/28 nm fab in Dresden, backed by the German government. Other key developments include Infineon's €3.5B MEGAFAB project and Silicon Box's €3.2B chiplet facility in Italy. These underscore Europe's ambition to reestablish sovereign manufacturing capacity.

In Japan, TSMC's Kumamoto fab (via JASM) has begun production, and a

second, more advanced fab is under construction. The government has pledged over \$5.4B to Rapidus, aiming for 2 nm pilot production by 2027. South Korea continues expanding its HBM and logic production with strong state backing.

Meanwhile, Taiwan is reinforcing its leadership in advanced semiconductor technologies through strategic regulation. In March 2025, the National Development Council confirmed that TSMC's overseas fabs are subject to the "N-1" rule, which prohibits companies from transferring their most advanced process nodes abroad. Officials outlined three principles: the latest technology must stay in Taiwan, critical IP must not leave, and national security takes priority, ensuring Taiwan remains the hub of cutting-edge chipmaking.

TSMC continues to invest heavily at home, building seven new facilities in 2025, including six fabs and one advanced packaging plant in Taiwan. 2 nm production will ramp in the second half of 2025, and 3 nm output is set to grow 60% this year. The company projects Al-related wafer shipments will be 12× higher than in 2021, with large-die shipments up 8×.

While these investments may enhance national capabilities, they also fundamentally reconfigure the global semiconductor supply chain. Today's semiconductor ecosystem, particularly

for Al chips, is deeply rooted in East Asia, with Taiwan at the center, not only for wafer fabrication but also for advanced packaging, testing, and final assembly. Manufacturing a chip with an advanced node is only the first step; without co-locating downstream processes, it makes little economic sense to fabricate in the U.S. only to ship wafers back to Taiwan for packaging.

Building a fab that manufactures advanced nodes already costs a fortune (Building a 2 nm wafer fab with high-volume output requires an enormous investment, often approaching tens of billions of dollars.), but replicating the entire supporting ecosystem adds substantially more. TSMC's Arizona project illustrates this complexity: to make it operate effectively, TSMC had to rebuild much of its supply chain from Taiwan to the US.

This kind of transition inevitably drives up the cost of advanced chips, and only wealthy nations with strong political and financial backing can afford to play. While the U.S. Chips Act has catalyzed onshoring, the road ahead remains long and difficult. Key challenges include:

- Skilled labor shortages, exacerbated by anti-immigration policies

- Capital intensity, especially amid worsening global economic conditions

- Geopolitical friction, including Taiwan's "N-1" regulation, which restricts export of the most advanced nodes and technologies

- Supply chain immaturity and fragility, as many upstream and downstream partners remain concentrated in

- Policy uncertainty, as government subsidies and permitting shifts, can delay or disrupt projects, especially over multi-year timelines.

### High bandwidth memory market is projected to surpass \$25.9 bn by 2034

The High Bandwidth Memory Market is set to grow from its current market value of more than \$2.3 billion to over \$25.9 billion by 2034; as reported in the latest study by Global Market Insights, Inc.

THE GLOBAL SHIFT toward datacentric technologies is reshaping the landscape of memory solutions, with high bandwidth memory emerging as a critical enabler for faster data processing and energy-efficient computing. As organizations across various sectors race to adopt next-generation technologies, the demand for high-speed, low-latency memory has seen a notable surge.

The growing influence of artificial intelligence (AI), machine learning (ML), advanced driver-assistance systems (ADAS), and 5G networks continues to fuel demand for powerful memory technologies. Enterprises are leaning heavily on HBM to support big data, high-resolution imaging, real-time analytics, and deep learning workloads. With digital transformation accelerating in sectors like automotive, healthcare. financial services, and media, HBM solutions are rapidly becoming foundational to the development of smarter, faster, and more connected systems. Companies worldwide are

responding by investing in cuttingedge innovations and expanding manufacturing capabilities to stay competitive in this rapidly evolving space.

The market is segmented by technology node into below 10nm, 10nm to 20nm, and above 20nm. The 10nm to 20nm category accounted for USD 1 billion in 2024 and is projected to grow at a CAGR of 26.7% between 2025 and 2034. This node has proven ideal for applications requiring balanced performance and cost-efficiency, such as automotive electronics, IoT devices, and mid-range consumer products. Its scalability, coupled with highyield production and reliable thermal management, continues to make it a go-to option for developers aiming to optimize performance without inflating manufacturing costs.

Based on application, the high bandwidth memory market is categorized into GPUs, CPUs, FPGAs, ASICs, AI, ML, HPC, networking, and

data centers. The GPU segment captured a 21.3% share in 2024, supported by soaring demand in professional and immersive gaming ecosystems.

As ultra-high-definition graphics, real-time rendering, and extended reality environments become mainstream, graphics processing units are integrating advanced HBM technologies such as HBM3E to meet rising bandwidth needs. This trend is particularly prominent in the gaming and animation sectors, where rapid refresh rates and responsive user experiences are essential.

### Semiconductor market sustains momentum amidst evolving global dynamics

THIS FIGURE represents a considerable 19.8% increase compared to May 2024, when sales stood at \$49.2 billion, and a 3.5% uplift from April 2025. This sustained upward trajectory offers critical insights for procurement pipelines and supply-chain agility within the electronics sector, particularly as defence industries globally seek advanced technological integration.

The consistent growth in chip sales indicates a robust underlying demand, which is a key consideration for strategic sourcing. According to

John Neuffer, president and CEO of the Semiconductor Industry Association (SIA), "Worldwide chip sales remained strong in May, slightly exceeding April's total and significantly outpacing last year's performance." This sustained performance signals a stable, if not expanding, supply landscape for fundamental electronic components.

Regional sales figures underscore a shifting global dynamic. Year-on-year expansion was observed across all major markets. The Americas led with a substantial 45.2% rise, followed by Asia Pacific/All Other regions at 30.5%, China at 20.5%, Japan at 4.5%, and Europe with a 4.1% increase.

Month-on-month growth also saw Asia Pacific/All Other (6.0%), China (5.4%), and Europe (4.0%) taking the lead, while the Americas and Japan registered more modest increases of 0.5% and 0.2% respectively. This regional disparity necessitates careful consideration for global procurement strategies, particularly concerning lead times and potential geopolitical influences on supply chains.

### US export controls on AI chips boost domestic innovation in China

The discussion around advanced chips for artificial intelligence, driven by billions in investment, dreams of artificial general intelligence, and marred by political concerns over security, has entered a stage of intense competition between nations, says IDTechEx.

NVIDIA achieved revenues of over US\$80 billion from data center GPUs alone in 2024; however, with significant stock going to nations outside of the US, the US government has mandated stringent measures to reduce this flow, citing national security concerns as the reason. China has been particularly affected by this change, with limited access to not only GPUs but also advanced tools required for manufacturing advanced semiconductor technologies.

Whilst these measures create roadblocks for companies across the whole supply chain, they also create the necessity for innovation, with Chinese players demonstrating this already. IDTechEx explores innovations from companies across the Al chips landscape within its semiconductors, computing, and Al portfolio, including a full analysis of the regulations landscape and analysis of international Al chip players, and technologies in the recently released "Al Chips for Data Centers and Cloud 2025-2035: Technologies, Market, Forecasts."

Al chips for data centers, rely on international collaboration in design, manufacturing, and distribution, however the US has cornered China by restricting this collaboration. These Al processors see increasing demand in data centers, but this comes with high energy consumption and capital costs. Source: IDTechEx

Artificial Intelligence (AI) is continuously being adopted into workflows by enterprise and consumers alike, presented as know-it-all generative AI language bots and smart AI agents; however, this is only the final layer of what AI really is. Behind the screen, and on the other side of the internet, are tens of gigawatts of data centers' capacity, with millions of GPUs and

other AI accelerators populating their racks. AI hardware sees governments and hyperscalers pouring hundreds of billions of dollars into building out AI data centers. These continue to be developed to facilitate the growing size of AI models required to deliver the likes of ChatGPT, Claude, Gemini, and other large AI models.

Demand has outstripped the famous Moore's Law scaling, with floating point operations per second (FLOPS) increasing at a rate of four and a half times per year since 2010. For perspective, Llama 3.1-405B, a leading Al model from Meta, requires 3.8x1025 FLOPS of training compute, which in turn requires 16,384 NVIDIA H100 SXM5 80GB nodes. This itself takes 2,142 hours with a power draw of 25,280 W to train, which is equivalent to powering 2,085 US households for a year, when running at 40.42% hardware utilization. This demand for computing is only expected to continue growing, with governments striving to lead in autonomous infrastructure, drug discovery, and military capabilities. IDTechEx forecasts that the AI Chips market will reach US\$453 billion by 2030 at a CAGR of 14% between 2025 and 2030.

The US puts pressure on the global semiconductor supply chain to limit China and other arms-embargoed countries' access to advanced chips Despite US-based fabless chip designers, NVIDIA and AMD, leading in the revenues from AI chip sales, the supply chain is firmly international. Semiconductor manufacture has been dominated by production in Taiwan, with TSMC leading the production of the majority of advanced AI chips. Advanced memory technologies providers have been split between the US and South Korea, with high bandwidth memory (HBM) designed

by SK Hynix, Samsung, and Micron Technology. Lithography equipment, specifically extreme ultra-violet (EUV lithography), is firmly dominated by the Netherlands' ASML. However, the US has imposed various strategies to limit China's ability to not only access advanced chips, but also equipment.

The US's limitations on China's access to advanced chips are by no means a new story, but it is a tale that gets more rigid year on year. October 2022, during Biden's presidency, saw the Bureau of Industry and Security (BIS) introduce controls restricting China's ability to obtain advanced computing chips, develop supercomputers, and manufacture advanced semiconductors, on the grounds of preventing these technologies from being used for military applications and human rights abuses. The controls were updated to enhance effectiveness and close loopholes in October 2023, which were formed of stricter limitations destined for countries of concern, particularly

In December 2024, the BIS further strengthened these controls by adding 24 types of semiconductor manufacturing equipment and three types of software tools to the restricted list. Additionally, 140 Chinese entities were added to the Entity List, requiring special licenses for US businesses to supply them. This move creates a chokehold on Chinese manufacturers to produce advanced chips for AI.

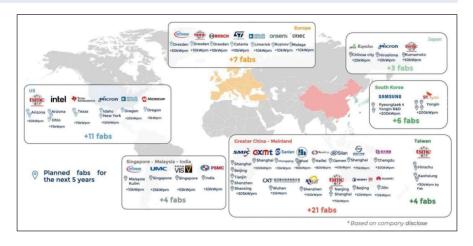

### Semiconductor foundry landscape to transform by 2030

Yole Group's new report, Status of the Semiconductor Foundry Industry, explores the geopolitical, economic, and capacity realignments reshaping the semiconductor foundry industry.

YOLE GROUP unveils its latest Status of the Semiconductor Foundry Industry report, offering a comprehensive view into a sector undergoing profound transformation. At the crossroads of technology, geopolitics, and global market dynamics, this ecosystem is being reshaped by new capacity investments, regional power shifts, and long-term national strategies.

Yole Group's 2025 analysis highlights how the global semiconductor supply chain remains highly fragmented and increasingly vulnerable to geopolitical tensions. Since the U.S. launched a semiconductor-focused trade war, mainland China has ramped up efforts to build a self-sufficient domestic ecosystem. In response, governments worldwide have launched significant subsidy programs to re-localize and fortify their semiconductor infrastructure.

One of the most impressive contrasts identified is in the U.S. market. Pierre Cambou, Principal Analyst, Global Semiconductors at Yole Group, comments: "While American semiconductor companies account for 57% of global wafer demand, they control only about 10% of foundry capacity locally. Indeed, the U.S. ecosystem relies heavily on foundry players located in Taiwan, Japan, and mainland China."

In contrast, Taiwan controls 23% of global foundry capacity but accounts for only 4% of wafer demand, as highlighted by Yole Group in its 2025 foundry report. Taiwanese foundry players mainly supply the US fabless ecosystem through players like TSMC, UMC, and VIS. South Korea with players, such as Samsung, is mostly satisfying its domestic demand with an equal share of global capacity and wafer demand at 19%.

The Status of the Semiconductor Foundry Industry report reveals the worldwide capacity and its distribution as well as regional dependencies. It analyzes this dynamic landscape and how it is expected to evolve.

Mainland China is rapidly becoming a central player. In 2024, it held 21% of foundry capacity despite generating just 5% of global wafer demand. Much of this excess capacity is either foreign-owned or offered as open foundry services, although utilization rates remain below the global average. By 2030, China is projected to dominate the global foundry landscape, accounting for 30% of installed capacity, outpacing Taiwan, South Korea, and Japan.

Europe and Japan are holding steady in terms of the supply-demand balance, though much of their foundry capacity is tied to their own internal market. The Southeast Asian region, especially Singapore and Malaysia, owns 6% of global foundry capacity, although it lacks domestic players and therefore operates entirely on foreign-owned foundries.

Despite fears of overinvestment, Yole Group forecasts that the 4.3% CAGR in foundry capacity will not result in severe overcapacity. Global utilization is expected to hover around 70% through 2030. This relatively low utilization rate will become the new normal. Without a corresponding surge in wafer production and end-market demand, the return on these capital-intensive expansions may fall short.

"The foundry market is more of a capitalistic game than a product competition," explains Pierre Cambou from Yole Group. "Ownership, location, and utilization must now be read through national interests, economic security, and long-term technology strategy."

While U.S.-based players still control roughly 20% of global capacity, 10% locally and 10% abroad, China's domestic players are rapidly expanding own local capacity from 15% in 2024 to significantly more by 2030. This growing divergence between where capacity is built and who owns it points to future uncertainties in market access, supply chain transparency, and strategic leverage.

There's a clear geographical overweight toward Asia, and that will only deepen. The global foundry market will be decided less by where fabs are located and more by who owns them.

### TechWorks and Canadian Semiconductor Council sign MoU

TechWorks, the UK industry association for semiconductor and deep tech innovation, has signed a landmark Memorandum of Understanding (MoU) with the Canadian Semiconductor Council (CSC) to foster strategic collaboration between the UK and Canadian semiconductor ecosystems.

THE AGREEMENT recognises the highly complementary strengths of both nations in areas such as advanced packaging, compound semiconductors, quantum technologies, Al, neuromorphic processors, sustainable materials, and more. While traditional high-volume digital CMOS production manufacturing has shifted eastward, the UK and Canada remain at the forefront of innovation across emerging technologies critical to future global competitiveness.

This coincides with the meeting this week in Ottawa between Sir Keir Starmer, Prime Minister of the United Kingdom (UK) and Mark Carney, Prime Minister of Canada to reaffirm the strength of the Canada-UK partnership, deepening trade ties as trusted partners and, in particular, agreeing to work together to enhance both nations' complementary strengths in semiconductors, photonics, emerging materials and chip design.

Their commitment underscores the vision set out in the MoU to build resilient supply chains and accelerate breakthroughs in this key economic growth sector, which is of great importance to both countries.

Charles Sturman, CEO of TechWorks, commented, "This partnership represents a significant milestone for our respective semiconductor industries. By connecting two innovation-rich ecosystems, we are opening the door to deeper collaboration in R&D, talent development, and commercial opportunity. Through shared strengths and common mind-set, we can help build resilient supply chains and accelerate the technologies that will define the next decade."

The MoU sets out a long-term collaborative framework based on:

- Sharing market intelligence, roadmaps, and best practices

- Promoting business-to-business collaboration and trade missions

- Supporting workforce development and academic partnerships

- Facilitating bilateral R&D initiatives, including participation in international innovation programs

Both countries aim to enhance their global competitiveness by increasing trade, foreign direct investment, and innovation output across the full semiconductor and microelectronics value chain—from design to manufacturing to end-use applications in Al, IoT, communications, mobility, and more

"Canada and the UK have long shared a rich history of collaboration, and this agreement is a natural next step in addressing the growing need for deeper cooperation in the semiconductor sector – especially as global trade dynamics continue to shift rapidly," said Paul Slaby, Managing Director of Canada's Semiconductor Council. "By strengthening ties and leveraging our mutual strengths, we can create new opportunities and lasting impact for both nations."

The UK Science Minister, Lord Vallance said: "This new partnership reflects

the UK and Canada's shared commitment to strengthening semiconductor supply chains and deepening international cooperation in critical technologies.

"It will help create new opportunities for businesses and researchers and support our Plan for Change through long-term economic growth."

The Honourable Mélanie Joly, Minister of Industry and Minister responsible for Canada Economic Development for Quebec Regions added:

"Canada and the United Kingdom's partnership demonstrates our shared commitment to advancing innovation and building economic resilience. We are strengthening our leadership in innovation, reinforcing secure supply chains, and creating new opportunities for businesses and researchers on both sides of the Atlantic."

TechWorks and CSC are also working with the UK and Canadian governments to support innovation and economic growth in this critical sector, supporting a jointly funded research and development program focusing on advanced packaging, photonics, and emerging materials. This was recently launched by Innovate UK and Canada's National Research Council Industrial Research Assistance Program (NRC IRAP).

The program aims to foster innovation and resilient supply chains: https://iukbusiness-connect.org.uk/opportunities/canada-uk-semiconductors-2025/.

The call for proposals is open to Canadian and UK organisations who wish to form project consortia to collaborate on innovative products, processes, or technology-based services.

### NY CREATES and Fraunhofer Institute to advance memory devices at the 300mm wafer scale

NY CREATES and Fraunhofer IPMS has announced at a signing ceremony a new Joint Development Agreement (JDA) to drive research and development focused on memory devices.

THE JDA will leverage and link the strengths of each organization to engineer, develop, and characterize these devices that are critical for advancing the memory development ecosystems of each respective organization.

"As we build upon the strong connections, we have with semiconductor R&D centers around the globe to create the technologies that the U.S. and the world will rely on in the future, we look forward to this collaboration with Fraunhofer IPMS to further develop next-generation ferroelectric memory devices at the 300mm scale," said Dave Anderson, President of NY CREATES.

"We are proud to work together to accelerate the processes and the evaluation and deployment of these materials which can lead to innovative breakthroughs, maintaining our global R&D leadership. With the Center Nanoelectronic Technologies (CNT), Fraunhofer IPMS maintains a leading international competence center for the development of ferroelectric memories based on hafnium oxide (HfO<sub>2</sub>). These memory technologies are particularly promising for neuromorphic computing applications as they are very energy efficient, CMOS compatible and scalable down to very small technology nodes. We look forward to working with NY CREATES to develop new promising memory designs based on the expertise of both parties," said Dr. Wenke Weinreich, Deputy Director of Fraunhofer IPMS.

Leaders from the New York Center for Research, Economic Advancement, Technology, Engineering, and Science (NY CREATES), based in Albany, N.Y., and the Fraunhofer Institute for Photonic Microsystems IPMS, based in Dresden, Germany, formalized the JDA with a ceremonial signing by NY CREATES Vice President of Strategies, Partnerships, & New Ventures and Chief Operating Officer Paul Kelly and

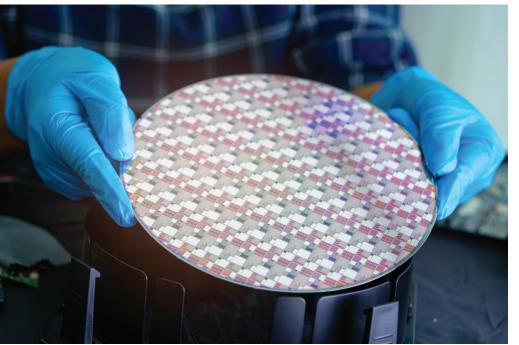

Fraunhofer IPMS Deputy Director Dr. Wenke Weinreich at NY CREATES' Albany NanoTech Complex on May 15, with a number of dignitaries from New York State and Germany in attendance. NY CREATES and Fraunhofer IPMS will embark on a joint development project for the co-development of advanced memory devices built at the 300mm wafer scale, the platform upon which chips are made.

In May of 2023, representatives from Fraunhofer IPMS met with counterparts at NY CREATES' Albany NanoTech Complex, the largest non-profit semiconductor research and development facility in North America.

There, Dr. Weinreich signed a Memorandum of Understanding between the two organizations and in the presence of Saxony's Minister President Michael Kretschmer with the aim of further advancing economic prosperity through innovation in both regions.

- Based around a hot topic for your company, this 60-minute recorded, moderated zoom roundtable would be a platform for debate and discussion

- Moderated by Editor, Phil Alsop, this can include 3 speakers

- Questions prepared and shared in advance

Cost: £5995

**Contact:** Jackie Cannon jackie.cannon@angelbc.com

### Invest Qatar partners with Ardian and Silian Partners

Plan is to foster AI and semiconductor ecosystems in Qatar and the wider region.

THE INVESTMENT PROMOTION

AGENCY QATAR (Invest Qatar), Ardian, a world-leading private investment house, and Silian Partners, a unique strategic and operational value creation firm specialised in the global semiconductor industry that has formed a strategic partnership with Ardian to launch Ardian Semiconductor, a pioneering semiconductor private equity platform, have announced a partnership to collaborate on Al and semiconductors.

This initiative will contribute to drive digital innovation and to develop strategic technologies in Qatar. Invest Qatar, Ardian and Silian Partners will work together to attract companies in the AI and semiconductor technology ecosystems to explore opportunities and establish operations in Qatar. In line with these efforts, Silian Partners will establish an office in Qatar to bring significant semiconductor industry capabilities to the country. As part of this partnership, Invest Qatar will facilitate connections between Ardian Semiconductor's portfolio companies and local stakeholders, as well as provide aftercare services for current investors.

The collaboration is poised to introduce various initiatives to support the long-term growth of the technology sector in Qatar such as joint seminars, workshops and conferences to facilitate knowledge sharing and networking. Invest Qatar will also work closely with Ardian and Silian Partners to organise exploratory fact-finding trips for related companies to learn more about Qatar's welcoming and supportive business environment and to experience the country's high quality of life.

Announced during the Qatar Economic Forum in Doha, the MoU was signed by Sheikh Ali Alwaleed Al-Thani, CEO, Invest Qatar; Jan Philipp Schmitz,

Executive Vice President, Ardian; Paul Boudre, CEO, Co-Founder & Partner, Silian Partners.

Sheikh Ali Alwaleed Al-Thani, CEO, Invest Qatar, said: "This partnership with Ardian and Silian Partners exemplifies our commitment to attracting investment in enabling clusters such as IT & Digital in line with Qatar's Third National Development Strategy. By combining Qatar's world-class digital infrastructure and significant investments in RDI with Ardian's proven and successful private equity capabilities and Silian Partner's deep semiconductor industry experience and expertise, we are paving the way to further enhance Qatar's position as a global hub for innovation and piloting new technologies."

Jan Philipp Schmitz, Executive Vice President, Ardian said: "I would like to extend my heartfelt congratulations to all parties involved in the partnership between Invest Qatar, Ardian, and Silian Partners. This collaboration marks a significant milestone in our shared commitment to fostering Al and semiconductor ecosystems in Qatar and the wider region. Ardian Semiconductor, our pioneering private equity platform, will serve as a catalyst for digital

innovation and strategic technology development in the region. We are thrilled to see Silian Partners establish an office in Qatar, which will not only bring substantial semiconductor industry expertise to the country but also create new opportunities for growth and investment. This initiative aligns perfectly with our vision to drive forward cutting-edge technologies and solidify Qatar's position as a global hub for innovation. We are eager to explore the new avenues this partnership will open and look forward to a prosperous future together."

Paul Boudre, CEO, Co-Founder & Partner, and Thomas Pebay-Peyroula, Co-Founder & Partner, Silian Partners said: "We are excited to announce that we will locate our global strategy team in Qatar. Our team in Doha will carry out high value-added semiconductor industry research and analysis, which is essential to underpin the investment strategy of the Ardian Semiconductor platform and support portfolio companies in their strategic positioning and growth. Having an on-the-ground presence will also accelerate our vision to participate in the emergence of a differentiated local semiconductor ecosystem, as well as further strengthening our long-term partnership with Qatar."

# **Connecting Semiconductors and Electronics**

WORKFORCE DEVELOPMENT

> **Global** ADVOCACY

> > Sustainability

1000+ STANDARDS

THOUGHT LEADERSHIP

#### SEMICON

**TECH**COMMUNITIES

**SEMI**UNIVERSITY

**Cyber** Security

#### About SEMI:

SEMI connects more than 2,500 member companies and 1.3 million professionals worldwide to advance the technology and business of electronics design and manufacturing. The breadth and depth of our events, programs and services help members accelerate innovation and collaboration on the toughest challenges to growth.

### Accelerating the green transition in the semiconductor industry

SEMI Europe has announced a new three-year Memorandum of Understanding (MoU) with Stockholm Environment Institute (SEI), which will serve as a knowledge partner in the green transition of the semiconductor industry.

The purpose of the MoU between SEMI Europe and SEI is to provide a framework of cooperation and understanding, and to facilitate collaboration to further shared goals and objectives linked to global challenges. These include, but are not limited to, pollution, climate change, decarbonisation, the sustainable development of the semiconductor industry, and the implementation and promotion of the European Green Deal.

"Our strategic collaboration with Stockholm Environment Institute is a key step in driving sustainability across the semiconductor value chain," said Laith Altimime, President of SEMI Europe. "By combining SEMI Europe's industry leadership with SEI's research expertise, we support the EU's goal of climate neutrality through climate action, circularity, and responsible innovation."

Areas of cooperation for the MoU

include sustainable consumption and production; sustainable business and industry transition(s), critical metals and minerals, the science-policy interface, environment and human health, circular economy, climate change and atmospheric quality, pollution, artificial intelligence, and education for sustainable development.

"The partnership with SEMI Europe, with its over 3,000 global members, has great potential to be impactful and accelerate implementation of the green transition in the electronics and semiconductor industry," said Måns Nilsson, SEI Executive Director.

SEI is an international non-profit research institute that tackles climate, environmental and sustainable development challenges. It has a diverse research agenda including air pollution, climate change, sustainable consumption, and human health. Using a range of participatory approaches,

such as citizen science, SEI helps policymakers around the world make informed decisions for a sustainable future.

#### Advancing sustainability and innovation

SEMI has released its official position paper on the revision of the European Union's REACH Regulation. The paper outlines the semiconductor industry's priorities for ensuring that the revised regulation supports sustainable manufacturing in Europe while protecting the technological resilience and competitiveness of Europe's semiconductor industry.

"Semiconductors are at the core of Europe's green and digital transition, and the REACH revision must reflect the unique role our industry plays in enabling this future," said Laith Altimime, President of SEMI Europe. "This paper highlights how a more tailored, risk-based approach to regulation can ensure continued access to critical materials, foster innovation, and uphold the EU's leadership in sustainable manufacturing."

The REACH revision proposal is expected in Q4 2025. With key regulatory decisions approaching, SEMI Europe is calling for a balanced and forward-looking framework that enables both environmental protection and technological progress.

#### Key recommendations from SEMI Europe include:

Introducing sector-specific derogations and realistic transition timelines for complex industrial sectors such as semiconductors.

- Ensuring restriction decisions are based on full risk assessments that account for real-world use and exposure, rather than hazard alone.

- Avoiding mandatory polymer registration for proprietary process chemicals already governed under existing frameworks.

- Applying substance grouping and substitution planning with greater scientific precision, especially for critical-use substances.

- Clarifying and operationalizing the essential use concept in a transparent, proportionate, and industry-relevant manner.

- Strengthening nanomaterials regulation through targeted updates to safety data sheets, testing guidelines, and integration of the revised EU definition.

The paper also highlights the importance of ensuring that the REACH revision does not conflict with strategic EU initiatives, including the European Chips Act, and calls for deeper engagement between regulators and high-technology industries in shaping effective, innovation-compatible policy. "SEMI Europe stands ready to work with EU institutions, regulators, and relevant stakeholders to ensure the REACH revision reflects both scientific evidence and the operational realities of the semiconductor sector," said Altimime. "By aligning regulatory ambition with industrial capabilities. Europe can achieve its sustainability goals while preserving long-term strategic resilience."

### Strengthening Europe's competitiveness and advancing innovation

Seeking to explore semiconductor policy measures that can strengthen Europe's industrial ecosystem, SEMI, the European Semiconductor Industry Association (ESIA), the Global Electronics Association (formerly IPC), and the European Association of Automotive Suppliers (CLEPA) have successfully held a roundtable in Brussels, bringing together representatives from the European Commission and national governments.

The 2023 European Chips Act marked an important milestone for Europe's semiconductor industry and overall industrial ecosystem, providing concrete measures to enhance competitiveness and technological capabilities. In order to build on the success of the Chips Act, the next 2028-2034 Multi-Annual Financial Framework (MFF) – the long-term budget of the European Union – must continue to deliver strategic investments to support manufacturing capabilities, research and development (R&D), supply chain resilience and access to critical raw materials.

"The creation of a new European semiconductor strategy was a focal point of the roundtable discussion, emphasizing on the increasing need to boost the technological capabilities and accelerate innovation across the European semiconductor ecosystem," said Laith Altimime, President, SEMI Europe. "We look forward to continuing our discussions with the European Commission to make sure the MFF effectively supports the semiconductor industry's pivotal role in technology advancement."

SEMI applauded the ongoing initiatives of European policymakers, together with the progress already made to bolster the European semiconductor ecosystem. Nevertheless, considering the existing concerns and challenges of industry raised during this forum, the European semiconductor ecosystem requires a holistic approach that decisively supports competitiveness while preserving supply chain resilience and security in the longer term.

SEMI will continue to engage with the relevant policymakers and stakeholders to create a policy framework that can strengthen the entire European semiconductor supply chain while preserving technological competitiveness.

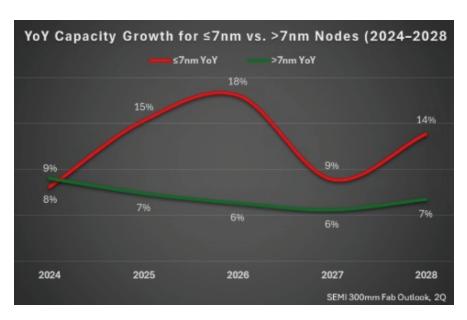

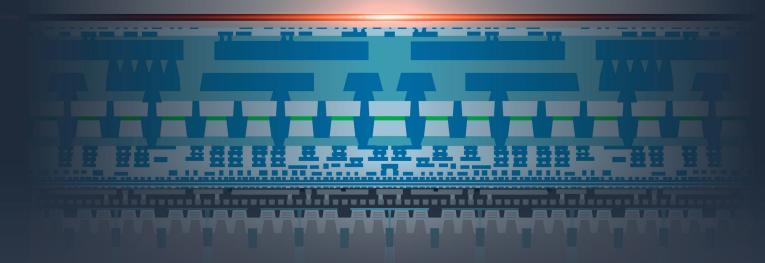

### 69% growth in advanced chipmaking capacity through 2028 due to Al

SEMI has reported findings from its latest 300mm Fab Outlook report. The report shows global frontend semiconductor suppliers are accelerating expansion efforts to support the surging demand for generative AI applications.

According to the 300mm Fab Outlook report, the global semiconductor manufacturing industry is expected to maintain strong momentum, with capacity projected to grow at a compound annual growth rate (CAGR) of 7% from the end of 2024 through 2028, reaching a record high of 11.1 million wafers per month (wpm).

A key driver of this growth is the continued expansion of advanced process capacity (7nm and below), which is expected to increase by approximately 69% – from 850,000 wpm in 2024 to a historic high of 1.4 million wpm in 2028 – representing a CAGR of around 14%, double the industry average.

"Al continues to be a transformative force in the global semiconductor industry, driving significant expansion of advanced manufacturing capacity," said SEMI President and CEO Ajit Manocha. "The rapid proliferation of Al applications is stimulating robust

#### SEMI NEWS UPDATE

investment across the semiconductor ecosystem, underscoring the industry's pivotal role in fostering technology innovation and meeting the surging demand for advanced chips."

#### Al Continues to Drive Demand for Advanced Nodes

Beyond the demand for increasingly powerful training capabilities to support larger Al model architectures, Al inference has emerged as another critical catalyst for growth. Market expansion is further fueled by Al's integration into system software for personal assistants and innovative applications.

Moreover, Al is also enabling new breakthroughs in virtual and augmented reality devices, as well as humanoid robotic sectors, which are expected to sustain strong demand for advanced semiconductor technologies over the next several years.

Advanced Process Capacity Expansion Maintains Double-Digit Growth Advanced process capacity is projected to maintain a robust 14% CAGR from 2025 through 2028, beginning with 982 thousand wpm in 2025, representing 15% YoY growth. The industry is expected to achieve a significant milestone in 2026, surpassing one million wafers for the first time, with capacity reaching 1.16 million wpm.

2nm and below capacity deployment shows even more aggressive scaling throughout the forecast period, with production capacity expanding dramatically from less than 200 thousand wpm in 2025 to over 500 thousand wpm by 2028, reflecting the strong market demand driven by Al applications in advanced manufacturing.

#### Fab Equipment in Advanced Technology Soar in 2025 and 2027

The semiconductor industry's investment landscape remains firmly anchored in advanced process technologies. Capital expenditure on advanced process equipment is forecast to surge to over US\$50 billion by 2028, representing a substantial 94% increase from the US\$26 billion invested in 2024.

This trajectory underscores the industry's resolute commitment to next-generation manufacturing capabilities, reflecting a robust 18% CAGR.

The transition to cutting-edge nodes continues to accelerate, with 2nm technology projected to reach mass production by 2026, followed by the commercial deployment of 1.4 nm technology in 2028.

In anticipation of growing market demand, chip manufacturers are strategically expanding production capacity ahead of schedule, with growth rates of 33% in 2025 and 21% in 2027, respectively.

Investment in 2nm and below wafer equipment represents a particularly dramatic expansion, with funding more than doubling from US\$19 billion in 2024 to US\$43 billion in 2028.

A remarkable 120% increase that underscores the industry's aggressive pursuit of next-generation manufacturing capabilities.

#### Dedicated webinars for the silicon semiconductor industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of Silicon Semiconductor, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 55,000 silicon semiconductor professionals.

In addition to organising and managing your webinar, we can also market your webinar to our silicon semiconductor specialist database.

In a dedicated 6-week program we will promote through our magazine, newsletters, LinkedIn group and website.We can also provide the webinar moderator, from our team of highly respected editors. Let our editors work with you and help you with the content.

#### Reach Educate Influence

Brand Awareness

online events.

- Increase global awareness by running sponsored webinars, Zoom interviews and virtual events.

- Lead Generation

Generate and mature leads through the use of

- Thought Leadership

Become the voice of knowledge by generating compelling

content via online events.

Find out how Angel Webinar can help you organise and run a webinar within the silicon semiconductor industry.

Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

### Semiconductor manufacturing equipment market: endless potential in chip making

The global semiconductor manufacturing equipment market is currently at the forefront of a major technological shift led by the rapid rise of applications like AI, 5G, IoT, automotive electronics, and advanced packaging.

SEMICONDUCTOR manufacturing equipment (SME) has now burst into the limelight, which is paving the way for the future of mobility, healthcare, energy, and defense. Governments are investing heavily in reshoring, supply chain security, and innovation. As per a report published by Research Nester, the semiconductor manufacturing equipment market is projected to reach an impressive USD 350.3 billion by 2037.

The growth is driven by the global shift towards electric and autonomous vehicles and the increasing demand for advanced, smaller node semiconductor technologies like 5 nm and 3 nm chips. As the automotive sector embraces electrification and self-driving technology, the need for high-performance semiconductors has skyrocketed. This surge has prompted substantial investments in SiC chip manufacturing facilities. At the same time, the semiconductor industry is pushing for miniaturization. This is leading to a soaring demand for ultraprecise manufacturing equipment. Further, let's dive into the trends and market dynamics shaping this vibrant industry.

#### Rise of advanced packaging

The surge in advanced packaging technologies is becoming a key player in the growth of the semiconductor manufacturing equipment market. This has increased the need for specialized equipment for precise assembly, bonding, interconnection, and inspection. Additionally, the need to manage delicate, high-density interconnects and multi-layer structures is driving the demand for

ultra-precise manufacturing systems. This trend is further fueled by the growing applications in areas like Al accelerators, 5G modules, IoT devices, and automotive electronics.

For instance, in September 2024. Tata Electronics announced a partnership with ASMPT Singapore for the development of semiconductor assembly equipment for its chip packaging units in Assam and Karnataka. This collaboration is all about R&D in areas like wire bonding, flip-chip technology, and advanced packaging. The goal of this partnership is to create a strong semiconductor assembly and testing infrastructure while prioritizing energy and material efficiency to promote sustainable growth and strengthen the semiconductor supply chain.

### Incorporation of Artificial Intelligence (AI) and Machine Learning (ML)

As the process of chip fabrication gets more intricate, manufacturers are increasingly relying on Al and ML to boost operational efficiency. One of the standout uses of Al in semiconductor manufacturing equipment is predictive maintenance. This proactive approach cuts down on unexpected downtime, prolongs the lifespan of equipment.

Moreover, Al and ML are also making waves in process optimization and defect detection. Al is revolutionizing smart automation in semiconductor fabs that boost yield and cut down on energy use. The integration of Al and ML is also transforming equipment design and functionality. Consequently, this is positioning it as a crucial factor

for long-term growth in the market. In March 2025, YES, a leading manufacturer of process equipment for Al and high-performance computing (HPC) semiconductor solutions, announced the shipment of its very first commercial VeroTherm Formic Acid Reflow tool to a prominent global semiconductor manufacturer.

This showcases the first piece of equipment made in India for cutting-edge semiconductor applications like high bandwidth memory (HBM), which is essential for Al and high-performance computing (HPC) around the globe.

#### Adoption of advanced lithography

The rise of cutting-edge lithography techniques is reshaping the semiconductor manufacturing equipment market. EUV lithography has become crucial for making these next-gen processes a reality. This transition has led to a surge in demand for highly complex, high-value lithography equipment. In February 2025, DuPont announced that showcase its latest innovations through a series of technical presentations that will highlight the development of photoresists for EUV lithography.

The introduction of High-NA EUV systems is likely to further boost capital spending among major players like Intel, TSMC, and Samsung. Recently, in June 2025, ASML, the world's sole provider of extreme ultraviolet (EUV) lithography machines, declared to move forward with its next-generation High-NA (numerical aperture) EUV systems. Furthermore, a new wave of investment in R&D,

production capacity is solidifying advanced lithography as a key player in the expansion of the market.

#### Investments in semiconductor fabrication (Fab) expansion

The recent surge in investments aimed at expanding semiconductor fab plants is playing a pivotal role in boosting the semiconductor manufacturing equipment, such as lithography systems, etching machines, deposition tools, cleaning units, and metrology devices.

Fab expansion is a fundamental shift in the global manufacturing strategy. Key players like Samsung, Intel, and GlobalFoundries are pouring billions into next-gen fabs across the U.S., Taiwan, South Korea, and Europe.

Government initiatives like the U.S. CHIPS Act, the European Chips Act are providing robust policy support, funding incentives to enhance domestic semiconductor production. This movement is resulting in a promising

growth trajectory that looks set to continue well into the next decade. Let's have a look at recent investments in semiconductor fab expansion by several regions.

- In June 2025, Texas Instruments announced a groundbreaking investment of over USD 60 billion in seven semiconductor fabs across the U.S. This marks the largest commitment to foundational semiconductor manufacturing in the nation's history. This expansion will significantly boost our manufacturing capacity to meet the rising demand for semiconductors.

- In March 2024, the Indian government gave the green light to a significant investment to feature the nation's very first cutting-edge semiconductor fabrication plant.

A whopping USD 15 billion has been allocated for these ambitious projects.

#### In a nutshell

The semiconductor manufacturing equipment market is now a vital

cornerstone of global innovation and economic stability. As various industries sprint towards digital transformation, the appetite for advanced semiconductors is skyrocketing.

The constant drive for smaller, more powerful chips, the emergence of advanced packaging and 3D integration, and the incorporation of AI and automation are expanding the semiconductor manufacturing equipment market.

Key players like Applied Materials, Lam Research, and Tokyo Electron are innovating rapidly to adapt to the shifting semiconductor landscape. At the same time, countries are pouring billions into policy initiatives to bolster domestic manufacturing capabilities. Looking ahead, the SME market will play a crucial role in driving the future of technology forward.

https://www.researchnester.com/ reports/semiconductor-manufacturingequipment-market/5058

As the process of chip fabrication gets more intricate, manufacturers are increasingly relying on AI and ML to boost operational efficiency. One of the standout uses of AI in semiconductor manufacturing equipment is predictive maintenance. This proactive approach cuts down on unexpected downtime, prolongs the lifespan of equipment

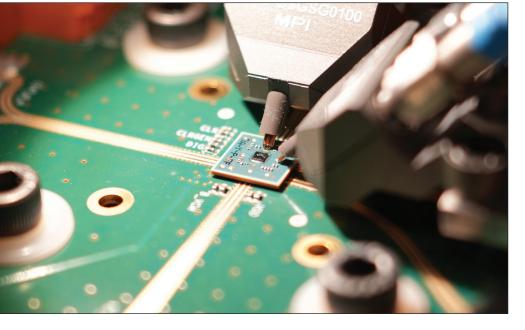

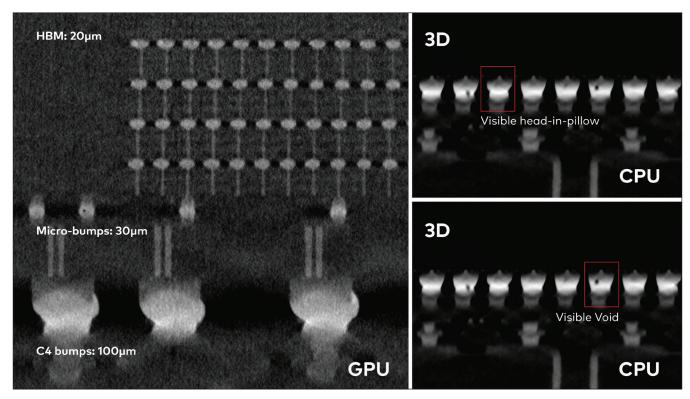

### New 3D chips could make electronics faster and more energy-efficient

The low-cost, scalable technology can seamlessly integrate high-speed gallium nitride transistors onto a standard silicon chip.

#### BY ADAM ZEWE, MIT NEWS

THE ADVANCED semiconductor material gallium nitride will likely be key for the next generation of high-speed communication systems and the power electronics needed for state-of-the-art data centers.

Unfortunately, the high cost of gallium nitride (GaN) and the specialization required to incorporate this semiconductor material into conventional electronics have limited its use in commercial applications.

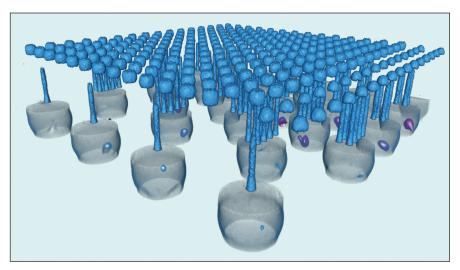

Now, researchers from MIT and elsewhere have developed a new fabrication process that integrates high-performance GaN transistors onto standard silicon CMOS chips in a way that is low-cost and scalable, and compatible with existing semiconductor foundries.

Their method involves building many tiny transistors on the surface of a GaN chip, cutting out each individual transistor, and then bonding just the necessary number of transistors onto a silicon chip using a low-temperature

process that preserves the functionality of both materials.

The cost remains minimal since only a tiny amount of GaN material is added to the chip, but the resulting device can receive a significant performance boost from compact, high-speed transistors. In addition, by separating the GaN circuit into discrete transistors that can be spread over the silicon chip, the new technology is able to reduce the temperature of the overall system.

The researchers used this process to fabricate a power amplifier, an essential component in mobile phones, that achieves higher signal strength and efficiencies than devices with silicon transistors. In a smartphone, this could improve call quality, boost wireless bandwidth, enhance connectivity, and extend battery life. Because their method fits into standard procedures, it could improve electronics that exist today as well as future technologies. Down the road, the new integration

scheme could even enable quantum applications, as GaN performs better than silicon at the cryogenic temperatures essential for many types of quantum computing. "If we can bring the cost down, improve the scalability, and, at the same time, enhance the performance of the electronic device, it is a no-brainer that we should adopt this technology. We've combined the best of what exists in silicon with the best possible gallium nitride electronics. These hybrid chips can revolutionize many commercial markets," says Pradyot Yadav, an MIT graduate student and lead author of a paper on this method.

He is joined on the paper by fellow MIT graduate students Jinchen Wang and Patrick Darmawi-Iskandar; MIT postdoc John Niroula; senior authors Ulriche L. Rodhe, a visiting scientist at the Microsystems Technology Laboratories (MTL), and Ruonan Han, an associate professor in the Department of Electrical Engineering and Computer Science (EECS) and member of MTL;

and Tomás Palacios, the Clarence J. LeBel Professor of EECS, and director of MTL; as well as collaborators at Georgia Tech and the Air Force Research Laboratory. The research was recently presented at the IEEE Radio Frequency Integrated Circuits Symposium.

#### **Swapping transistors**

Gallium nitride is the second most widely used semiconductor in the world, just after silicon, and its unique properties make it ideal for applications such as lighting, radar systems and power electronics.

The material has been around for decades and, to get access to its maximum performance, it is important for chips made of GaN to be connected to digital chips made of silicon, also called CMOS chips. To enable this, some integration methods bond GaN transistors onto a CMOS chip by soldering the connections, but this limits how small the GaN transistors can be. The tinier the transistors, the higher the frequency at which they can work. Other methods integrate an entire gallium nitride wafer on top of a silicon wafer, but using so much material is extremely costly, especially since the GaN is only needed in a few tiny transistors. The rest of the material in the GaN wafer is wasted.

"We wanted to combine the functionality of GaN with the power of digital chips made of silicon, but without having to compromise on either cost of bandwidth. We achieved that by adding super-tiny discrete gallium nitride transistors right on top of the silicon chip," Yadav explains. The new chips are the result of a multistep process.

First, a tightly packed collection of miniscule transistors is fabricated across the entire surface of a GaN wafer. Using very fine laser technology, they cut each one down to just the size of the transistor, which is 240 by 410 microns, forming what they call a dielet. (A micron is one millionth of a meter.) Each transistor is fabricated with tiny copper pillars on top, which they use to bond directly to the copper pillars on the surface of a standard silicon CMOS chip. Copper to copper bonding can be done at temperatures below 400 degrees Celsius, which is low enough to avoid damaging either material.

Current GaN integration techniques require bonds that utilize gold, an expensive material that needs much higher temperatures and stronger bonding forces than copper. Since gold can contaminate the tools used in most semiconductor foundries, it typically requires specialized facilities.

"We wanted a process that was low-cost, low-temperature, and low-force, and copper wins on all of those related to gold. At the same time, it has better conductivity," Yadav says.

#### A new tool

To enable the integration process, they created a specialized new tool that can carefully integrate the extremely tiny GaN transistor with the silicon chips. The tool uses a vacuum to hold the dielet as it moves on top of a silicon chip, zeroing in on the copper bonding interface with nanometer precision. They used advanced microscopy to monitor the interface, and then when the dielet is in the right position, they apply heat and pressure to bond the

GaN transistor to the chip. "For each step in the process, I had to find a new collaborator who knew how to do the technique that I needed, learn from them, and then integrate that into my platform. It was two years of constant learning," Yadav says.

Once the researchers had perfected the fabrication process, they demonstrated it by developing power amplifiers, which are radio frequency circuits that boost wireless signals. Their devices achieved higher bandwidth and better gain than devices made with traditional silicon transistors. Each compact chip has an area of less than half a square millimeter.

In addition, because the silicon chip they used in their demonstration is based on Intel 16 22nm FinFET state-of-the-art metallization and passive options, they were able to incorporate components often used in silicon circuits, such as neutralization capacitors. This significantly improved the gain of the amplifier, bringing it one step closer to enabling the next generation of wireless technologies.

This work is supported, in part, by the U.S. Department of Defense through the National Defense Science and Engineering Graduate (NDSEG) Fellowship Program and CHIMES, one of the seven centers in JUMP 2.0, a Semiconductor Research Corporation Program by the Department of Defense and the Defense Advanced Research Projects Agency (DARPA). Fabrication was carried out using facilities at MIT.Nano, the Air Force Research Laboratory, and Georgia Tech. Reprinted with permission of MIT News http://news.mit.edu/

### Dedicated webinars for the silicon semiconductor industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of Silicon Semiconductor, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 55,000 silicon semiconductor professionals.

Find out how Angel Webinar can help you organise and run a webinar within the silicon semiconductor industry.

Reach Educate Influence

- Brand Awareness

- Lead Generation

- Thought Leadership

Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

#### RESEARCH FOCUS | MATERIALS ENGINEERING

### Applied Materials and CEA-Leti expand joint lab to drive innovation in specialty chips

Based at CEA-Leti, collaboration focuses on materials engineering solutions to enable more energy-efficient AI Data centres.

APPLIED MATERIALS, INC. and CEA-Leti have outlined the next phase of their longstanding collaboration to accelerate innovation in specialty semiconductors. Through an expansion of their joint lab, the organizations plan to develop materials engineering solutions to address emerging infrastructure challenges in Al data centers.

The joint lab is focused on device innovations for chipmakers serving ICAPS markets (IoT, Communications, Automotive, Power and Sensors). These specialty chips are used in a wide range of applications – from industrial automation to electric vehicles – and they play a critical role managing data and power distribution within data centers. Growing resource demands in AI infrastructure have highlighted the need for a new wave of innovation in ICAPS chips to enable more energy-efficient computing.

Under the new agreement, Applied and CEA-Leti will expand the lab with new equipment and capabilities that move beyond individual process steps to include full-flow development of specialty devices. Additionally, the lab will be equipped with state-of-the-art advanced packaging tools to support heterogeneous integration of chips across different wafer types and process nodes — enabling entirely new classes of specialty devices for a range of next-generation applications.

The joint facility features several Applied Materials wafer processing systems together with CEA-Leti's world-class capabilities for evaluating performance of new materials and device validation. The upgraded lab will strengthen the chipmaking ecosystem in France by further expanding the technology hub in Grenoble, a leading site for collaborative innovation across government, academia and industry.

The lab also marks an extension of Applied's global EPIC Platform, a new high-velocity innovation model designed to accelerate commercialization of new chip technologies. Applied and CEA-Leti will be able to leverage the R&D work taking place across Applied's global

innovation centers to drive progress in specialty semiconductor technologies.

"Applied Materials and CEA-Leti have a long history of successful collaboration, and we are excited to strengthen our capabilities for accelerating innovation and commercialization of nextgeneration specialty chips," said Aninda Moitra, corporate vice president and general manager of Applied Materials' ICAPS business. "Our combined expertise will help foster breakthroughs and push the boundaries of semiconductor innovation, contributing to sustainable advancements in a range of critical applications for the AI era." Sébastian Dauvé, CEO of CEA-Leti, said the first phase of the expanded collaboration laid important groundwork for addressing materials-engineering challenges of specialty semiconductor devices.

"Building on this momentum, the joint lab's new focus on energyefficient solutions for Al data-center infrastructure reflects our shared commitment to making technological progress that meets both industrial

#### RESEARCH FOCUS | MATERIALS ENGINEERING

and societal needs. The extended partnership also leverages our complementary strengths to accelerate innovation at the system level, while supporting sustainable growth in France's semiconductor ecosystem," he said.

#### CEA-Leti and Soitec form strategic partnership

CEA-Leti and Soitec have formed a strategic partnership to enhance the cybersecurity of integrated circuits (ICs) through the innovative use of fully depleted silicon-on-insulator (FD-SOI) technologies.

This collaboration aims to position FD-SOI as a foundational platform for secure electronics by leveraging and extending its inherent resistance to physical attacks.

At the heart of the initiative is a joint effort to experimentally validate and augment the security benefits of FD-SOI—from the substrate level up to circuit design. The project aims to deliver concrete data, practical demonstrations, and roadmap guidance to meet the surging cybersecurity demands in critical markets such as automotive, industrial IoT, and secure infrastructure.

#### Combining expertise to secure the future of electronics

The partnership, which will utilize GlobalFoundries' advanced chip manufacturing capabilities, will address a growing need for trusted components in embedded and cyber-physical systems – systems that must deliver security services and withstand both software- and hardware-level attacks. With FD-SOI's proven advantages against laser fault injection (LFI) attacks due to its thin-film architecture and channel isolation, the technology presents a compelling foundation for next-generation secure IC design.

#### Key goals of the partnership include:

- Highlighting FD-SOI's existing strengths in cybersecurity.

- Co-developing innovations across the substrate-design stack to boost physical robustness and meet security requirements in automotive and other embedded systems.

- Demonstrating empirical security data to reinforce FD-SOI's credibility in certification contexts such as SESIP and Common Criteria.

Applied Materials and CEA-Leti have a long history of successful collaboration, and we are excited to strengthen our capabilities for accelerating innovation and commercialization of next-generation specialty chips

Context: Rising Threats, Rising Demand

"In an era marked by increasing attacks on connected systems and autonomous vehicles, the need for embedded hardware capable of resisting physical tampering has never been greater," said CEA-Leti CTO Jean-René Lequepeys. "FD-SOI's unique combination of performance, energy efficiency, and attack resistance offers an ideal answer for industries that demand both trust and efficiency. This project will leverage research results from the FAMES Pilot Line."

#### FD-SOI's critical benefits include:

- Physical attack resistance, enabled by electrical isolation between the channel and substrate.

- Power-performance optimization, vital for battery-constrained applications like automotive ECUs and industrial sensors.

- Security design enablement, allowing

- tailored countermeasures such as fault detection and isolation of sensitive circuit domains.

- Long-Term Vision: Toward a New Cyber-Substrate

While the initial phase focuses on leveraging existing FD-SOI capabilities, the project sets the stage for long-

term innovation. The envisioned next-generation cyber-substrate would expand upon FD-SOI's strengths by incorporating:

Enhanced protection against backside and invasive physical attacks.

Embedded anti-tamper features and physical unclonable functions (PUFs) for hardware fingerprinting.

Dynamic response mechanisms to detect and counter emerging threats. This future-oriented work will address both cyber and supply-chain vulnerabilities — making FD-SOI not only more secure, but also more indispensable.

Soitec's Senior Executive Vice President in charge of Innovation and Chief Technology Officer Christophe Maleville said: "This partnership with CEA-Leti reflects our strategic ambition to position FD-SOI as a reference platform for secure and energy-efficient electronics. By combining our substrate innovation capabilities with CEA-Leti's research excellence, we aim to demonstrate the full potential of FD-SOI in addressing today's most pressing security challenges. Together, we are paving the way for a new generation of trusted technologies that are essential to the future of connected systems."

## GENESIS Project launches to lead Europe's transition to sustainable semiconductor manufacturing

58 partners charged with implementing cutting-edge solutions for emission control, materials innovation, waste reduction and raw material reuse.

A PAN-EUROPEAN consortium dedicated to developing sustainable processes and technologies for the semiconductor-manufacturing industry has announced the launch of the GENESIS project.

This integrated, large-scale initiative aims to enable Europe's chip industry to meet its sustainability goals – from materials development to final waste treatment.

Coordinated by CEA-Leti, the threeyear project brings together 58 partners spanning the entire European semiconductor value chain, from large enterprises and SMEs to research institutes, universities, and industry associations.

GENESIS will drive innovative solutions in emission control, eco-friendly

materials such as alternatives to PFASbased ones, waste minimization, and raw material reuse, directly aligned with the European Green Deal and European Chips Act.

"GENESIS is designed to address the complex challenges of building a truly sustainable semiconductor ecosystem," said Laurent Pain, Sustainable Electronics Program director at CEA-Leti. "Its structure reflects both the urgency and the opportunity of Europe's green transition, powered by the complementary expertise and close collaboration of its partners."