VOLUME 46 ISSUE VII 2025

enabling environments where innovation thrives

# Ganymede

Performance without compromise

# BY PHIL ALSOP EDITOR

# The Semiconductor industry at a crossroads — growth, risk, and geopolitics

The semiconductor industry is surging ahead, yet it is also stumbling into risks that will define its future. In the second quarter of 2025, global foundry revenues hit a record \$41.7 billion, driven by seasonal demand and China's subsidy-fuelled consumption. TSMC's dominance has never been clearer, securing over 70% market share. At the same time, Al adoption is reshaping both chip design and manufacturing: the Al-in-semiconductor manufacturing market is forecast to grow sevenfold by 2033, while Al-powered data centres are expected to nearly double their semiconductor spend by 2030.

But behind the growth charts lies a more fragile picture. Security risks are mounting. Every semiconductor company in the S&P 500 has now disclosed Al-related vulnerabilities - ranging from intellectual property theft to prompt-driven data leaks. In a sector where a single schematic or line of code represents billions in R&D, such breaches are existential threats. Innovation is colliding with exposure. Geopolitics adds another layer of volatility. The US—China chip rivalry has hardened into a long-term structural divide.

Export controls have deprived China of leading-edge GPUs and advanced manufacturing tools, but they have also spurred domestic innovation, with SMIC, Huawei, and others doubling down on homegrown capabilities. Yole Group forecasts China could control 30% of global foundry capacity by 2030 - a shift that would rival Taiwan's dominance and reshape global dependencies.

Meanwhile, Europe, Japan, and even the UK are each attempting their own sovereignty plays. The UK's Council for Science and Technology has urged the creation of a sovereign Al chip design industry, while the US is pouring billions into workforce training through regional education nodes.

This competition isn't just about market share, it's about who controls the future of Al. Hyperscalers like Google, Amazon, and Microsoft are developing Al-specific ASICs to

reduce reliance on Nvidia, while startups push boundaries on cost and energy efficiency. Fraunhofer's collaboration with DIVE shows how sustainability and efficiency can still be achieved, cutting emissions and metrology waste in fabs. Yet even this innovation must be seen through the lens of ownership and control: who builds the fabs, who owns the IP, and who sets the guardrails for AI integration.

The semiconductor industry is now a theatre where three forces collide: explosive technological growth, escalating security vulnerabilities, and geopolitical manoeuvering. Revenue highs cannot mask the fragility of a system dependent on a few chokepoints of capacity, tools, and talent. The industry is richer than ever, but also more exposed than ever.

For your free weekly e-news roundup go to: siliconsemiconductor.net

# **COVER STORY**

Predictive maintenance in the semiconductor sector: how Edwards Vacuum is shaping the future of reliability

Predictive maintenance for vacuum pumps is no longer an experimental idea — it is a proven value driver in semiconductor fabs worldwide

#### 16 SEMICON West reaches new heights in Phoenix

Joe Stockunas, President, SEMI Americas, provides a comprehensive overview of the forthcoming SEMICON West 2025 event, held for the first time in Phoenix, Arizona

#### 20 Innovative partnership for resourceefficient wafer inspection

Fraunhofer IPMS and DIVE optimise semiconductor processes with 'cutting-edge' measurement system

# 24 Innovative approaches to scaling network-on-chip architectures

Co-integration of NoC routing channels alongside the backside power delivery network as a cost-effective scaling path

# 28 Thin film thermal metrology and its implications for electronic devices

How a new technology addresses the limitations of traditional measurement methods

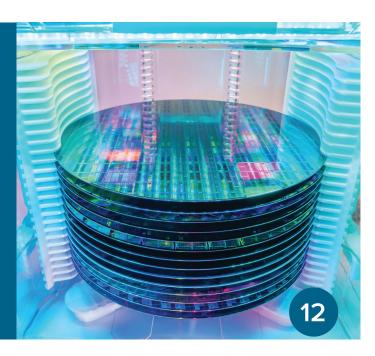

# 32 The geopolitics of the semiconductor industry: navigating a global power struggle

Nations are racing to control the semiconductor technologies that power everything from consumer gadgets to defence systems

# 36 Advanced fabs require more innovative facility services for efficiency, reliability and resiliency

Today's fabs are highly complex environments that demand precision, reliability, and real-time adaptability.

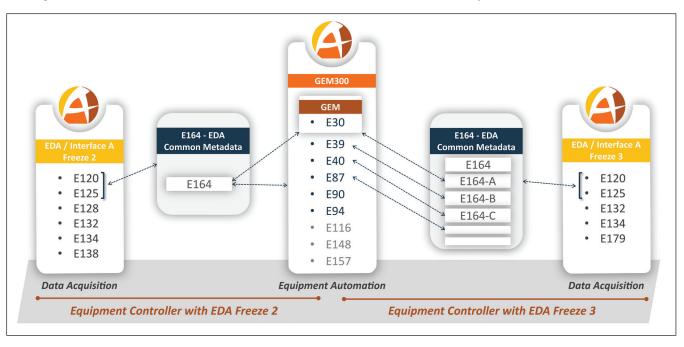

# 40 Why the global semiconductor industry needs SEMI EDA standards

By improving data throughput and seamlessly integrating with modern analytics and artificial intelligence-driven solutions

# 44 Ensuring gas purity for complex semiconductor manufacturing

As demand for chips grows, the semiconductor industry is pushing the limits of current manufacturing capabilities

# 46 Artificial intelligence in multimodal microscopy workflows for failure analysis: from 3D imaging to automated defect detection

Examining how the wealth of interconnected data will fuel the development of Al-based predictive models, capable of forecasting not only the occurrence but also the timing and underlying causes of failures from their earliest symptoms

#### 52 Building trust in GenAl for semiconductor design with IP lifecycle management

While Generative AI (GenAI) technologies are already transforming software development and have great potential to improve semiconductor design, their adoption in this industry remains hindered by the challenges around protecting highly sensitive intellectual property (IP),

#### **NEWS**

- 06 Tech, software, and semiconductor companies face the highest Al security risk in the S&P 500

- **07** Al in semiconductor manufacturing market to surpass \$14.2 billion

- **08** 2Q25 foundry revenue surges 14.6% to record high

- 09 Regional nodes to ramp up education

- **10** Data centre semiconductor trends 2025: Al reshapes compute and memory markets

Fabinary Jackie Califori Editor Phil Alsop Sales & Marketing Manager Shehzad Munshi Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor Chief Executive Officer Sukhi Bhadal

Chief Technical Officer Scott Adams

jackie.cannon@angelbc.com phil.alsop@angelbc.com shehzad.munshi@angelbc.com sharon.cowley@angelbc.com mitch.gaynor@angelbc.com sukhi.bhadal@angelbc.com +44 (0)1923 690205

+44 (0)1022 60021

+44 (0)1923 690215 +44 (0)1923 690200

+44 (0)1923 690214 +44 (0)2476 718970 +44 (0)2476 718970 Directors Jackie Cannon, Sharon Cowley

**Published by** Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK.

Silicon Semiconductor is published ten times (6x print and 4x video issues) a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00 per annum (UK), £60.00 per annum (Europe), \$90 per annum (air maili)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright versights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2025. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Silicon Semiconductor, Air Business Ltd, v/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2025.

# Tech, software, and semiconductor companies face the highest AI security risk in the S&P 500

nexos.ai highlights sector-leading exposure to IP theft, insecure AI outputs, and data leakage, and outlines practical controls to protect code and chip-design intellectual property (IP).

Al RISK is no longer just a hypothetical concern for America's largest companies. Autonomy Institute's new analysis shows that 3 out of 4 S&P 500 firms increased their Al risk disclosures this year, highlighting how deeply Al security issues are transforming corporate strategies. The technology, software, and semiconductor industries face the greatest exposure. According to Cybernews research, this sector alone has 202 documented Al security risks across 61 companies – the highest in the index.

These risks include 40 flagged cases of potential intellectual property theft, 34 insecure AI outputs, and 32 instances of data leakage. The Autonomy Institute's accompanying analysis underscores how widespread the issue is: 1 in 5 companies in the S&P 500 now list proprietary data or IP exposure as a top AI risk, and every single semiconductor company in the index updated its filings in 2025 to acknowledge significant AI threats.

Cybernews' investigation reviewed public disclosures of Al use across 327 S&P 500 companies, finding nearly 1,000 real-world Al deployments, from internal analytics tools to customerfacing chatbots, and identifying 970 potential Al security issues in total. Each case included specific examples and was categorized into risks such as prompt injection, model extraction, and accidental data exposure.

For tech and semiconductor companies, the risk isn't hypothetical. One malicious prompt can trick a model into revealing confidential code or unreleased design files. A continuous model-extraction attack can reconstruct algorithms and expose trade secrets. Cybernews warns that since these companies hold "a high concentration of proprietary algorithms and sensitive code," they

are "especially vulnerable to both data leaks and IP theft."

"Al is now a core business driver. Without the right guardrails, it carries strategic risks, especially in tech and semiconductors," says Žilvinas Girėnas, head of product at nexos.ai. "IP theft, insecure outputs, and prompt-driven leaks are no longer theoretical. The solution is proactive: policy-first design, prompt redaction at the edge, strict model access controls, and auditready logs. This is how companies can protect their most valuable asset, their innovation, while still moving fast with Al."

For technology and semiconductor companies, intellectual property isn't just valuable — it is the core of the business. A single leak of source code, chip schematics, or proprietary algorithms can wipe out years of competitive advantage.

Recent incidents demonstrate how quickly things can go wrong. At Samsung, engineers pasted confidential code into ChatGPT, and that code became part of the model's training data — leading to a corporate ban on generative Al. In 2024, an

EDA (Electronic Design Automation) software company encountered a serious exposure: internal design automation prompts, used to guide the Al-assisted design of chip layouts and verification logic, were found circulating in developer forums after being entered into an unsecured third-party Al model. In multiple semiconductor companies, misconfigured Al assistants have exposed unreleased product specifications during internal testing.

These aren't isolated mistakes. They indicate that without enforced Al policies, redaction during use, and strict model oversight, every Al query risks becoming a security breach.

"Tech companies are racing to ship Al features. That pace often skips the guardrails protecting code and designs. Centralized controls like policy, redaction, routing, and clear audit trails are the only way to keep innovation from becoming an IP liability," says Girénas.

Girenas recommends that organizations handling sensitive code, algorithms, or design files adopt: Centralized policy enforcement to block risky prompts and apply consistent output filters.

# AI in semiconductor manufacturing market to surpass \$14.2 billion

According to Research intelo's latest research, the Al in Semiconductor Manufacturing market size reached USD 1.95 billion in 2024 globally.

THE MARKET is demonstrating robust momentum, supported by a strong compound annual growth rate (CAGR) of 22.7% projected from 2025 to 2033. By the end of the forecast period in 2033, the market is expected to attain a value of USD 14.2 billion.

This substantial growth is primarily driven by the increasing adoption of artificial intelligence technologies to enhance process efficiencies, reduce defects, and optimize yield in semiconductor fabrication and assembly.

As per the latest research, the market's expansion is further fueled by the growing complexity of semiconductor devices and the need for advanced analytics to maintain competitiveness in a rapidly evolving industry landscape.

The semiconductor industry forms the foundation of the digital age, powering everything from smartphones to supercomputers. As chips grow smaller, faster, and more complex, traditional manufacturing processes face significant challenges.

Artificial Intelligence (Al) has emerged as a transformative tool, enabling smarter production, faster innovation, and enhanced efficiency in semiconductor manufacturing.

Semiconductor manufacturing involves hundreds of intricate steps, including wafer fabrication, lithography, etching, and packaging. With each new generation of chips, transistors shrink to nanoscale levels, pushing the limits of physics and precision engineering.

Al helps overcome these challenges by providing predictive insights, automating defect detection, and optimizing process efficiency.

#### Key Applications of AI in Semiconductor Manufacturing 1. Predictive Maintenance

Manufacturing equipment in semiconductor fabs is highly complex and prone to wear.

Al-powered predictive maintenance detects anomalies in machines, reducing downtime and preventing costly failures.

#### 2. Yield Optimization

Al algorithms analyze vast amounts of production data to identify defects, improve yields, and enhance product quality. This ensures minimal wastage and greater cost efficiency.

#### 3. Process Automation

From wafer inspection to testing integrated circuits, Al-driven automation reduces manual intervention and speeds up production cycles.

#### 4. Supply Chain Management

Al models forecast demand, optimize inventory, and enhance logistics efficiency, ensuring semiconductor manufacturers remain resilient in times of global shortages.

Benefits of Al Adoption in Semiconductor Manufacturing

- Higher Production Efficiency: Reduced errors and faster production cycles.

- Cost Reduction: Lower downtime, reduced scrap, and optimized resource allocation.

- Improved Quality: Enhanced defect detection and precise manufacturing.

- Innovation Acceleration: Faster design-to-manufacturing transitions.

- Sustainability: Optimized use of energy and raw materials.

Al in Wafer Fabrication and Inspection Wafer fabrication is one of the most critical steps in chip manufacturing, where even microscopic errors can impact chip performance. Al-based imaging systems enable:

- Real-time defect detection.

- Improved lithography pattern recognition.

- Accurate alignment of nanoscale structures.

These advancements help manufacturers achieve higher yields and improve the reliability of finished chips.

#### **Challenges in AI Integration**

Despite its promise, AI adoption in semiconductor manufacturing faces hurdles:

- Data Privacy Concerns: Handling proprietary design and manufacturing data.

- High Implementation Costs: Al infrastructure requires significant investment.

- Skilled Workforce Shortage:

Combining Al expertise with semiconductor domain knowledge is rare

- System Integration: Ensuring Al tools align with existing manufacturing processes.

- O Future Outlook: Al-Powered Semiconductor Ecosystem The future of semiconductor manufacturing lies in intelligent automation and adaptive processes. Al will continue to evolve with advancements in:

- Generative AI for Chip Design: Automating early-stage circuit design.

- Digital Twins of Fabs: Creating virtual replicas of manufacturing plants for simulation and optimization.

- Edge Al: Deploying smart chips that manage their own performance.

- Sustainable Manufacturing: Using Al to minimize energy and water consumption in fabs.

### 2Q25 foundry revenue surges 14.6% to record high

TrendForce's latest investigations reveal that global foundry revenue in 2Q25 reached a record US\$41.7 billion, up 14.6% QoQ, thanks to China's consumer subsidy program spurring early stocking, along with upcoming demand for new smartphones, notebooks/ PCs, and servers launching in the second half of the year. Both capacity utilization and wafer shipments improved significantly across the top ten foundries.

LOOKING ahead to 3Q25, seasonal demand for new products will drive order momentum. Advanced nodes will benefit from strong demand for flagship chips, while mature nodes will be supported by peripheral IC orders. As a result, industry-wide utilization rates are expected to rise further, supporting continued revenue growth—albeit at a more moderate pace.

The revenue performance of the top 10 foundries in the second quarter is as follows: TSMC reported outstanding performance, with major smartphone clients entering their ramp-up cycle and strong shipments of Al GPUs, notebooks, and PCs pushing wafer shipments and ASPs higher. Revenue climbed 18.5% QoQ to \$30.24 billion, lifting its market share to a record 70.2% and cementing its leadership position.

Samsung Foundry also posted solid results, benefiting from smartphone demand and the ramp-up of the Nintendo Switch 2. Shipments were weighted toward high-value advanced nodes, driving revenue up 9.2% QoQ to \$3.16 billion to give the company a 7.3% market share as it ranked second. SMIC, while still supported by U.S. tariffs and China's subsidies, struggled with lingering issues from its advanced-node production lines in the first

| Ranking         | Company         | 2Q25   | 1Q25   | QoQ   | 2Q25  | 1Q25  |

|-----------------|-----------------|--------|--------|-------|-------|-------|

| 1               | TSMC            | 30,239 | 25,517 | 18.5% | 70.2% | 67.6% |

| 2               | Samsung         | 3,159  | 2,893  | 9.2%  | 7.3%  | 7.7%  |

| 3               | SMIC            | 2,209  | 2,247  | -1.7% | 5.1%  | 6.0%  |

| 4               | UMC             | 1,903  | 1,759  | 8.2%  | 4.4%  | 4.7%  |

| 5               | GlobalFoundries | 1,688  | 1,585  | 6.5%  | 3.9%  | 4.2%  |

| 6               | Huahong Group   | 1,061  | 1,011  | 5.0%  | 2.5%  | 2.7%  |

| 7               | VIS             | 379    | 363    | 4.3%  | 0.9%  | 1.0%  |

| 8               | Tower           | 372    | 358    | 3.9%  | 0.9%  | 0.9%  |

| 9               | Nexchip         | 363    | 353    | 2.9%  | 0.8%  | 0.9%  |

| 10              | PSMC            | 345    | 327    | 5.4%  | 0.8%  | 0.9%  |

| Total of Top 10 |                 | 41,718 | 36,413 | 14.6% | 97%   | 97%   |

quarter, which led to shipment delays and lower ASPs. Its revenue slipped 1.7% QoQ to \$2.21 billion, with market share dipping slightly to 5.1%, though it retained third place.

UMC performed well, with gains in both shipments and ASPs lifting revenue by 8.2% QoQ to \$1.9 billion, securing a 4.4% market share and ranking fourth. GlobalFoundries followed closely, benefiting from new product stocking and modest ASP improvements. Its revenue increased 6.5% QoQ to \$1.69 billion, placing fifth with a 3.9% share. Shipments of Tier 2 foundries improved, supported by orders for peripheral ICs used in new products.

Amid China's consumption subsidies and the push for IC localization, HHGrace, a subsidiary of HuaHong Group, saw its capacity utilization improve in the second quarter, which drove a sequential increase in total wafer shipments. While this was partly offset by a slight decline in ASP, revenue still rose by 4.6% QoQ. Including HLMC and other affiliated businesses, HuaHong Group's consolidated revenue grew by around 5% to reach approximately \$1.06 billion, securing a 2.5% market share and holding steady at sixth place.

Vanguard reported revenue growth of 4.3% QoQ to nearly \$379 million, ranking seventh, while Tower improved utilization as clients resumed stocking for second-half launches, pushing revenue up 3.9% QoQ to \$372 million, maintaining eighth place.

Nexchip also benefited from subsidy-driven demand and higher orders for peripheral ICs, though low pricing limited upside. Its revenue grew nearly 3% QoQ to \$363 million, ranking ninth. Finally, PSMC achieved revenue of \$345 million, up 5.4% QoQ, securing tenth place.

TSMC reported outstanding performance, with major smartphone clients entering their ramp-up cycle and strong shipments of Al GPUs, notebooks, and PCs pushing wafer shipments and ASPs higher. Revenue climbed 18.5% QoQ to \$30.24 billion, lifting its market share to a record 70.2% and cementing its leadership position

### Regional nodes to ramp up education

The SEMI Foundation has launched the application process for organizations seeking to become Regional Nodes in the National Network for Microelectronics Education (NNME), a nationwide initiative funded by the U.S. National Science Foundation and supported by the U.S. Department of Commerce that aims to advance education, training, and employment pathways in the U.S. microelectronics sector.

THIS RELEASE marks the first step in the review and selection process designed to identify and support regional ecosystems that are ready to lead and scale workforce development efforts aligned with the growing talent needs of the semiconductor and microelectronics industries.

The SEMI Foundation is serving as the NNME's Coordinating Hub, which includes development, coordination, and scaling of Regional Node activities nationwide. NNME expects to support up to eight nodes, each with up to \$20 million over five years.

SEMI Foundation "We've spent years listening, collaborating, and building trust, and the NNME is where all of that work takes flight," said Shari Liss, Vice President of Global Workforce Development and Initiatives at SEMI. "In an industry that's shaping the future, investing in people isn't just important, it's everything. This is our moment to build the national workforce infrastructure our ecosystem needs, one that matches the scale of our ambitions and the promise of what we can achieve together."

NNFME"A key component of our nation's technology strategy has to be talent — specifically, ensuring our nation has a world-class workforce that is qualified and equipped to compete globally in the technology sectors we know will drive the economy of the future," said Erwin Gianchandani, NSF Assistant Director for Technology, Innovation and Partnerships. "NSF is thrilled to be investing in the National Network for Microelectronics Education, which will coordinate and expand access to workforce training opportunities for America's semiconductor industry. Together with

the private sector, NNME will bolster opportunity for all Americans and strengthen our competitive advantage in a technology sector critical to our economic future and national security."

"NNME is more than a workforce initiative — it's a national call to collaborate," said Michelle Williams, Executive Director of the SEMI Foundation. "We believe the greatest breakthroughs in microelectronics workforce development will come not from isolated efforts, but from strong, coordinated partnerships rooted in communities across the country. Through NNME, we're creating a framework where industry, education, and local leaders can work hand-in-hand to make a lasting impact."

Regional Nodes are expected to be collaborative, location-based partnerships that anchor workforce development strategies for the semiconductor industry. They will bring together employers, education providers, and community organizations to: Coordinate talent development aligned with local and national industry needs.

Expand access to training and workbased learning for all populations across a full range of job types and educational attainment levels, and Support employer engagement in the co-design of programs.

The Regional Nodes will serve as innovation hubs, building replicable models for scalable impact across the ecosystem.

Regional Nodes are expected to be collaborative, locationbased partnerships that anchor workforce development strategies for the semiconductor industry

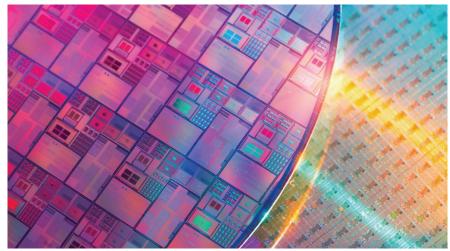

# Data centre semiconductor trends 2025: Al reshapes compute and memory markets

Yole Group publishes its new report, Data Center Semiconductor Trends 2025, offering an in-depth analysis of how AI, HPC, and hyperscaler demand are driving a new semiconductor paradigm.

THE SEMICONDUCTOR backbone of global cloud and AI infrastructure is undergoing a profound shift. Yole Group's Data Center Semiconductor Trends 2025 reveals a market at an inflection point, driven by explosive AI growth and fundamental architectural change.

In 2024, the total semiconductor TAM for data centers reached \$209 billion, spanning compute, memory, networking, and power. By 2030, that figure is projected to grow to nearly \$500 billion. Al and HPC are now the dominant use cases, with generative Al alone reshaping demand across processors and accelerators.

GPUs remain the cornerstone of Al infrastructure, with Nvidia capturing 93% of the server GPU revenue in 2024. Yole Group, the market research

& strategy consulting company, forecasts GPU revenue will grow from \$100 billion in 2024 to \$215 billion by 2030. Despite their high ASPs, GPUs are indispensable for AI training and are increasingly used in inference.

In this dynamic environment, AI ASICs are gaining momentum. Google, Amazon, and Microsoft are investing in domain-specific silicon to optimize performance and reduce dependence on Nvidia. Based on the entrance of these leading companies, AI ASIC revenue is expected to skyrocket to \$84.5 billion by 2030.

Compute is not the only bottleneck. Memory architecture is also evolving rapidly. DDR5 adoption continues. HBM is seeing exceptional demand, especially for Al training. CXL is gaining traction to solve memory disaggregation and latency challenges in new server architectures.

Leadership in data center silicon is also shifting. US players remain dominant, especially Nvidia, AMD, and Intel. But Yole Group's analysts point out that China is scaling up its domestic capabilities through strategic investment and policy. Export controls continue to impact supply chains but also reinforce sovereign development goals in China and beyond.

Startups and newcomers are also part of the game and shaping the market. From Groq to Cerebras and Tenstorrent, innovation in chip design is pushing the frontier of what Al inference hardware can do. Sometimes, novel solutions challenge established players on cost, performance, or energy efficiency.

# IR LayerRelease™ Technology

- Replacement for mechanical debonding thanks to through-silicon IR laser

- Enabling ultra-thin film or layer transfer from silicon carriers

- Nanometer-precision release of bonded, deposited or grown layers

- Front-end compatibility through silicon carriers and inorganic release materials

- Supporting future roadmaps in advanced packaging and transistor scaling

# Predictive maintenance in the semiconductor sector: how Edwards Vacuum is shaping the future of reliability

Predictive maintenance for vacuum pumps is no longer an experimental idea — it is a proven value driver in semiconductor fabs worldwide. By marrying decades of vacuum science expertise with cutting-edge data science and Al, Edwards Vacuum has built a leadership position in this critical domain.

SEMICONDUCTOR manufacturing is an unforgiving business. The complexity of the processes, the astronomical value of wafers, and the constant pressure to drive down cost while scaling up performance mean that every piece of equipment in a fab must operate with absolute precision. Among these critical systems are vacuum pumps, the oftenoverlooked workhorses that underpin etch, deposition, and other fundamental processes.

When a vacuum pump fails unexpectedly, the consequences can be catastrophic. A single wafer can be worth tens of thousands of dollars; in batch processes, an entire lot could represent millions in scrapped product. In an industry where margins are thin and throughput is paramount, the ability

to predict and prevent vacuum pump failures is no longer a nice-to-have — it is a strategic necessity.

This is where predictive maintenance comes in. While preventive maintenance schedules have long been a feature of fabs, the ability to forecast failures before they happen, based on real data rather than arbitrary calendars, has transformed expectations. And at the forefront of this transformation is Edwards Vacuum, a global leader in vacuum and abatement solutions for semiconductor manufacturing.

This article explores the evolution of predictive maintenance in the semiconductor sector — from pre-Al roots to the latest machine learning and digital twin models — and examines

how Edwards Vacuum is deploying data science, domain expertise, and IoT technology to deliver game-changing value to its customers.

### From preventive to predictive - an historical perspective

Before the rise of Al and machine learning, predictive maintenance largely relied on rules-based approaches. Engineers would monitor key parameters — vibration, temperature, power draw, exhaust composition — and set thresholds for when interventions should occur. Using decision trees and other statistical models, these early predictive maintrenance systems achieved respectable accuracy, often outperforming time-based schedules.

The foundations of machine learning were laid decades ago, but it is only in the last 15 years that computing power has caught up with the theory. Edwards and other advanced manufacturers were already experimenting with digital twins and rule-based models well before Al became a buzzword.

On vacuum abatement equipment, these models proved particularly effective; for dry pumps, accuracy was more challenging but still offered tangible benefits compared to rigid maintenance calendars.

The real game-changer, however, came when better data capture and higher-quality sensor inputs met the rise of advanced machine learning. By investing heavily in data acquisition infrastructure, Edwards set the stage for a step change in predictive accuracy. With high-resolution timeseries data streaming from pumps, machine learning models could spot subtle signatures that precede failure — signatures invisible to rules-based systems.

### The cost of failure - why prediction matters

In semiconductor fabs, two basic maintenance strategies historically dominated:

- Run-to-fail Pumps and abatement are operated until they break. This is common in single-wafer processes where the loss of one wafer is painful but manageable.

- Scheduled replacement Pumps and abatement are swapped at conservative intervals to prevent catastrophic failures during batch processing, where dozens or even hundreds of wafers are at stake.

Both strategies carry heavy costs. In run-to-fail scenarios, every failure risks unplanned downtime and lost product. In scheduled replacement regimes, pumps are often serviced or replaced long before their useful life is exhausted. Edwards engineers routinely find pumps that are "clean as a whistle" internally, removed only because the schedule said it was time.

Predictive maintenance provides a third path: run-to-predict. Instead of guessing, fabs can use real data to make informed decisions. Vacuum systems can be operated closer to their true limits without crossing them, minimizing both scrap risk and unnecessary replacements. The Edwards approach is tailored.

### Tailored models for specific failure modes

A key insight from Edwards' work is that not all pump failures are created equal. Vacuum pumps in semiconductor fabs are exposed to hostile environments - corrosive gases, deposition byproducts, and extreme duty cycles.

Different processes lead to different degradation mechanisms. For example, corrosion occurs gradually as corrosive gases attack pump internals. These are relatively easy to detect, as degradation trends are slow and steady. In contrast, when it comes to deposition byproducts accumulating inside the pump, leading to blockages or seizure, these failures are more abrupt and therefore harder to predict.

Rather than attempting a "one size fits all" predictive model, Edwards builds specific models for each failure mode and pump family, tuning them to the customer's process conditions.

remarkable results, with prediction accuracies north of 95% for corrosive processes and 70-90% accuracy for depositive processes, depending on the customer and the specific process. These accuracies are 30 -40% higher than attempts to use generic models. The lesson is clear - domain expertise and failure-mode specificity matter just as much as raw machine learning power.

### The data advantage – needles and haystacks

Machine learning thrives on data — but without domain knowledge, models can mistake noise for signal. Edwards' advantage lies not only in the sheer volume of pump performance data it has accumulated over decades, but in its deep vacuum science expertise. Building predictive models is a little like looking for a needle in a haystack. Al can sift the hay faster, but Edwards knows what a needle looks like. By combining physics-based insights with statistical analysis, this avoids false positives and delivers actionable intelligence.

This fusion of human expertise and algorithmic insight is what makes Edwards' predictive maintenance solutions robust in real-world fabs.

#### Dollars and downtime

Ultimately, fabs care about total cost of ownership (TCO) and yield protection. Predictive maintenance delivers on both fronts.

While Edwards guards its proprietary ROI calculators, the company can quantify benefits for each customer by analyzing historical pump failures, wafer scrap events, and unplanned maintenance. For many fabs, the savings run into hundreds of thousands of dollars per year, by moving breakdown maintenance to corrective maintenance.

But the benefits extend beyond customer savings. Predictive insights

#### COVER STORY | EDWARDS VACUUM

allow Edwards itself to optimize its service network. For example, if the company can forecast a quantity of potential pump failures across a region weeks in advance, it can stock the right spare parts, schedule the right number of technicians, and streamline logistics. This not only reduces Edwards' operating costs but ensures faster, smoother service for customers.

### Beyond prediction - optimization and self-tuning

Predictive maintenance is not just about avoiding failure; it also opens the door to optimizing vacuum system performance.

By analyzing operational data, Edwards' teams often discover simple configuration tweaks — for example, adjusting pump temperature by a few degrees — that dramatically reduce failure risk. These insights, delivered as part of Edwards' service packages, represent an additional layer of value beyond prediction.

Looking ahead, Edwards envisions a future where pumps may be able to reconfigure themselves autonomously in response to changing process conditions. While industry conservatism and safety concerns make this a longer-term goal, the trajectory is clear: predictive maintenance is evolving into prescriptive maintenance, and

eventually toward self-optimizing equipment.

### Building and deploying the models

Edwards' predictive maintenance models are structured around standard models for pump families and failure modes and customer-specific tuning, enabled by a sophisticated simulation environment.

By replaying years of pump data in a matter of hours, Edwards can test and refine models before deploying them live. This rapid iteration allows them to demonstrate predicted hit rates with confidence and customize solutions without prolonged trial-and-error on the fab floor.

Deployment is flexible. Edwards' data platform is designed cloud-first, offering scalability, real-time monitoring, and fleet-level visibility. For customers wary of the cloud, edge deployments are possible — either on-site or within the customer's own private cloud.

Alerts and decision-making can be handled by Edwards' service teams, integrated into fab management systems, or both. The flexibility reflects a key principle, that customers choose the level of autonomy they want, while Edwards protects the proprietary core of its models.

### Next-generation pumps - Ganymede and IoT in action

Edwards' upcoming Ganymede platform exemplifies the convergence of predictive maintenance and IoT. Unlike previous pumps, where the control and communication functions were bundled on a single microcontroller, Ganymede introduces a dedicated gateway controller with substantial compute power.

This allows predictive models to run directly on the pump itself, reducing latency and dependency on external systems. Data still flows into EdCentra for fleet-level oversight, but the pump becomes more autonomous, embodying the long-promised vision of industrial IoT. The IoT hype cycle has passed through its 'trough of disillusionment', what remains is a mature, pragmatic use of connected devices — and Ganymede is poised to be a flagship example.

#### The role of digital twins

Digital twins — virtual replicas of physical systems — are another Al frontier for Edwards. The company's service centre teams are already using twins of maintenance facilities to simulate pump flows and optimize operations.

For predictive analytics, the challenge is tougher: accurately modelling the physics of a vacuum pump in real time is enormously complex. Edwards is tackling this incrementally, starting with subsystems like cooling circuits. The long-term goal is to combine physics-based twins with machine learning models, yielding hybrid approaches that are both interpretable and accurate. Full pump digital twins may be several years away, but the trajectory is set twins will complement AI by embedding physical causality into predictive systems.

#### Toward deeper fab integration

One exciting prospect is integrating pump data with process tool data. In theory, knowing process gas flow rates or chamber conditions could make predictive models even more accurate. In practice, fabs are fiercely protective of recipe data, and OEMs guard their equipment telemetry closely.

This is a longstanding cultural barrier, rooted in the semiconductor industry's

history of secrecy and 'paranoia'. Yet there are signs of progress. Edwards can already show how combining pump and abatement system data — both under its umbrella — improves prediction accuracy. Extending this logic to fab-level integration may be inevitable, especially under the combined pressures of sustainability, yield, and cost efficiency.

The challenge will be coordinating collaboration across OEMs, fabs, and suppliers while maintaining confidentiality. Initiatives like SEMI standards and third-party data platforms may provide the neutral ground needed.

### Overcoming human and cultural barriers

Predictive maintenance is as much a people challenge as a technical one. Operators with decades of experience often pride themselves on their "gut feel" for when equipment is failing. Far from displacing this expertise, Edwards' models often validate it, providing data-driven confirmation. Resistance does exist, but results speak louder than scepticism. Once engineers see higher uptime and fewer scrapped wafers, they tend to embrace the technology.

At a broader level, the semiconductor industry's caution toward cloud adoption remains a barrier. Concerns about data leaving the fab walls are deeply ingrained. Yet as Edwards points out, the very IT security technologies developed by the semiconductor

industry underpin the safety of cloud systems used in banking, pharma, and other critical sectors.

For Edwards, the vision is clear - a 'control room' model (similar to the Rolls-Royce aerospace approach), where specialists monitor pump performance worldwide in real time and proactively guide maintenance. Achieving this requires industry-wide comfort with cloud-based data sharing — a cultural shift that is gradually unfolding.

#### The road ahead

Edwards' predictive maintenance journey is still evolving. The near-term roadmap includes:

- Wider deployment of cloud-first data platform.

- Rollout of Ganymede pumps with onboard predictive capability.

- Continued progress on digital twins for subsystems.

- Exploration of deeper fab integration under secure data-sharing frameworks.

- Leveraging predictive insights for Edwards' own service network optimization.

Longer-term, the possibilities include autonomous self-tuning pumps, Aldriven operational efficiency across regions, and hybrid models combining machine learning with digital twins. In every case, the goal is the same: to reduce downtime, extend pump lifetimes, and protect yield in one of the most unforgiving industrial environments that exists.

#### Conclusion

Predictive maintenance for vacuum pumps is no longer an experimental idea — it is a proven value driver in semiconductor fabs worldwide. By marrying decades of vacuum science expertise with cutting-edge data science, Edwards Vacuum has built a leadership position in this critical domain.

From tailored failure-mode models to IoT-enabled next-generation pumps, from service-centre digital twins to visions of real-time global monitoring, Edwards is demonstrating how predictive maintenance is evolving into a broader paradigm of predictive operations.

In the relentless pursuit of yield, uptime, and efficiency, predictive maintenance is not just about pumps — it is about the future of semiconductor manufacturing itself. And Edwards is helping to write that future, one (Al-enabled) pump at a time

### **SEMICON** West reaches new heights in Phoenix

A comprehensive overview of the forthcoming SEMICON West 2025 event, held for the first time in Phoenix, Arizona. The show floor has grown from 1,100 exhibitors in 2024 to more than1,500 this year, and the packed conference programme boasts just under 600 presentations covering the sector's current challenges and opportunities, including AI and quantum computing, cybersecurity, the skills shortage, sustainability, supply chain, heterogeneous integration, and more.

#### SILICON SEMICONDUCTOR INTERVIEW WITH JOE STOCKUNAS, PRESIDENT, SEMI AMERICAS

SIS: The obvious place to start is that we have a brand new venue for SEMICON West - Phoenix, Arizona. How much was the decision influenced by the fact that Arizona is a big semiconductor ecosystem and growing. Why Phoenix?

JS: I made the decision shortly after coming into this role in 2022, and things were really just getting started in Arizona, but it certainly turned out to be a very good decision as a result of

Arizona being successful in attracting over \$200 billion worth of investment. Now, an awful lot of that's just with TSMC, but there's plenty more. I've been to countless ribbon cuttings in the Phoenix area over the last few years and I've got three during SEMICON week. So, it really has worked out very well. The decision goes back to the fact that I feel very strongly about hosting SEMICONs where there's a semiconductor community. I wanted to do something a little bit different.

I looked at where that community exists. We looked at San Jose, Portland, Austin and, of course, Phoenix. The Phoenix Convention Centre really was the one that was most attractive because it was large enough to handle our growth. That's worked out very well. We sold out the show floor. We've never done this before. We sold out the show floor almost a year in advance. The show's in October this year. By the end of last November, we were completely sold out on the show floor. We kept taking waitlist requests from companies. In March, we had 280 companies on the waitlist. I looked at this and said, we've got to do something, I don't want to turn away 280 companies. The main show floor is similar to Moscone in San Francisco, one level below street level. Adjacent to where the keynote stage will be, that auditorium is where we will have additional exhibition space. We've opened that up, and we sold that out now as well. Last year, we had just over 1,000 booths at Moscone. And as of yesterday, we were at 1,535 booths. We've got a 50% increase in exhibitors this year, and we've got a great exhibition.

And content at the show will be fabulous. We'll actually have four days of content. The exhibition will only be open Tuesday, Wednesday, Thursday. But Monday afternoon, we've got our Market Symposium, and that is very

attractive to many. We get a huge crowd for that. During this session, SEMI's own analyst along with others that we collaborate with through the year will provide different perspectives on what to expect in the semiconductor market. Overall, right now, we have 567 speakers lined up in those four days across 63 different content sessions. Again, last year, I think we had about 450. We're up nicely on the number of speakers.

SIS: I was going to ask if you could point out what you think might distinguish the new location from the traditional home in San Francisco. You've already partly answered it because clearly the show is going to be bigger. Is there anything else you think that's going to distinguish it being in Phoenix as opposed to San Francisco?

JS: It's really interesting just how many companies are involved in semiconductors in Phoenix. There's a very large number of big companies like Intel and TSMC, certainly. But there's an awful lot of infrastructure in the industry based there as well. A number of our equipment and materials suppliers have located their headquarters in the area and have been there for a long time.

Companies like ASM and EV Group and a company I used to work for. I ran the electronics materials business at Air Products. Now, that division was sold off to Merck KGaA, Darmstadt, Germany and goes by EMD Electronics in the US. And again, they've got their headquarters for US now in Phoenix as well. So, a really great opportunity.

And what I think will be different is, I'll be honest, I'm a little jealous of my peers in Asia, the shows in Asia are just unbelievable. We had 180,000 people in China in March at SEMICON China in three days, and Japan broke 100,000 people. And the difference is in Korea, Samsung and SK hynix combined bus 17,000 employees to come to SEMICON Korea. And that's the difference for us in Phoenix this year - we've got those operating companies, the fabs, the equipment suppliers, material suppliers, the rest of the infrastructure that makes up semiconductor.

People are going to come and kick the tires this year. It'll be a great show. Again, being in Phoenix, I'm expecting that our crowd will increase. Last year, we had about 25,000 people, I think maybe 27,000. But this year, I'm very confident that we'll be over 35,000 and probably closer to 40,000 people this year. Being in Phoenix, where that infrastructure is established and people go to work every day in semiconductors, will bring more people into the convention centre, and we're really excited about that. It'll have a real buzz. Since the CHIPS Act, our shows had a real buzz. The show floors are crowded. There's a lot of folks there. This year, I think it'll even be bigger and better with us being in Phoenix where so much is going on.

SIS: You referenced some of the shows in Asia. Do you still view SEMICON West as very much a global event, bringing people from around the world to come and discuss some of the industry challenges and obviously the momentum? I still think the \$1 trillion mantra is somewhere out there, isn't it? But do you think you're going to get that global audience and this forum to discuss what's needed?

JS: I think you asked me three questions there!

So, your first question, the global show. SEMICON West was the original show, the first SEMICON we ever had, and that was in 1970 and back in Silicon Valley. And SEMI is headquartered in the US. The view of West is it's both the Americas show, so SEMICON for the Americas business, but it's also the headquarters show as well. As a result, it has always been very well-attended. We don't have the numbers that China has, but all the movers and shakers

are at SEMICON West, and that will continue.

We do a really good job of tackling the issues that are facing our industry. That is very key to it. We are very much on the path to \$1 trillion. To give you some feel for that, the semiconductor sales revenue, that's \$1 trillion in global semiconductor sales. Last year, we finished the year at \$619 billion and we're seeing very significant growth this year, maybe to \$720 billion.

We had double-digit growth, high over 20% last year. And this year, most of the market analysts are projecting at least 15%. We're well on track to \$1 trillion. That was your second question. And that's really exciting for us. It is a good time to be in semiconductors. And your third question, I think it was, will we tackle the issues? And as I said, we very much tackle the issues at this event. We've got a great keynote schedule. We'll have keynotes Tuesday, Wednesday, and Thursday morning.

Last year, we just did all day Tuesday and all day Wednesday. And what I did was I focused on the Americas

#### INTERVIEW | SEMICON WEST

issues on Tuesday, which was really the growth in America. It was really celebrating how much investment was happening in the US. Then on Wednesday, we took a look at the global opportunities and issues and split it up that way. My only regret was, if you go later in the day like we did, you're competing with the show floor. I had wonderful speakers in the afternoon, and my only complaint was they deserved a bigger audience.

This year, I'm limiting it. The show floor doesn't open until 10:00 a.m., and we'll be finished with the keynotes on Tuesday and Thursday at 10:30 a.m. And on Wednesday, we're going a little bit longer till 11:30 a.m. And the reason is on Wednesday, it will be Al day. We will start off with NVIDIA, and we will have all presentations focusing on how Al impacts and creates opportunity for the semiconductor industry. We've got great presentations on Al.

We'll go a little bit longer. But for the most part, I don't want to see us competing with the show floor. Again, we will be tackling all the opportunities and issues, which today, great growth opportunities, driven principally by Al, but then the other markets that we're very excited about, automotive, manufacturing, industry 4.0, 5.0, as you see it, MedTech, the continued demand for communications and computing capability, and the advancement into quantum computing in the future. All those opportunities will be covered in great detail, both with the keynote presentations and the other 62 sessions that provide the over 560 speakers I mentioned earlier.

We'll also have a lot to talk about on talent. Our industry is very much self-governing right now in wanting to make these investments and do them the right way and be environmentally sensitive with it. Growing issues with cybersecurity. Cybersecurity has really been the new issue that we're putting more effort into. So, it is very much the headquarters show, and we will cover all the opportunities and issues that are present for the industry today and for the next five years as we move forward on that path to \$1 trillion.

**SIS:** That's answered a couple of my next questions. You're ahead of me there. I know that the main theme is, 'Stronger together', which is, I guess, looking at the cross-industry collaboration. I'm just interested how far you think that can go because I've talked to a couple of people, you referenced AI, and clearly a large part of that is the data. I know traditionally. semiconductor companies are reluctant to share data for obvious reasons. But if the full potential of AI is going to be realised, they maybe will have to do something around that. Just your thoughts, I suppose, as to how far collaboration needs to go in the industry?

JS: I think we've really seen changes in collaboration. The SEMI supply chain initiative is very much led and engaged by us, but we've had Intel and TSMC partnering with us from day one in establishing that supply chain initiative. I've worked in the industry for 40 years and it was very difficult to get data, very difficult to get forecasts, even more

difficult to get accurate forecasts. Then we have chip shortages, and that's recognised now. I do think there's a whole lot more collaboration in general.

I can point to that, but I'll also point to when you talk about the technology demands now, it's a number of entities working together. It's certainly the tradition of the device manufacturers, the equipment manufacturers, and the material suppliers, and others. Now, again, design companies are coming into it as well in that, to make the most advanced chips, no one's doing it alone today. And that collaboration is recognised. A number of the large companies are speaking openly about this, I've actually heard one of them talk about the fact that 'we recognise we have to collaborate with our competitors now'.

I worked in the chemical/semiconductor industry for many years. And in the chemical industry, it's a common practise. In some cases, we have a relationship where we're competitors, in others, we're suppliers, in others, we're buying from each other. I think that's coming to fruition now in the semiconductor industry as well, principally driven by the needs for a reliable and resilient supply chain, and then also the demands of the technology going forward.

SIS: In terms of a quick overview of what's going on, you've mentioned the CEO Summit, but I think there are executive panels, workforce development. I think the SEMI University is there, and there are lots of technology sessions, and then there's the show floor. I've probably asked you about three questions in one, but can you give us a flavour of content, both in terms of the speakers, the conferences, and then what people can see on the show floor?

JS: As I mentioned a little bit earlier, the CEO Summit will be Tuesday, Wednesday, and Thursday. I've got anchor presentations on Tuesday. We'll start off with the Governor of Arizona, and we'll end up with TSMC. And in between, there's another three or four presentations that are equally powerful. On Wednesday, it's AI, and we start off with an NVIDIA presentation.

I'm hoping they bring the dog! It's a programme around AI and robotics and

tied to semiconductor opportunities for AI, but I'm really hoping they bring the dog - I hope at least some videos! And then the last session will be very interesting. Our friends from Merck KGaA, Darmstadt, Germany are actually bringing the global people officer and head of strategy in the US, and they're going to do a presentation on how they see Al impacting their workforce, how they'll gain advantages, where their concerns lie. And then on Thursday morning, we've invited Department of Commerce to speak. We've invited Intel to speak about their foundry business and where that's going.

And then we finish up with a presentation on cybersecurity. And that presentation will be by Keith Krach. Keith was the CEO of DocuSign, so very well-versed in security. And he also served in a previous administration in the Department of State, so very much a global view as well. And again, one of our biggest challenges now is protecting our data in this big data Al world that we're all in.

I walked away from SEMICON West last year and looked at what were my big takeaways? The number one on my list was my last position in industry, I worked in back-end packaging and test equipment. I had seven different product lines for test and high-speed dispense for packaging applications. For the last 10 years, I've been working on advanced packaging, and advanced packaging was the future. I walked away from the show last year, and my view was that the future is now for advanced packaging. We will have an awful lot more content, and that's very prevalent today, as you see all the things that are being discussed on the packaging that's used for the most advanced chips, the stacking, the memory. You will see a whole lot more content in our agenda that focuses on advanced packaging, heterogeneous integration.

In terms of workforce development, we're really proud at SEMI to have been selected to operate the National Network for Microelectronics Education, and we'll look to shepherd the implementation of a national programme. You'll see and hear a whole lot of what's going on in workforce development with SEMI in the US and globally, during the presentations and also on the show floor where we'll have

a workforce development pavilion. Over the last few years, there's been a real buzz in the show. We've had wonderful attendance, we've had a large number of speakers, great content and great exhibit show floor.

This year, the thing I'm trying to bring to it is a bit more recognition and celebration. On Monday evening, we will have our first ever gala. It's called the Legends and Leaders Honors event, where we will recognise Lisa Su, the CEO of AMD, as our first award recipient for the SEMI Silicon Medal. First time we've ever done that so it will be a big time celebration on Monday evening. On Tuesday evening, we will have a street fair. We've got a country western band, and we've got a bunch of new activities on Third Street, which separates the two buildings in the Convention Centre, and we're going to have fun on Tuesday night.

We're not going to compete with many of our large customers at SEMI who host hospitality from 5:30 p.m. to 8:00 p.m. So, from 8:30 p.m. till about 11: 00 p.m., we're going to have this street fair, and it'll be fun folks.

Additionally, during the CEO Summit, each day we'll have at least two presentations recognising technology advancement. We have a 20 Under 30 recognition where we recognise 20 people under 30 years of age. We'll present the SEMI Catalyst Award to one of the global companies that's been in Phoenix for a long time and still today is providing enabling technology for the advancement of our industry. We'll have a host of different presentations where we're recognising people on stage as

SIS: In closing, I guess it'd be good to understand if there was one thing you

wanted people to take away, that might be difficult, so it might be two or three things, but what you want them to go away with, and then, in my tradition of asking you at least two questions in one, for people who are attending for the first time, would you have any advice? You've given us the numbers. They can't, I expect, get round all 1,500 stands or listen to all of the presentations. Any tips as to how best to get stuck into SEMICON West?

JS: First thing is, visit our website, www. semiconwest.org. You need to visit our website, first of all to register for the event. Our agenda is organised in many different ways. You can see the full agenda and decide what presentations you must hear. The show floor map is there. You can search on specifically what exhibitors you might want to see when you go to visit. You can see where the social happenings are occurring all on that same website.

Overall, what I'd like to leave everyone with is we're clearly on the path to \$1 trillion, but it's not going to come to you. It's a very competitive world right now. If you want a part of that \$1 trillion, come to SEMICON West, have a plan. There's tremendous opportunities for you to network, develop business contacts, figure out where you can most advance your opportunities in the semiconductor world. It's a very exciting world right now. It's happening all over the... well, not quite all over the world, but we've got eight SEMICONs and pretty much wherever there's a SEMICON, there's a lot of activity right now in the semiconductor world. Come to SEMICON, make the contacts, do the networking, and come ready with a plan so you can maximise your opportunities in three days.

www.semiconwest.org

# Innovative partnership for resource-efficient wafer inspection

Fraunhofer IPMS and DIVE optimise semiconductor processes with 'cutting-edge' measurement system.

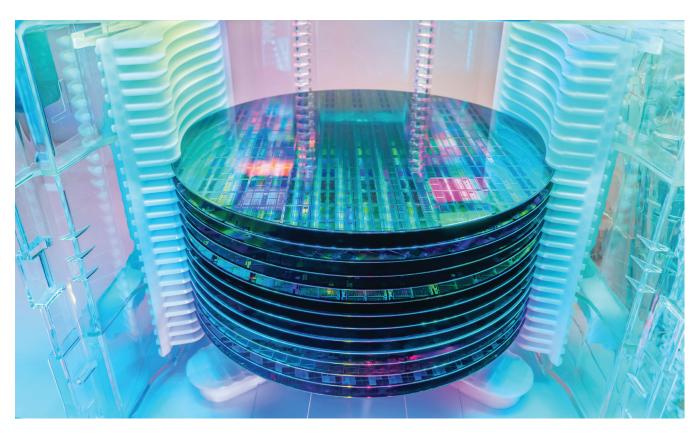

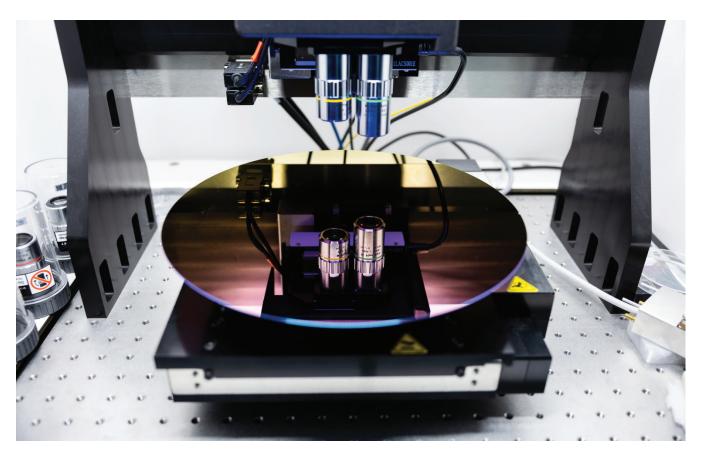

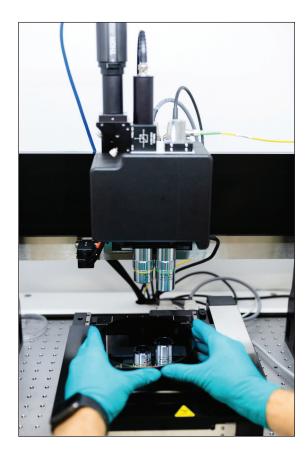

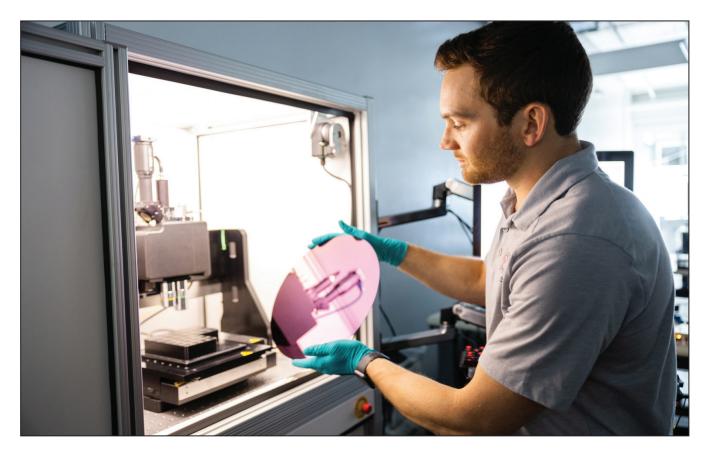

THE FRAUNHOFER INSTITUTE for Photonic Microsystems IPMS, in collaboration with DIVE imaging systems GmbH, has achieved a major milestone in resource-efficient semiconductor manufacturing. With the successful installation of an optical measurement system by DIVE in the cleanroom of Fraunhofer IPMS, the effort required for quality control during wafer production has been significantly reduced. This collaboration paves the way for a more sustainable and efficient semiconductor production process.

Semiconductor manufacturing involves up to 1,500 process steps, including etching, deposition and lithography.

Due to their complexity of structures, finished wafers must be nearly defect-free, which requires rigorous quality control. As a result, up to 50% of process steps are dedicated to metrology and thousands of additional control wafers are produced each month. This requires substantial additional financial and material expenditures as well as energy and time resources.

The project "NEST" (New Screening Tool for Efficient Semiconductor Manufacturing) directly addresses this issue. Over the past 1.5 years, DIVE, together with Fraunhofer IPMS and Fraunhofer IZM has conducted an environmental potential analysis. The study revealed that targeted inspection tools could reduce control wafer usage by at least 25%, while also saving more than 118,000 kilograms of CO<sub>2</sub> emissions during production every month.

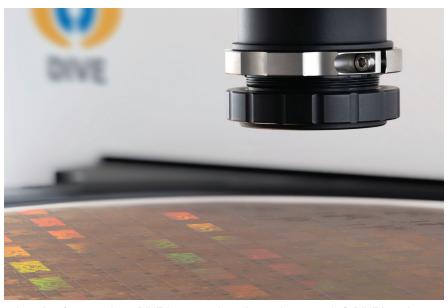

DIVE's solution uses an innovative combination of spectroscopy and imaging technologies capable of identifying defects even in deeper wafer layers. The analysis was based on a 28 nm manufacturing process and 25,000 wafer starts per month. The project was funded within the "Green ICT Space" by the Research Fab Microelectronics Germany (FMD).

In addition to CO<sub>2</sub> savings, the system offers further ecological benefits, such as the reduction of water and chemicals used in control wafer production.

Furthermore, the reduction of metrology steps also improves energy efficiency by freeing up tool capacity; an early detection of process deviations avoids misproduction and improves the overall productive wafer yield, which results in an economic advantage as well.

#### Industry-ready evaluation in cleanroom Environment at Fraunhofer IPMS

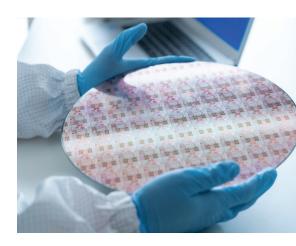

DIVE imaging systems GmbH develops advanced inspection tools that combine the benefits of optical spectroscopy with imaging. The DIVE VEpioneer® is the first of its kind to operate under cleanroom conditions.

It rapidly assesses surface properties, contamination and deviations from

> Quality inspection in the wafer manufacturing process. © Fraunhofer IPMS

production specifications in just 20 seconds. The integration of Al algorithms enables comprehensive process control while significantly reducing testing efforts. "DIVE's hyperspectral imaging systems offer a new way of non-destructive wafer inspection. With the support of Fraunhofer IPMS, this innovative technology is now available for use in standardized industrial cleanrooms — enabling significant productivity gains and cost savings for semiconductor fabs," says Martin Landgraf, R&D Manager at Fraunhofer IPMS.

After the successful conclusion of the project, the DIVE VEpioneer® system will remain at Fraunhofer IPMS's Center Nanoelectronic Technologies (CNT) for continued wafer measurement and evaluation for customers and partners. Further joint projects are planned to enhance the system with wafer handling automation and equipment integration for an automatic data transfer. With the acquisition of DIVE imaging systems GmbH by PVA TePla AG, the start-up now gains new opportunities for evaluation and development – particularly through the expertise of the material and metrology specialist.

### Pure water for sustainable semiconductor production

AlixLabs and NSS Water are pleased to announce a strategic collaboration to develop sustainable and cost-effective ultrapure water (UPW) management solutions for chip production. Amid rising concerns over the semiconductor industry's ever-increasing water consumption the two Swedish companies will team up to address this challenge.

The project value is approximately 28,000 euros, with funding coming from the European Union's ASCENT+ program and is overseen by the Fraunhofer-Institute for Photonic Microsystems IPMS.

➤ Imaging Systems from DIVE for a non-invasive wafer control. © DIVE imaging systems GmbH

By integrating Fraunhofer IPMS's state-of-the-art metrology expertise in advanced defect and contamination control, the partnership aims to improve and elevate water recycling methods, reduce chemical usage, and optimize overall process efficiency – paving the way for smarter water solutions in a water-constrained future.

### Nano-pure water for sustainable water consumption

According to industry data, the semiconductor sector has experienced a 20–30% increase in water consumption in recent years, with the average chip manufacturing facility using up to 10 million gallons of UPW daily – an amount equivalent to the daily water needs of a city of 300,000 people. Producing UPW traditionally comes at a significant cost: it can be 60 to 350 times more expensive than drinking water due to the intensive energy and chemical processes required.

This is the challenge NSS Water addresses with its nano-pure water

(NPW). The semiconductor industry's water consumption is projected to keep increasing due to more advanced plants with higher consumption coming online in the coming years.

Additionally, 40% of chip production facilities are projected to be located in high-water-risk areas by 2030, meaning the need for data-driven, circular water strategies has never been more critical.

"Water is the lifeblood of our planet and the backbone of the semiconductor industry," says Reza Jafari Jam, Research Director at AlixLabs. "This collaborative research on water conservation not only safeguards a finite resource but fuels innovation, ensuring sustainable growth and technological advancement. We push the semiconductor industry to be more sustainable with our APS™ patterning process technology and our collaboration with NSS Water will further solidify our position as an enabler tomorrow's green semiconductor production."

By integrating Fraunhofer IPMS's state-of-the-art metrology expertise in advanced defect and contamination control, the partnership aims to improve and elevate water recycling methods, reduce chemical usage, and optimize overall process efficiency – paving the way for smarter water solutions in a water-constrained future

#### RESEARCH FOCUS | METROLOGY

Cooperation for advanced semiconductor manufacturing "We are happy to expand our collaboration with AlixLabs and Fraunhofer IPMS," says Björn Holmström, CEO at NSS Water. "The importance of advanced metrology will help us provide a platform that improves the water infrastructure used by AlixLabs and other advanced semiconductor players. With this project, we get to benchmark our NPW on 300-millimeter wafers as well as have the wafers cleaned with NPW by Fraunhofer IPMS."

Through this partnership, AlixLabs and NSS Water are combining their respective strengths in innovative water treatment, advanced analytics, and semiconductor manufacturing know-how to develop solutions that significantly reduce water usage, lower operational costs, and bolster sustainability. Fraunhofer IPMS's involvement ensures precise contamination and defect control, further enhancing the effectiveness

Experts from DIVE and Fraunhofer IPMS in the cleanroom at Fraunhofer IPMS in Dresden. © Fraunhofer IPMS.

of the recycling and purification processes. Co-financed by the European Nanoelectronics Access program ASCENT+, which provides a direct gateway to Europe's globalscale Nanoelectronics Research Infrastructure, granting researchers, SMEs, and PhD candidates access to state-of-the-art capabilities. The project is an important step in positioning AlixLabs, NSS Water and the European Union at the forefront of sustainable semiconductor manufacturing innovations.

SCREEN

# **Wafer Cleaning System**

Wet Station | Spin Scrubber | Single Wafer Cleaner

15,000+ units shipped

SCREEN Semiconductor Solutions Co., Ltd.

**SEMICON® WEST** October 7-9, 2025 SCREEN Booth #6545

# Innovative approaches to scaling network-on-chip architectures

The evolution of cloud computing has sparked a pressing need for advanced solutions that maximize computational efficiency while minimizing physical and energy constraints. Modern data centers depend heavily on multi-core processors, often packing over 100 cores into a single chip.

BY MORITZ BRUNION, RESEARCHER DESIGN-TECHNOLOGY CO-OPTIMIZATION AND JAMES MYERS, PROGRAM DIRECTOR SYSTEM TECHNOLOGY CO-OPTIMIZATION, BOTH AT IMEC.

THESE PROCESSORS are designed to handle the growing demands of cloud-based applications by sharing network, memory, and storage resources, transforming each core into a rentable unit of processing power.

However, as processors grow more powerful, the network-on-chip (NoC) has emerged as a critical

bottleneck in scaling. The NoC, tasked with routing data among CPU cores and memory, relies on metal interconnects that present unique challenges when scaled down. Higher resistance in these interconnects increases power consumption and necessitates additional signal repeaters to maintain performance over long distances.

Adding to this, the increasing core count and HD logic scaling, while maintaining the same NoC dimensions, drive a significant rise in NoC area. These factors add complexity and compromises the goal of achieving smaller and more efficient designs.

Addressing these challenges has led to a variety of innovative solutions, though none without tradeoffs. 2D mesh topologies, while straightforward and scalable, struggle with communication latency as the number of cores increases.

Other approaches, such as routerless configurations or workload-specific optimizations, can improve performance but are often impractical for general-purpose systems like those used in cloud computing. While scaling the NoC link throughput by an increase in the number of signals per channel can increase the throughput, it often results in higher costs and resource demands, further complicating the NoC landscape.

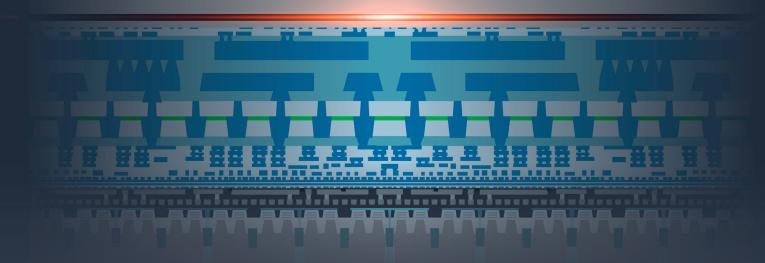

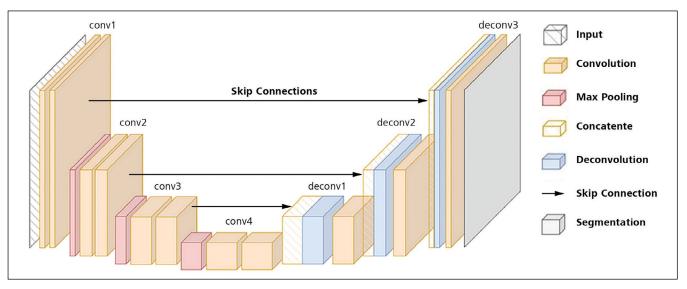

In response to these constraints, imec researchers have pioneered two transformative approaches: relocating NoC channels to a dedicated die and integrating them with the backside power delivery network (BSPDN). These strategies, guided by system-technology co-optimization (STCO) principles, aim to overcome scaling limitations while balancing cost and performance. Of these, the co-integration of NoC channels with the BSPDN offers particularly promising results for future design of such high core-count systems.

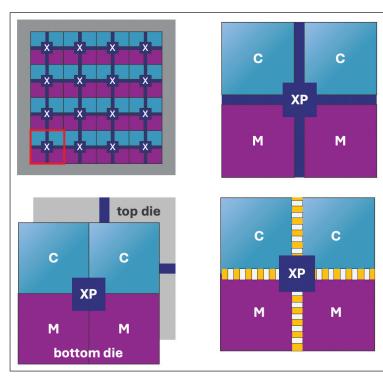

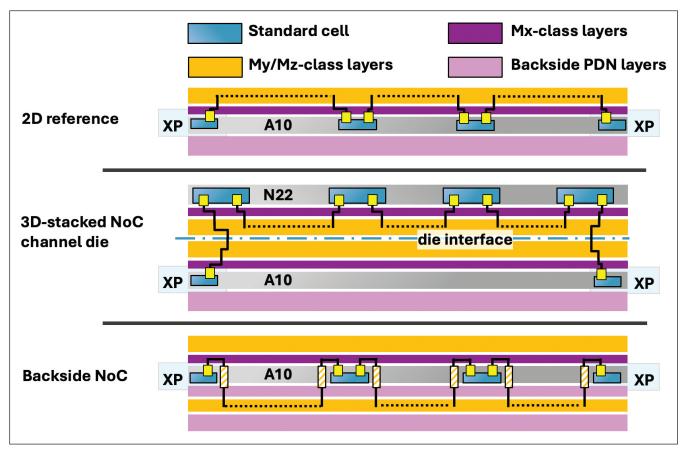

> Figure 1. 2D reference system (top left) and tile (top right) with NoC channel routes and logic within a single FEOL and BEOL stack. In the bottom are the two new approaches depicted: (left) 3D stacking design, showing the separation of NoC channel routes into a dedicated routing die bonded to the A10 logic die, and (right) the backside integration approach, showing NoC channel routes integrated into the backside metal layers of the BSPDN.

Figure 2. (Top) The technology stack cross-section for the 2D reference shows both NoC channels and crosspoints (XP) in the A10 logic frontend. (Middle) The NoC routing is entirely offloaded to a dedicated die freeing up placement and routing resources on the main logic die. In this case, channels in the separate die are manufactured in older technology while the crosspoints reside in the A10 logic. (Bottom) The NoC channels sharing routing resources with the power delivery network and repeaters located on the logic die front-end. NoC buffer islands occupy 1-2% of a high-performance CPU core (compared to up to 10% of the silicon area being dedicated to the NoC in the 2D reference), with the addition of two dedicated backside metal layers for NoC channels.

### Dedicated NoC routing on a separate die

One novel approach proposed by imec involves offloading the NoC channel routes to a dedicated die, independent of the main logic layers. Using wafer-to-wafer face-to-face hybrid bonding, this architecture can leverage the high-bandwidth data transfer in the vertical direction with minimal energy usage per bit. The NoC die can be fabricated using a less advanced manufacturing process, such as N22, significantly reducing production costs.

This design also simplifies the back-end-of-line (BEOL) configuration by using fewer metal layers, thereby optimizing functional integration efficiency. The NoC routers, which make real-time routing decisions, remain on the main logic die, ensuring that latency is kept to a minimum.

This design, however, is not without its challenges. Power distribution becomes more complicated, as the additional die requires its own power infrastructure. Physical design experiments also revealed an 8% increase in propagation delay and

a 15% rise in energy per bit transferred across a channel link compared to conventional 2D NoC systems.

#### Backside integration with the BSPDN

A second solution involves co-integrating NoC channels with the BSPDN on the backside of the wafer. The BSPDN's existing metal layers, optimized for power delivery with wider pitches and lower resistance, provide an ideal foundation for routing NoC channels over long distances at high clock speeds. This integration takes advantage of the relaxed design constraints of backside interconnects to achieve efficient signal transmission.

To implement this approach, the researchers made several design adjustments. First, they devised a bidirectional wiring scheme, enabling both horizontal and vertical NoC channels to share the same metal layer. This reduces the total number of required layers, lowering both costs and the overall chip footprint. Second, since BSPDN currently doesn't support active devices on the backside, signal repeaters were placed as compact "islands"

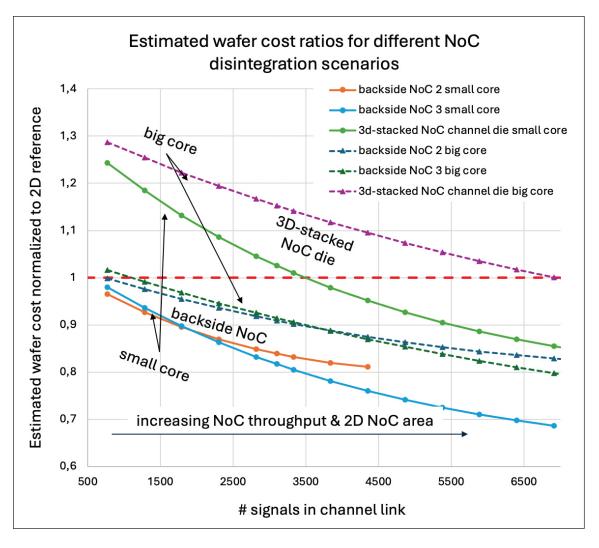

> Figure 3. Estimated wafer cost ratios of different NoC integration schemes, normalized to the 2D baseline. As the width of the NoC channel increases, the cost advantage of backside integration becomes more evident.

on the main logic die. These repeaters ensure robust signal strength at a small area overhead, while freeing up the channel routing footprint in the main logic die for other logic components. Finally, integrating NoC channels with the BSPDN required addressing the shared routing resources between data and power delivery, which increases the risk of IR drop and can affect performance. To mitigate these challenges, the researchers traded-off the PDN pitches and IR drop against the area overhead of the repeater islands, maintaining the benefits of the BSPDN and ensuring stable voltage levels, while also supporting reliable data transmission across the NoC.

### Cost-benefit analysis favours NoC backside integration

When comparing the two approaches, not only their technical trade-offs but also cost-effectiveness is important to identify the best solution for growing

demands. The dedicated die method offers greater flexibility and customization options but incurs higher manufacturing costs due to the need for an additional fully processed wafer. By contrast, integrating NoC channels with the BSPDN reuses existing infrastructure, adding only a few extra metal layers. This significantly reduces costs and optimizes the use of front-side silicon, making it an attractive option for applications requiring high core densities, such as cloud server CPUs.

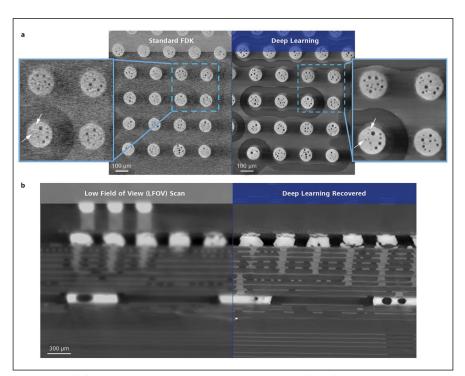

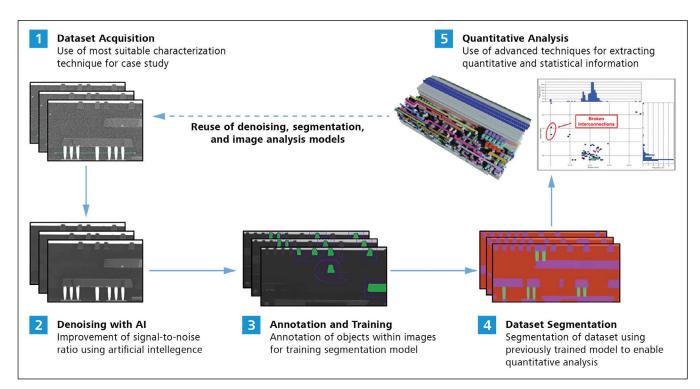

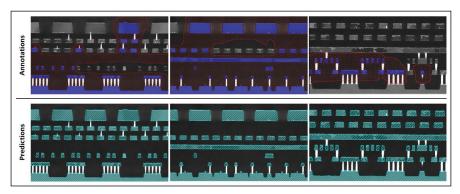

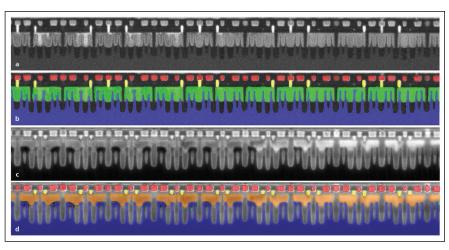

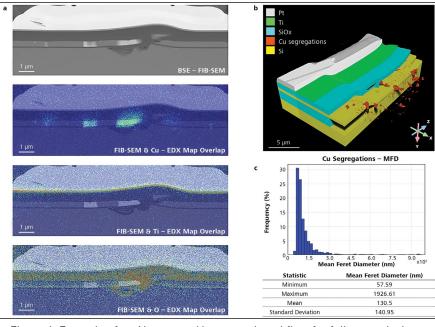

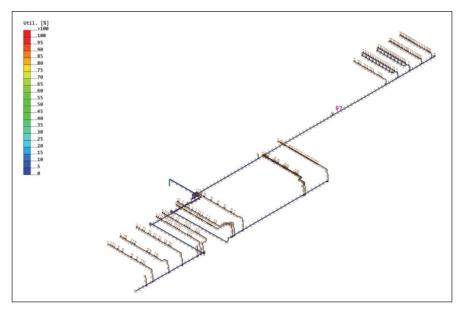

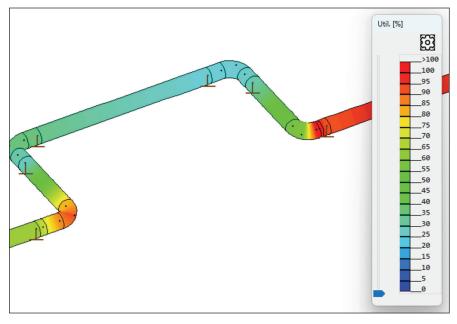

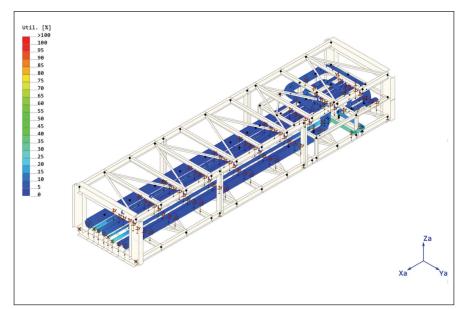

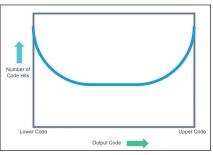

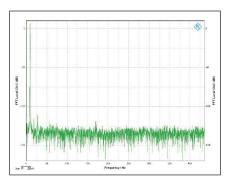

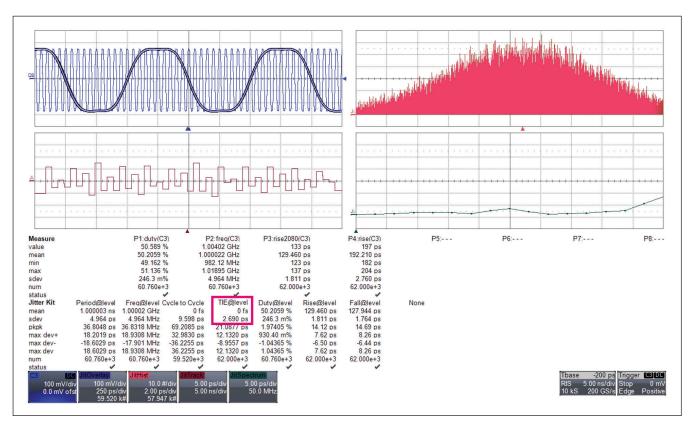

Backside integration also excels in scalability. As core counts per processor continue to rise, the demand for wider NoC channels increases. By leveraging the backside metal layers, this approach minimizes congestion and enables higher data throughput without substantially increasing the silicon footprint. These attributes make it a compelling solution for next-generation chip architectures.