# **SEBUCION SEMICONDUCTOR COMMUNITY**

NEXT GEN 3D X-RAY INSPECTION FOR ADVANCED PACKAGING: TO SEE BETTER. FASTER. MORE.

c•met

#### VOLUME 45 ISSUE VIII 2024

### INSIDE

News Review, Features News Analysis, Profiles Research Review and much more...

#### AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

### Cleaning solutions for microelectronics industry

This rapidly advancing field faces considerable environmental challenges, particularly regarding its cleaning processes

### BEYOND AOI: AI-revolution in visual inspection

The need for accurate, efficient, and adaptable inspection processes has never been more pressing

#### SILICONSEMICONDUCTOR.NET

#### Unstoppable growth in a billion-dollar market

Companies and governments are investing heavily in semiconductor technology to stabilise supply chains and meet demand such as Al

### FUSION AND HYBRID BONDING FOR HETEROGENEOUS INTEGRATION

Enabling advanced 3D device stacking and chiplet integration for CMOS image sensors, memory and 3D system-on-chip (SoC)

High-volume production equipment and process technology for Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding

GEMINI® FB Automated Production Wafer Bonding System delivers industry leading alignment accuracy and bonding performance

Heterogeneous Integration Competence Center<sup>™</sup> serving as leadingedge innovation incubator for EVG customers and partners

GET IN TOUCH to discuss your manufacturing needs www.EVGroup.com

# VIEWPOINT

By Phil Alsop, Editor

# Plenty of reasons to celebrate the semiconductor industry's success

THE NEWS PAGES in this issue of Silicon Semiconductor demonstrate an industry in good health, with plenty of grounds for optimism over the next few years, whether or not that \$1 trillion target is reached in 2030 of beyond.

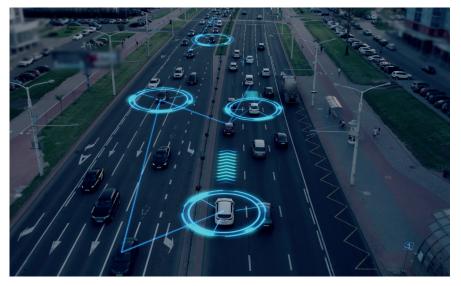

One could reasonably argue that semiconductors are the most important components of the modern vehicle – whether that's the ADAS which continue to evolve, EVs themselves, or the Internet of Vehicles. Yes, many will still think of the transport future as a little bit too science fiction for their liking, but there's no doubting the general direction of travel or the massive role which semiconductors will continue to play in adding more and more intelligence to vehicles for safety and/or sustainability reasons.

Onshoring, reshoring, whatever name we give to the process of countries taking back control of their manufacturing activities, continues to be a major consideration for many nations. At the very least, countries want to ensure a safe and secure semiconductor supply chain. How much of this can be established in country, and how much relies on collaboration with other like-minded nations, remains to be seen. But the UK, Germany (and the wider EU) and India/Singapore news in this issue are just some of the latest developments in this ongoing process. No one wants to have to worry about their chip supply chain. Alongside supply chain security, sustainability remains a major focus for the industry – and the 'Carbon dioxide capture success' story provides plenty of food for thought. Quite how our digital world can also be truly sustainable remains to be seen (without some radical consumption restrictions at some future date), but it's great to see that much work is being done in this area.

Visitors to SEMICON Europa will have the chance to see and hear how the industry is addressing the sustainability challenge, as well as, of course, witnessing how the industry continues to innovate in so many ways.

Which brings us neatly to Infineon's announcement that it has developed what it says is the world's first 300 mm power gallium nitride (GaN) technology. The silicon semiconductor industry remains the bedrock of the semiconductor sector, but it is fascinating to see the development of the new compound semiconductors, and to try and understand how they will fit alongside existing materials and solutions and where they will likely replace them.

In summary, the semiconductor industry seems to be in a good, if not great, place right now. Let us hope that this momentum continues, whatever the geopolitical climate, and however the 'great' AI story unfolds.

For your free weekly e-news roundup go to: siliconsemiconductor.net

### CONTENTS

#### VOL 45ISSUE VIII 2024

### 26

Next Gen 3D X-Ray Inspection for Advanced Packaging: To see better. Faster. More.

### 16 Semiconductors: Unstoppable growth in a billion-dollar market

Both companies and governments are investing heavily in semiconductor technology to stabilise supply chains and meet demand through innovation drivers such as Al.

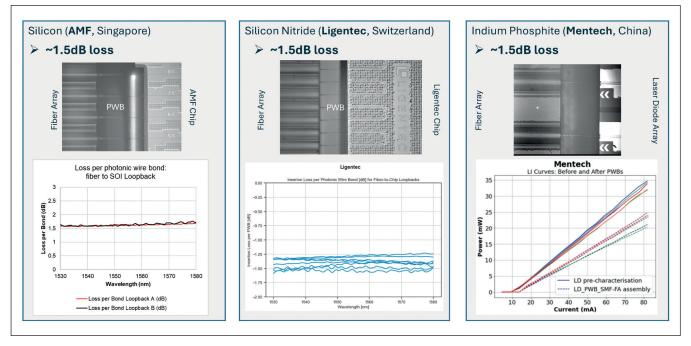

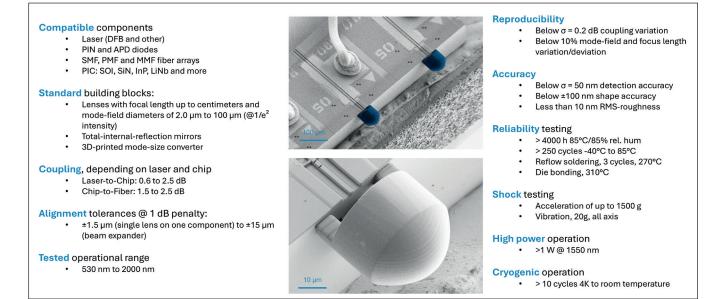

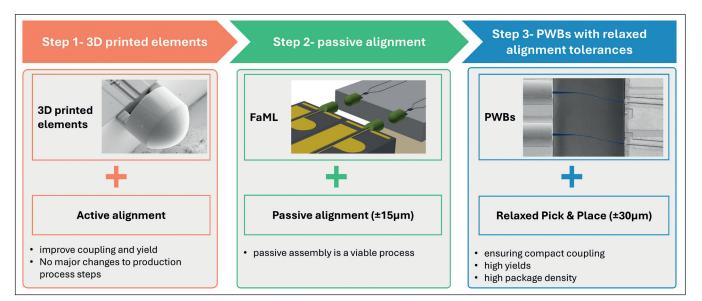

### 30 Bringing tomorrow's photonics to life with fully automated photonic wire bonding and facet-attached micro-lenses

Vanguard Automation is enabling a bright future for photonic packaging and integration with scalable industry-ready 3D nano-printing solutions

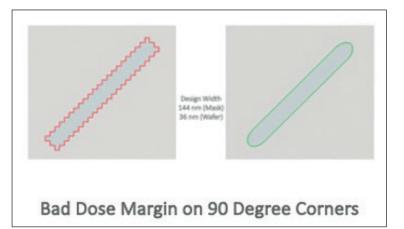

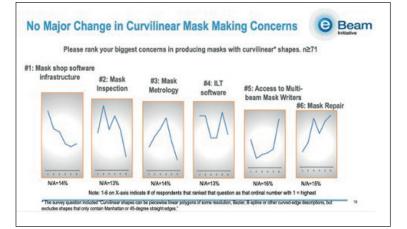

### 36 Why the mask world is moving to curvilinear

If you've been to a lithography or photomask technology conference lately, you've likely noticed a trend: many papers and talks on curvilinear masks, curvilinear OPC, curvilinear ILT, curvilinear mask process correction (MPC), and curvilinear mask formats

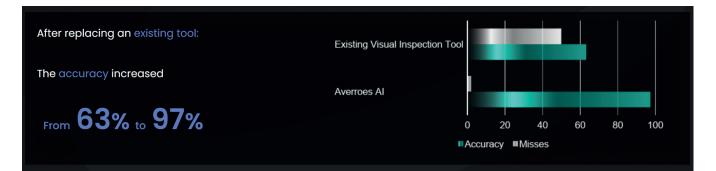

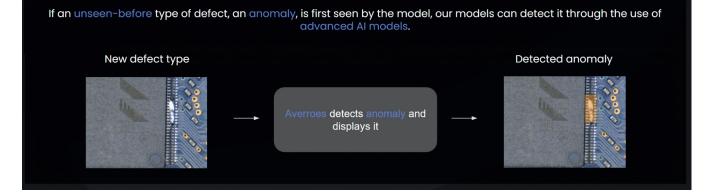

### 42 Beyond AOI: an AI-driven revolution in visual inspection

As industries strive to produce flawless products, the need for accurate, efficient, and adaptable inspection processes has never been more pressing

### 48 Sustainable cleaning solutions for a greener microelectronics industry

The microelectronics industry powers the devices that define modern life, from smartphones and computers to vehicles and medical equipment. However, this rapidly advancing field also faces considerable environmental challenges, particularly regarding its cleaning processes

### 52 Splitting hairs to ten to the power of four

14ACMOS: EU project for the next technology node in semiconductor manufacturing

### 56 TSMC enables semiconductor fabrication expansion with AMD

Better cost-performance with fewer servers by deploying  $4^{\mbox{\tiny th}}$  Gen AMD EPYCprocessors

### 59 Test early and test often

Emanuele Bardo, Vice President for the Semiconductor and MEMs Test Business Unit at SPEA, talks to Silicon Semiconductor Editor, Philip Alsop, about the importance of power semiconductor testing

### **RESEARCH NEWS**

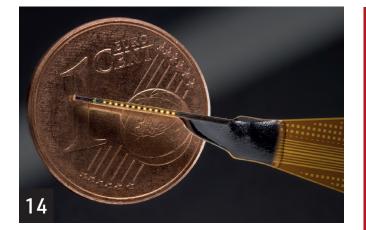

### 14 Optogenetic OLED-on-CMOS stimulators for neurosensory therapies

Researchers from the Fraunhofer Institute for Photonic Microsystems IPMS and the Max Planck Institute for Multidisciplinary Natural Sciences (MPI-NAT) have researched optical stimulators for future cochlear implants as part of the "NeurOpto" project (funded by the Fraunhofer-Max-Planck Cooperation Program: 601001).

### SEMI NEWS UPDATE

### 20 SEMI Consortium to develop cybersecurity strategy and roadmap

Seeking to strengthen the semiconductor industry's resilience to cybersecurity threats, the global association SEMI is to create of a strategic roadmap for cybersecurity implementation throughout the industry.

### **NEWS**

- 06 Automotive semiconductor market poised for \$88 billion by 2027

- 07 Support for semiconductor firms to grow, powering growth in £10bn UK industry

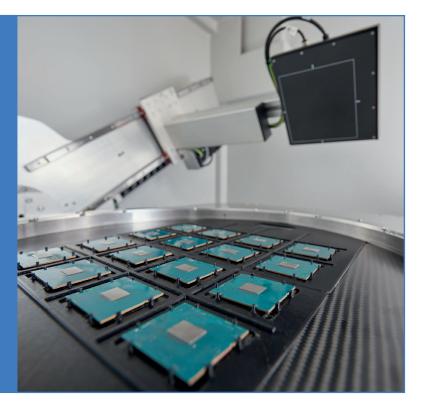

- **08** Commission approves €5 billion German State aid measure to support ESMC

- 09 ESMC breaks ground on Dresden fab

- 10 Singapore and India sign MOU on semiconductor ecosystem partnership

- 11 Carbon dioxide capture success

- 12 An industry game-changer?

#### Publisher Jackie Cannon Editor Phil Alsop Sales & Marketing Manager Shehzad Munshi

Marketing & Logistics Executive Eve O'Sullivan USA Representatives Tom Brun Brun Media Janice Jenkins Director of Logistics Sharon Cowley

Design & Production Manager Mitch Gaynor

phil.alsop@angelbc.com shehzad.munshi@angelbc.com eve.osullivan@angelbc.com tbrun@brunmedia.com iienkins@brunmedia.com +44 (0)1923 690200 sharon.cowlev@angelbc.com mitch.gaynor@angelbc.com

jackie.cannon@angelbc.com

Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley sukhi.bhadal@angelbc.com +44 (0)2476 718970 scott.adams@angelbc.com +44 (0)2476 718970

Published by Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP. UK T: +44 (0)2476 718 970 E: info@angelbc.com

Silicon Semiconductor is published ten times (6x print and 4x video issues) a vear on a controlled circulation basis. Non-aualifying individuals can subscribe at: £50.00 per annum (UK). €60.00 per annum ( Europe), \$90 per annum (air mail)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2024. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Silicon Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA.

+44 (0)1923 690205

+44 (0)1923 690215

+44 (0)2476 823123

+001724539-2404

+001724-929-3550

+44 (0)1923 690214

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise. Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2024.

### **INDUSTRY NEWS**

# Automotive semiconductor market poised for \$88 billion by 2027

The global automotive semiconductor market is on track to surpass \$88 billion by 2027, driven by the surging demand for high-performance computing (HPC) chips, graphics processing units (GPUs), radar chips, and laser sensors.

THIS GROWTH is fueled by the increasing adoption of the advanced driver assistance system (ADAS), electronic vehicles (EVs), and Internet of Vehicles (IoV), bringing new growth opportunities for the automotive semiconductor sector, according to a recent report titled 2023 Worldwide Competitive Landscape of Automotive Semiconductor.

IDC predicts that as the value of semiconductors per vehicle continues to rise, semiconductor companies will become increasingly critical to the automotive supply chain.

Leading semiconductor companies such as Infineon, NXP, STMicroelectronics, Texas Instruments (TI), and Renesas Electronics are investing heavily in developing solutions for nextgeneration microcontrollers, system on a chip (SoC), and high-resolution radars.

To meet the needs of automobiles for higher volume, higher performance, and higher safety of semiconductors, they continuously enhance ADAS, autonomous driving systems, and cockpit and networking features and integrate complex electronic control units (ECUs) and sensor fusion technology.

According to International Data Corporation (IDC)'s recently released report, 2023 Worldwide Competitive Landscape of Automotive Semiconductor ( Doc #US50917724, July 2024), the top five vendors in the automotive semiconductor market captured over 50% of the market share in 2023. Infineon led the market with a share of 13.9%; it was followed by NXP and STMicroelectronics, holding a market share of 10.8% and 10.4%, respectively; TI and Renesas Electronics also demonstrated strong performance, accounting for 8.6% and 6.8%,

respectively, of the total share. The market landscape is as follows:

- Through ongoing technological innovation, strategic acquisitions, robust supply systems, and close cooperation with automotive original equipment manufacturers (OEMs), Infineon consistently elevated its market position in the field of power electronics and advanced control systems, establishing itself as a leader in the power semiconductor market.

- NXP possesses deep expertise in vehicle-to-everything (V2X) communication and security technologies and continually innovates and iterates. It is a frontrunner in this field as a supplier of comprehensive product solutions through close cooperation with automotive OEMs and Tier 1 suppliers.

- STMicroelectronics offers innovative solutions for the automotive industry by virtue of its specialisation in micro-electromechanical systems (MEMS) and power semiconductors.

- TI, with a wide range of analog chips and embedded solutions, delivers product portfolios that meet customers' needs. Meanwhile, it has

a robust supply chain management and product quality management system to support it.

Renesas Electronics offers

a comprehensive collection of microprocessors and SoCs to ensure functional safety and reliability. Meanwhile, it employs strategic acquisitions and cooperation to maintain its leading edge in the industry.

Advancements in the automotive sector have fueled the demand for high-performance, high-safety semiconductors. As EVs and autonomous driving technologies evolve, those semiconductor companies will continue to play a key role in the global automotive semiconductor market.

According to Adela Guo, Research Director at IDC Asia Pacific, "The common strengths of these leading semiconductor vendors include substantial R&D investment and strong technological leadership, comprehensive product portfolios, solid strategic partnerships, efficient global operations, as well as safe and reliable product performance."

# Support for semiconductor firms to grow, powering growth in £10bn UK industry

Science Minister Lord Vallance unveils new support for UK semiconductor scale-ups to advance innovations, from phone screens to medical tech.

UK SEMICONDUCTOR firms producing vital technology from phone screens to surgical lasers are being backed in their efforts to scale up into large businesses and drive economic growth.

The science Minister Lord Patrick Vallance has announced the 16 projects that will win a share of a £11.5 million pot – provided by Innovate UK – that will help drive innovation, as he opened an industry conference of G7 nations today (Thursday 26 September).

Pioneering projects across the country will help take the UK's thriving semiconductor industry to the next level as it further enhances everyday life – from more efficient medical devices to energy saving phone screens – and kickstart economic growth.

This comes shortly before the Government's International Investment Summit which will showcase the UK as a place to do business. Today's move is yet another reason for business to choose the UK as a place to invest – as it is backing the industries of the future. A new report by Perspective Economics reveals the UK semiconductor sector, which includes over 200 companies in research, design, and manufacturing, is valued at almost £10 billion and could grow up to £17 billion by 2030.

Semiconductors are small chips at the core of everyday technology from smartphones to renewable energy systems and this support will help to scale up domestic manufacturing and strengthen supply chain resilience, so the UK is fit for the future in a global industry.

The funding comes as the G7 Semiconductors Point of Contact group kicks off with a stakeholder forum at major UK tech company Arm's HQ in Cambridge, where member states, research organisations, and industry representatives are discussing key issues affecting the global semiconductor industry, like supporting early-stage innovation and sustainability.

Science Minister, Lord Vallance, said: "Semiconductors are an unseen but vital component in so many of the technologies we rely on in our lives and backing UK innovators offers a real opportunity to growth these firms into industry leaders, strengthening our £10bn sector and ensuring it drives economic growth.

"Our support in these projects will promote critical breakthroughs such as more efficient medical devices that could significantly lower costs and faster manufacturing processes to improve productivity.

"Hosting the G7 semiconductors Points of Contact group is also a chance to showcase the UK's competitive and growing sector and make clear our commitment to keeping the UK at the forefront of advancing technology."

Among the funded projects, receiving a share of £11.5 million, is Vector Photonics Limited in collaboration with the University of Glasgow, which aims to enhance the power and costeffectiveness of blue light lasers in everyday technology by using gallium nitride, a high-performance material. Blue lasers are key in devices like medical equipment, quantum displays and car headlights.

Another project, led by Quantum Advanced Solutions Ltd with the University of Cambridge, is developing advanced shortwave infrared (SWIR) sensors which improve vision in critical sectors like defence, by supporting surveillance in challenging conditions

in low-visibility environments, such as during adverse weather conditions or atmospheric disturbances. The project looks to simplify production using innovative quantum dot materials – tiny semiconductor particles that emit light at specific wavelengths – offering higher sensitivity and performance, cutting costs and making this advanced technology more accessible to multiple sectors including manufacturing and healthcare.

The G7 Semiconductors Point of Contact Group, established under Italy's G7 Presidency earlier this year, continues its mission to address issues impacting the semiconductor industry, including early-stage innovation, crisis coordination, sustainability, and the impact of government policies and practices.

This meeting immediately follows the OECD Semiconductor Informal Exchange Network gathering, where countries and stakeholders shared strategies for strengthening global semiconductor supply chains and addressing shared challenges in the semiconductor industry.

The UK is playing a key role in the OECD's efforts to unite government and industry in navigating the complexities of the global chip supply chain.

### **INDUSTRY NEWS**

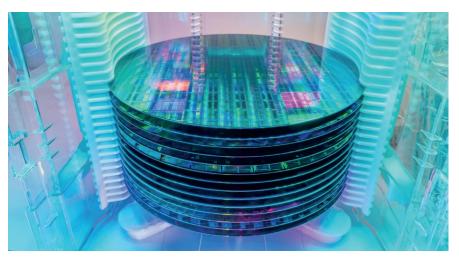

# Commission approves €5 billion German State aid measure to support ESMC

The European Commission has approved, under EU State aid rules, a €5 billion German measure to support European Semiconductor Manufacturing Company ('ESMC') in the construction and operation of a microchip manufacturing plant in Dresden.

ESMC is a joint venture between Taiwan Semiconductor Manufacturing Company ('TSMC'), Bosch, Infineon, and NXP. The measure will strengthen Europe's security of supply, resilience and digital sovereignty in semiconductor technologies, in line with the objectives set out in the European Chips Act Communication. The measure will also contribute to achieving the digital and green transitions.

Germany notified the Commission of its plan to support ESMC's project to build and operate a new semiconductor production facility in Dresden, Germany. The project aims at serving the demand for automotive and industrial applications.

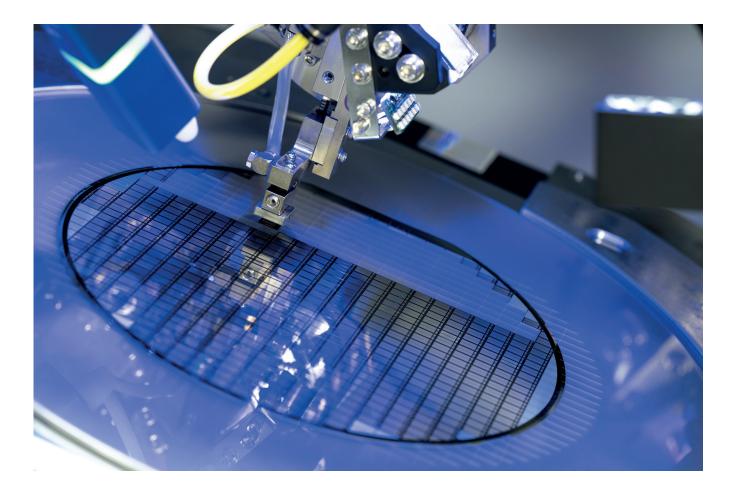

The new large-scale manufacturing facility supported under the measure will deliver high-performance chips, based on 300mm silicon wafers with node sizes covering 28/22nm and 16/12nm, using field-effect transistor ('FinFET') technology and allowing the integration of several additional features in one chip. The produced chips will offer better performance while at the same time reducing total power consumption. The plant, which is planned to be operating at full capacity by 2029, is expected to produce 480,000 silicon wafers per year.

The facility will operate as an open foundry, meaning that any customer – including but not limited to the three other shareholders besides TSMC – can place orders for the production of specific chips. This operating model is important for the wider EU ecosystem, especially in view of ESMC's commitments to provide dedicated support to European small and medium enterprises ('SMEs') and start-ups, to strengthen their knowhow and competences. The facility will also provide special access to its production

capacities for SMEs and European universities, further supporting research and knowledge creation within Europe. The Commission's assessment The Commission assessed the German measure under EU State aid rules, in particular Article 107(3) (c) of the Treaty on the Functioning of the European Union ('TFEU'), which enables Member States to grant aid to facilitate the development of certain economic activities subject to certain conditions, and based on the principles set out in the European Chips Act Communication.

The Commission found that:

- The measure facilitates the development of certain economic activities, by enabling the establishment of a new massproduction facility for innovative technologies and chips in Europe.

- O The facility is first-of-a-kind in Europe, as there currently is no comparable mass-production facility for the specific technology features offered. ESMC will be the first open foundry that will produce silicon wafers with 28/22nm and 16/12nm technology nodes, using FinFET technology with logic, mixed-signal, radio frequency and embedded non-volatile memory technology processes. These specific technologies differentiate it from other existing capacity and complement the production capacities needed by European customers.

- The aid has an 'incentive effect', as

the beneficiary would not carry out this investment without public support.

- The measure has a limited impact on competition and trade within the EU. It is necessary and appropriate to ensure the resilience of Europe's semiconductor supply chain. In addition, the aid is proportionate and limited to the minimum necessary based on a proven funding gap (i.e. the aid amount necessary to attract the investment that otherwise would not take place). Finally, ESMC has agreed to share with Germany potential profits beyond current expectations.

- The measure has wide positive effects for the European semiconductor ecosystem and contributes to strengthening Europe's security of supply, in particular by setting up an open foundry providing access for European customers, including SMEs and start-ups. It will also enable additional support for European universities. Furthermore, ESMC has committed to comply with priority rated orders to produce crisis-relevant products in Europe in case of a crisis, as defined in the EU Chips Act Regulation. The Commission also took note that ESMC has committed to apply to be recognised as an Open EU Foundry under the EU Chips Act Regulation and will comply with all obligations linked to this status, including the commitment to invest in continued innovation in the EU with a view to achieving concrete advances in semiconductor technology, by preparing next-generation technologies as well as investing in the Union's talent pipeline.

On this basis, the Commission approved the German measure under EU State aid rules.

### ESMC breaks ground on Dresden fab

ESMC – a joint venture between TSMC, Robert Bosch GmbH, Infineon Technologies AG and NXP Semiconductors N.V. – recently held a groundbreaking ceremony to officially mark the initial phase of land preparation for its first semiconductor fab in Dresden, Germany.

THE EVENT brought together government officials, customers, suppliers, business partners and academia to celebrate a milestone in establishing what will be the EU's firstever FinFET-capable pure-play foundry. Distinguished guests included president of the European Commission Ursula von der Leyen, German Chancellor Olaf Scholz, and Saxony Minister President Michael Kretschmer and Lord Mayor of Dresden, Dirk Hilbert.

In a demonstration of dedicated support, during the event, President von der Leyen announced that the European Commission has approved, under EU State aid rules, a  $\in$ 5 billion German measure to support European Semiconductor Manufacturing Company (ESMC) in the construction and operation of the semiconductor fab.

"Together with our partners, Bosch, Infineon and NXP, we are building our Dresden facility to meet the semiconductor needs of the rapidly growing European automotive and industrial sectors," said TSMC Chairman & CEO C.C. Wei. "With this state-of-the-art manufacturing facility, we will bring TSMC's advanced manufacturing capabilities within reach of our European customers and partners, which will stimulate economic development within the region and drive technological advancements across Europe."

When fully operational, ESMC is expected to have a monthly production capacity of 40,000 300mm (12-inch) wafers on TSMC's 28/22 nanometer planar CMOS and 16/12 nanometer FinFET process technology, further strengthening Europe's semiconductor manufacturing ecosystem with advanced FinFET transistor technology. Total investments are expected to exceed 10 billion euros consisting of equity injection, debt borrowing, and strong support from the European

Union and German government. The new facility is expected to generate around 2,000 direct hightech professional jobs. Additionally, each direct job created by the project is expected to stimulate the creation of numerous indirect jobs throughout the EU supply chain, bolstering the region's economy. ESMC will uphold TSMC's standards of sustainability and environmental protection. In line with this mission, ESMC and its partners are dedicated to constructing a green fab that utilizes both existing and cutting-edge techniques to optimize conservation. This includes energy-efficient construction, water reclamation, and obtaining LEED certification.

The establishment of ESMC exemplifies the strength of TSMC's Grand Alliance, a cornerstone of innovation within the semiconductor industry. This alliance has driven groundbreaking advancements, bringing together TSMC's partners for a new level of collaboration. The investment in ESMC signifies not just a deeper commitment to this strategic partnership, but also underscores TSMC's unwavering dedication to nurturing innovation across Europe. Construction is expected to start later this year.

"The ESMC wafer fab is to be built right next door to our own Bosch wafer fab in Dresden. So now we will be able to watch it emerge and grow with our own eyes. We're looking forward to that, just as we are to collaborating closely with our partners TSMC, Infineon, and NXP. Together, we will take Europe a decisive step forward in a key industry, and ensure that advanced chips are available for industrial enterprises here," said Dr. Stefan Hartung, chairman of the board of management of Robert Bosch GmbH.

"Our joint investment in Dresden once again highlights the enormous significance of Silicon Saxony as a magnet for leading international semiconductor manufacturers." said Infineon Technologies AG CEO Jochen Hanebeck. "The construction of another semiconductor manufacturing facility in Dresden by ESMC constitutes a major success for the region. We are bringing to Europe a particularly important semiconductor technology which is used in the most modern digital chips. This investment will create additional jobs and will permanently strengthen the semiconductor ecosystem in Silicon Saxony, Germany and Europe as a whole."

#### **INDUSTRY NEWS**

# Singapore and India sign MOU on semiconductor ecosystem partnership

Singapore and India exchanged a Memorandum of Understanding (MOU) to partner and cooperate in the field of semiconductors.

THE MOU aims to support India's growing semiconductor industry while facilitating Singapore's ecosystem of semiconductor companies and related supply chains to participate in the fastgrowing Indian market. The MOU was exchanged in the presence of India's Prime Minister Narendra Modi and Prime Minister Lawrence Wong during Prime Minister Modi's Official Visit to Singapore. It was signed earlier by Deputy Prime Minister and Minister for Trade and Industry, Gan Kim Yong and India Minister of Electronics and Information Technology. Ashwini Vaishnaw, on the sidelines of the India-Singapore Ministerial Roundtable on 26 August 2024.

#### **MOU on India-Singapore**

Semiconductor Ecosystem Partnership India aims to establish itself as a global node for semiconductor manufacturing, driven by strong domestic demand in the electronics, electric vehicles, and manufacturing sectors. Singapore's established semiconductor ecosystem has produced a strong cluster of semiconductor companies which are keen to participate in the growth of India's semiconductor industry.

Under the MOU, Singapore and India will leverage complementary strengths in their semiconductor ecosystems and tap on opportunities to build resilience in their semiconductor supply chains. This will include governmentled policy exchanges on ecosystem development, supply chain resilience, and workforce development. The Ministry of Trade and Industry (MTI) and India's Ministry of Electronics and Information Technology (MeitY) will establish a Policy Dialogue to facilitate discussions, oversee the implementation of the areas of collaboration, and exchange best practices. A parallel businessto-business Cooperation Forum will be established and led by Enterprise

Singapore and the India Semiconductor Mission (ISM) to encourage and catalyse more private sector partnerships between both countries.

Deputy Prime Minister and Minister for Trade and Industry Gan Kim Yong said, "This MOU signals India's and Singapore's commitment to work together in the field of semiconductors to address the demand from industries around the world. This will also strengthen semiconductor supply chain resilience and create new markets and opportunities for businesses in our countries."

"Singapore plays an important role in the global semiconductor supply PRESS RELEASE chain. Our companies bring with them extensive expertise through their collaborations with global semiconductor players, and can value-add by providing services, solutions, components and more to global chipmakers and large equipment manufacturers. These capabilities and track record position them well to cement and strengthen the partnership between Singapore and India in the semiconductor space," said Deputy Managing Director, Enterprise Singapore, Tan Soon Kim. "Through our

series of semiconductor delegations to India this year, EnterpriseSG has also seen positive reception from the engagements between Singapore companies and Indian officials and partners. We encourage more companies to leverage this latest MOU to tap on the growing opportunities in India."

Growing momentum between India's and Singapore's semiconductor ecosystems

During his visit in Singapore, Prime Minister Modi was hosted to a site visit by Singapore semiconductor ecosystem player, AEM Singapore. He was accompanied by Prime Minister Wong and Minister for Home Affairs and Minister for Law K Shanmugam. The visit comprised a sharing led by Singapore Semiconductor Industry Association (SSIA) on the development of Singapore's semiconductor industry and opportunities for mutual collaboration between Singapore and India partners, and a tour of AEM's facilities. Prime Minister Modi also engaged with ecosystem players and institutions such as APP Systems, Century Water, Ecsal Technologies, NexGen Wafer Systems, PEP Innovation and Temasek Polytechnic.

### Carbon dioxide capture success

WACKER successfully tests carbon dioxide capture from the silicon production process.

WACKER has successfully captured carbon dioxide (CO<sub>2</sub>) generated from silicon production. The project, which was enabled by the technology and expertise of the SLB and Aker Carbon Capture Joint Venture (SLB-ACC JV), involved a pilot test of the capture process at WACKER's production site in Holla, Norway, where quartz and carbon are combined to produce silicon for use in its silicone products. This reaction generates a considerable share of the CO<sub>2</sub> emissions relevant to WACKER and its products. The newly tested capture process makes it possible to reuse or store this greenhouse gas and prevent its release into the atmosphere – a critical step on the road to net-zero chemicals production.

Holla is where WACKER manufactures roughly one-third of the silicon metal that it needs for its production. The company carried out a successful carbon-capture pilot project here. Combined with green electricity and the use of renewable charcoal, this will open the door to future climate-neutral silicon value chains (photo: WACKER) SLB-ACC JV specializes in capturing CO<sub>2</sub> from flue gases from largescale industrial processes, including unavoidable CO<sub>2</sub> such as that generated in the production of metallurgical-grade silicon. WACKER's production plant in Holla produces this important raw material, which serves as the basis for microchips, solar modules and the full range of silicones.

SLB ACC JV's mobile test unit (MTU) was installed at WACKER's site in Holla. The MTU is a complete  $CO_2$  capture plant on a small scale. The waste gas generated from silicon production was piped directly into the pilot plant, where carbon dioxide was captured via a chemical process known as amine

scrubbing. This makes use of an aminecontaining solvent that selectively extracts  $CO_2$  from the gas mixture. In large-scale industrial processes, the  $CO_2$  is then released from the solvent by desorption before it is cooled, condensed under pressure and purified.

#### On the road to closed carbon cycles

For the first time, WACKER has demonstrated the amine scrubbing method for removing carbon dioxide in one of its own processes. The pilot test campaign, which was successfully concluded in late June, achieved capture rates of over 95%. The project team also thoroughly studied and validated the process parameters, delivering important information needed for large-scale implementation.

At the same time, WACKER and SLB-ACC JV conducted an engineering feasibility study as well, which involved drafting a design for a plant that would capture 180,000 metric tons of CO<sub>2</sub> annually. These calculations have now been supplemented with the data obtained in actual practice.

"The results of the pilot study are a huge success for us. We've shown that this technology makes it possible to remove  $CO_2$  effectively," says WACKER CEO Christian Hartel. Capturing carbon dioxide prevents its release into the atmosphere as a greenhouse gas. It can then be put to other uses, such as creating synthetic fuels (e-fuels) or synthesizing methanol as a starting material for other chemical processes.

Storing it underground (carbon capture and storage, CCS) is also an option. The project represents an important step on the road to closed carbon cycles. "What we need now are customers that will buy the  $CO_2$  from us and a regulatory framework that can help us build the business case," Hartel goes

on to say.

#### Net Zero by 2045

WACKER has set ambitious sustainability goals for itself. By 2030, the company's absolute greenhouse gas emissions are to be 50% lower (compared to 2020). By 2045, WACKER intends to achieve net zero, which means it would no longer emit any net  $CO_2$  whatsoever. Silicon production in Holla is a major piece of that puzzle.

The objective for this site is full CO<sub>2</sub>-neutral production. The energyintensive manufacturing processes here began running on 100% green electricity from sources such as hydroelectric power back in 2022. And the gradual switch from bituminous coal to biogenic sources of carbon is to be complete by 2030. Green electricity, sustainable carbon and carbon capture will one day make climate-neutral silicon value chains a reality.

The amount of carbon dioxide released during silicon production is the most critical factor in the carbon footprint of silicones. The use of  $CO_2$ -neutral metallurgical-grade silicon from Holla could significantly reduce the carbon footprint of the company's silicone products.

### **INDUSTRY NEWS**

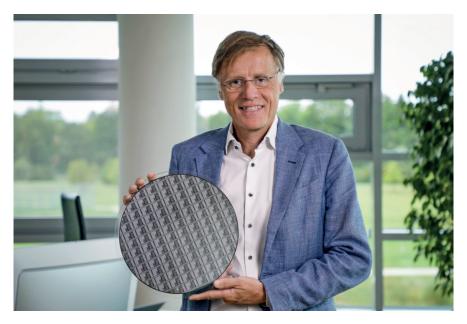

### An industry game-changer?

Infineon pioneers world's first 300 mm power gallium nitride (GaN) technology.

INFINEON TECHNOLOGIES has succeeded in developing the world's first 300 mm power gallium nitride (GaN) wafer technology. Infineon believes that it is the first company in the world to master this groundbreaking technology in an existing and scalable high-volume manufacturing environment.

The breakthrough will help substantially drive the market for GaN-based power semiconductors. Chip production on 300 mm wafers is technologically more advanced and significantly more efficient compared to 200 mm wafers, since the bigger wafer diameter offers 2.3 times more chips per wafer.

GaN-based power semiconductors find fast adoption in industrial, automotive, and consumer, computing & communication applications, including power supplies for AI systems, solar inverters, chargers and adapters, and motor-control systems.

State-of-the art GaN manufacturing processes lead to improved device performance resulting in benefits in end customers' applications as it enables efficiency performance, smaller size, lighter weight, and lower overall cost. Furthermore, 300 mm manufacturing ensures superior customer supply stability through scalability.

"This remarkable success is the result of our innovative strength and the dedicated work of our global team to demonstrate our position as the innovation leader in GaN and power systems," said Jochen Hanebeck, CEO of Infineon Technologies AG.

"The technological breakthrough will be an industry game-changer and enable us to unlock the full potential of gallium nitride. Nearly one year after the acquisition of GaN Systems, we are demonstrating again that we are determined to be a leader in the

fast-growing GaN market. As a leader in power systems, Infineon is mastering all three relevant materials: silicon, silicon carbide and gallium nitride."

Infineon has succeeded in manufacturing 300 mm GaN wafers on an integrated pilot line in existing 300 mm silicon production in its power fab in Villach (Austria). The company is leveraging well-established competence in the existing production of 300 mm silicon and 200 mm GaN.

Infineon will further scale GaN capacity aligned with market needs. 300 mm GaN manufacturing will put Infineon in a position to shape the growing GaN market which is estimated to reach several billion US-Dollars by the end of the decade.

This pioneering technological success underlines Infineon's position as a global semiconductor leader in power systems and IoT.

Infineon is implementing 300 mm GaN to strengthen existing and enabling new solutions and application fields with an increasingly cost-effective value

proposition and the ability to address the full range of customer systems. Infineon will present the first 300 mm GaN wafers to the public at the electronica trade show in November 2024 in Munich.

A significant advantage of 300 mm GaN technology is that it can utilize existing 300 mm silicon manufacturing equipment, since gallium nitride and silicon are very similar in manufacturing processes.

Infineon's existing high-volume silicon 300 mm production lines are ideal to pilot reliable GaN technology, allowing accelerated implementation and efficient use of capital.

Fully scaled 300 mm GaN production will contribute to GaN cost parity with silicon on R DS(on) level, which means cost parity for comparable Si and GaN products.

300 mm GaN is another milestone in Infineon's strategic innovation leadership and supports Infineon's mission of decarbonisation and digitalisation. We're about to change the game in the subfab

### 00.01 | project ganymede 2025

# Optogenetic OLED-on-CMOS stimulators for neurosensory therapies

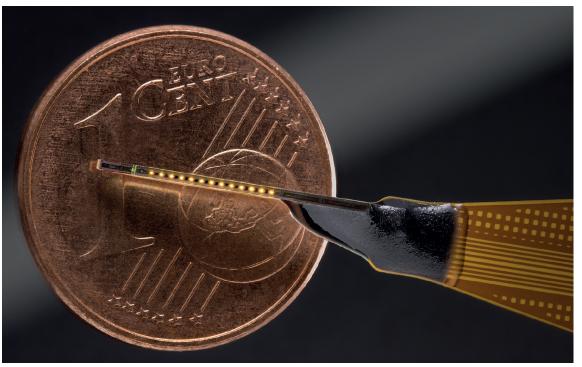

Researchers from the Fraunhofer Institute for Photonic Microsystems IPMS and the Max Planck Institute for Multidisciplinary Natural Sciences (MPI-NAT) have researched optical stimulators for future cochlear implants as part of the "NeurOpto" project (funded by the Fraunhofer-Max-Planck Cooperation Program: 601001).

OPTOGENETICS is a method that uses light to control genetically modified cells in living tissues. By introducing light-sensitive proteins into cells, their activity can be precisely turned on and off with light pulses. This technique is commonly used in neuroscience to study the functions of nerve cells and to activate or inhibit specific neuronal populations. To deliver light precisely to stimulate tiny cells, small and locally selective light sources are therefore needed now.

Dr. Uwe Vogel, Head of business unit "Microdisplays and Sensors" at Fraunhofer IPMS, explains: "With OLED-on-silicon technology, we can bring tiny, locally controllable light pixels onto a chip. This chip can be flexibly designed to reach the desired locations even in curved structures like the cochlea. This allows light to be used precisely where electrical stimulation alone is insufficient."

Prof. Tobias Moser from MPI-NAT adds: "The development of optical cochlear implants promises

better hearing for the severely hearing impaired. MPI-NAT and University Medical Center Göttingen (UMG) are working closely with partners such as Fraunhofer IPMS on the technological solutions required for this. Intelligent implantable stimulators based on optical stimulation could also be used for other medical therapies such as laryngeal pacemakers, cardiac pacemakers, pain relieve, retinal implants, or deep brain stimulation."

### How does optical cell stimulation work?

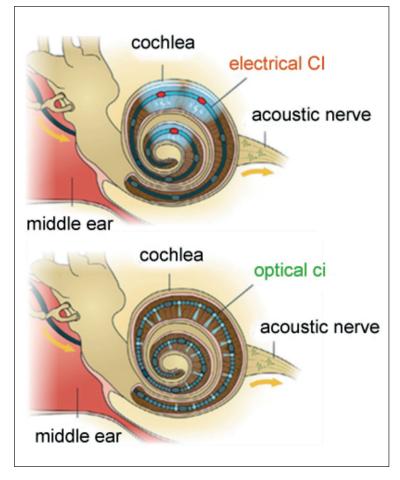

Current electrical cochlear implants (eCls) restore speech comprehension in quiet environments for most of the approximately 1 million users worldwide. However, speech recognition in background noise and enjoyment of music are often severely limited. The reason for this is the inadequate frequency resolution of electrical sound coding: each electrode contact also stimulates more distant nerve cells that code different frequencies due to the broad current spread. Since light can be controlled much more

> OLEDon-Silicon Technology for Optogenetics. © Fraunhofer IPMS precisely, an optical cochlear implant (oCl) could overcome this problem. The number of independent frequency bands could be increased by spatiallytargeted optical stimulation of light-sensitive auditory nerve cells (SGNs). This would be possible through dozens of microscale light emitters along the frequency axis of the cochlea, ideally individually controllable.

UMG/MPI-NAT have been working for many years with academic and industrial partners on the development of the oCl and gene therapy. The current collaboration with Fraunhofer IPMS focused on evaluating OLED technology for use in oCls. Fraunhofer IPMS has leveraged its experience from OLED-on-silicon technology for microdisplays to bring CMOS-integrated light sources of the highest pixel density and brightness, as well as the lowest power consumption, to a pixelated OLED microsensor that can individually control spatially distributed light channels assignable to corresponding audio frequencies in the cochlea via a serial interface.

### Where was the challenge in developing the technology?

Although Fraunhofer IPMS has already introduced unique features with its OLED-on-silicon technology for microdisplays that are also important for optogenetics, there are still some challenges: The necessary brightness and degree of integration have been successfully demonstrated during the project. However, flexibility and biocompatibility are not yet verified. The silicon microtechnology used has shown that these properties are generally achievable. With further research and development effort, they also appear feasible here.

### When will the technology be market-ready?

The project laid the first foundations for the use of OLED-on-silicon technology in optogenetics. The results are promising. The scientists will continue to work on this technology and remain open to other areas of application.

> Electrical vs. Optical Cochlea Stimulation - Above: The current from each of the 12 electrode contacts of a conventional electrical cochlear implant spreads widely. Below: The light from nearly one hundred independent micro-light-emitting diodes of an optical cochlear implant can be projected onto a small area.

## Dedicated webinars for the silicon semiconductor industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of Silicon Semiconductor, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 55,000 silicon semiconductor professionals.

Find out how Angel Webinar can help you organise and run a webinar within the silicon semiconductor industry.

Reach Educate Influence Brand Awareness

- Lead Generation

- Thought Leadership

Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

### Semiconductors:

### Unstoppable growth in a billion-dollar market

Both companies and governments are investing heavily in semiconductor technology to stabilise supply chains and meet demand through innovation drivers such as AI. An analysis of the market potential based on current figures.

#### BY PHILIPP SCHLÜTER, PARTNER M&A, PAVA PARTNERS GERMANY

THE INTERNATIONAL semiconductor industry has been at the centre of global attention during the significant supply chain disruptions between 2021 and 2022. What industry insiders have already been aware of for quite a while has now come to light: the semiconductor market is both complex and essential to the global industry.

According to analysis by IC Insights and Semiengineering.com, more than €190 billion has been invested in the semiconductor market in 2022 alone. A further USD 300 billion has been announced by leading semiconductor companies for the coming years.

By way of comparison, this is roughly equivalent to the amount the global automotive industry plans to invest in research and development by 2028, driven in particular by the megatrends of electrification and autonomous driving.

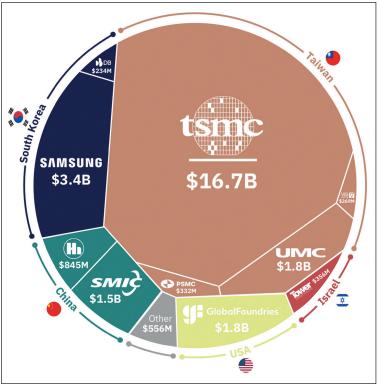

### Taiwan is the undisputed leader in semiconductor production

Government policy is also providing a boost. The supply chain problems during the pandemic and beyond have highlighted the fact that semiconductor chips are critical infrastructure. With the current shortage, politicians in Europe and the US have decided to boost local production again. As a result, billions of taxpayers' money are being pumped into establishing FABs. How badly subsidies are needed in the EU shows its positioning in the market. The world's top 10 semiconductor foundries show how far behind Europe is in chip production (Figure 1). Europe is only listed under 'others'. Unsurprisingly, Taiwan's semiconductor production is the undisputed leader. The chart from the latest Semicon Report illustrates Taiwan's immense lead.

The fact that industrial policy is now being implemented, and more subsidies are being channelled into semiconductor production, is an important sign for Europe and Germany in particular. Over the past 30 years, the region of Saxony and Saxony-Anhalt has succeeded in establishing the region as an attractive location for international players through the strategic development of production sites and expertise at universities and research centres.

An investment that has paid off, as confirmed by the international companies that have already settled in the region. However, the industry association ZVEI has criticised the fact that German funding is too selective and does not sufficiently support the entire semiconductor ecosystem.

So far, the association has criticised the fact that important sub-sectors such as printed circuit boards and electronic manufacturing services (EMS), which make the further processing of chips possible in the first place, have been excluded from the allocation of funding.

> The 'Semicon Landscape' in Figure 2 shows that the entire ecosystem, from materials to software, comprises more than 300 companies in new industrial sectors with various subgroups. European suppliers are particularly strong in mechanical engineering, as well as in the design and manufacture of chips for sensors and power electronics.

### MARKET TRENDS | SEMICONDUCTORS

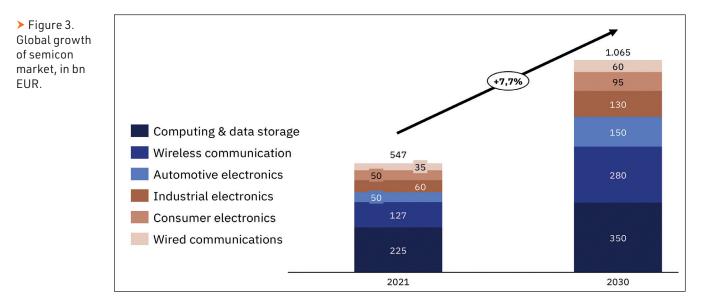

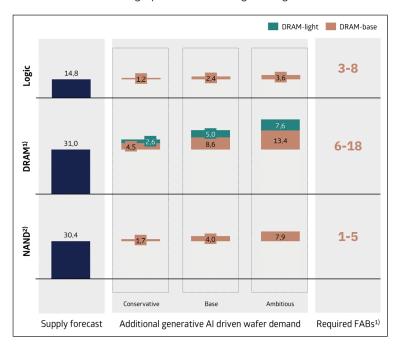

Artificial intelligence drives demand for chips However, a look at the main drivers of growth in the semiconductor industry shows that the market is set for strong growth in the future. Data storage, wireless communications and automotive electronics are the biggest growth drivers in the semiconductor industry, accounting for more than 70 percent of the sector's growth (Figure 3). In particular, the electrification of the automotive industry and advances in autonomous driving are driving growth, as is the expansion of the Internet of Things in industrial and consumer environments. The future topic of artificial intelligence, in particular Generative Artificial Intelligence (GenAI), which has achieved enormous leaps in innovation in a very short period of time, is increasing the demand for intelligent chips to an unprecedented extent. According to current analyses, the demand for logic chips for GenAl applications will increase to up to 3.6 million additional wafers (Fig. 4). Meeting this demand will require a corresponding increase in production capacity, requiring up to eight new FABs by 2030.

The graph in Figure 4 also clearly shows that NAND and DRAM chips in the tens of millions will be needed in the memory technology sector. This demand is primarily driven by the increasing requirements for computing power and the increasing rack density in specialised data centres as a result of the growing number of complex GenAI

> Figure 1. Data based on Q1 2023 revenue in USD.

| MATERIAL                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S                             | EMICAP                                       |                                                                                                                                                                                |                        |  |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| SI SIC GAN                                                                                         | SCHOTT WACKER<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>CONSTRUCTION<br>C |                               | BACKEND<br>ASMPT STATE                       | DITENT                                                                                                                                                                         | Anter SLM SENTECH      |  |

| FAB                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |                                              |                                                                                                                                                                                |                        |  |

| ALLIS EASI & CobalFoundries washed                                                                 | PCB / EMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ELES SPIO                     | SWINDON<br>IN CON MININ                      |                                                                                                                                                                                |                        |  |

| DESIGN                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |                                              |                                                                                                                                                                                |                        |  |

|                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               | nextchip                                     |                                                                                                                                                                                | prodesign              |  |

| AUTOMOTIVE<br>KIOXIA NP 57 (Micron Diese Kioxia NP) 57 (Micron Diese Kioxia NP) 57 (Micron Hitachi | COMMUNICATIONS<br>Micron BROADCOM<br>SKYWORKS KIOXIA DAWA 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               | Cron Tower sk hynix                          | INDUS<br>57 NIGO 🦛 💦                                                                                                                                                           |                        |  |

| STANFORS WORSDOOL BINOS                                                                            | CIMUR CREONIC SAPWAYES DIROCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               | Silicon Line<br>Dis Generation Ele cognetied | CIMUN / motomation                                                                                                                                                             |                        |  |

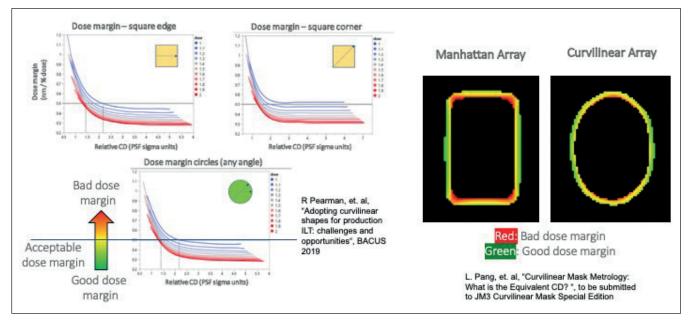

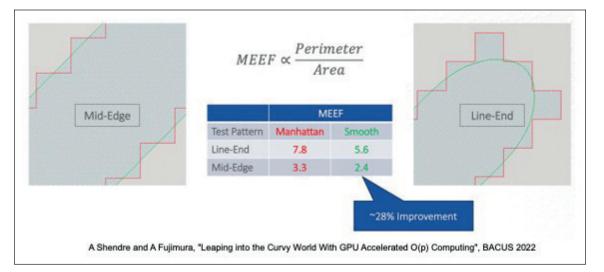

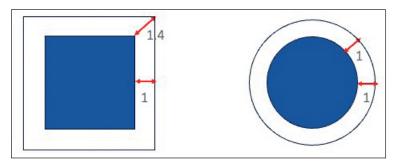

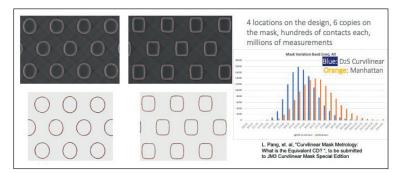

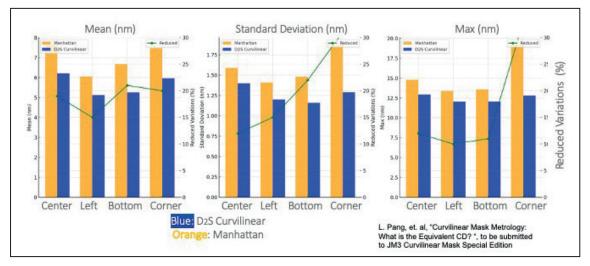

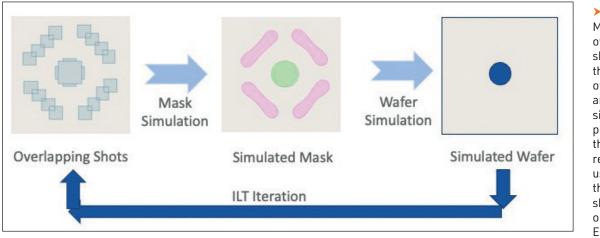

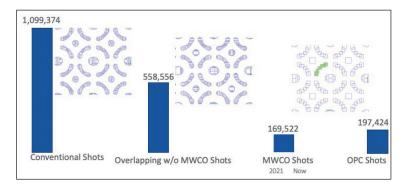

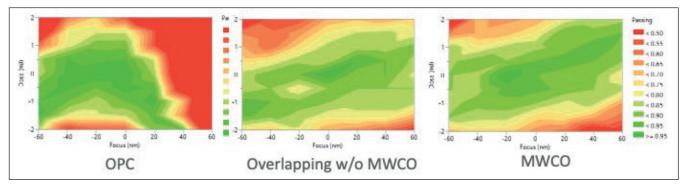

|                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               | tion                                         | GRAPHCORE                                                                                                                                                                      | V TEXAS<br>INSTRUMENTS |  |