VOLUME 46 ISSUE VIII 2025

SILICONSEMICONDUCTOR.NET

# Powerful inspection solutions for wafer and chip level packaging.

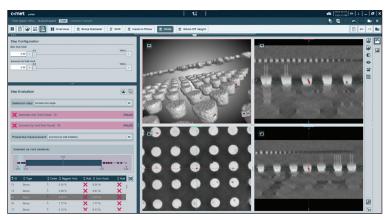

From root cause analysis in the lab, to fast process analysis in the fab, Comet's leading 2D and 3D X-ray technology provides powerful inspection solutions for wafer and chip level packaging, enhanced with incredible Al-based software.

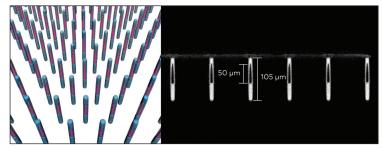

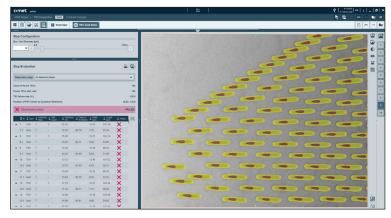

Visualization of 3D X-ray inspection results of TSV fills in a wafer. Wafer designed for Comet by Fraunhofer IZM\_ASSID, it contains voids for illustrative purposes.

Visit us in Munich! SEMICON Europa Booth #C2.513

Contact us to learn more, or explore our entire portfolio

yxlon.comet.tech

# BY PHIL ALSOP EDITOR

# Robotaxis and the AI opportunity: sorting the hype from the reality

A couple of recent episodes have served to highlight for me the continuing excitement and uncertainty that surrounds the future of our digital world as Al looms ever larger.

I was lucky enough to travel to Phoenix for the recent SEMICON West event, which seems to have been universally acknowledged as the biggest and best of these events for quite some. It will be interesting to see where else this event will visit in the coming years, or if San Francisco and Phoenix will remain the alternate year homes for some time to come.

Anyhow, arriving late on the Sunday, we had a day's leisure on the Monday, the day before the event, and so my colleague, Shez, and I decided to visit one of the out of town shopping malls. Uber ordered, and excitement from Shez as he realized that a Waymo robotaxi would be picking us up from our breakfast location. From the picking us up, the journey and the arrival at our destination the whole experience seemed faultless, although when I WhasApped my wife during the ride, she did scream at me to 'get out now'!!

For the rest of our stay, Shez summoned Waymos via their app and it all seemed very normal and safe.

Pre this direct experience of robotaxis, I was extremely sceptical as to the future of the driverless vehicle, but I am now a convert to the technology — although not quite as big a fan as Shez, who can't wait for them to arrive in the UK next year and seems likely to start up the first official Waymo fan club!

I shall leave the profound implications of the driverless vehicle future for another time, but there seems little doubt that robotaxis and fully autonomous vehicles for private citizens are here to stay.

Episode number two, a recent interview with a power grid expert who opined, with sound reasoning, that, in the UK at least, the required data centre capacity for AI – training and

inferencing – may well be somewhat over-estimated. The suggestion being that there are many data centre owners/ operators chasing the same business, so the size of the anticipated market is significantly exaggerated. The good news would seem to be that the energy required to power the AI era is not nearly as much as currently anticipated. The less good news...maybe the number of chips, power electronics solutions and the like required to support the AI explosion will not be as high as currently expected.

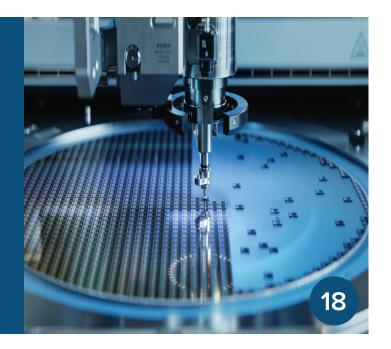

Add in the ongoing geopolitics and the impact of tariffs – actual and threatened – and the semiconductor industry continues to face an exciting, if volatile, future. And if Al numbers do dip, then the autonomous vehicle market could just make up some of this shortfall.

I'll spare you my Third Man/Harry Lime quote about Italian turmoil leading to the renaissance and hundreds of years of peace in Switzerland leading to the cuckoo clock (I paraphrase somewhat), but there's no doubt that the pace and scope of innovation in our industry is increasing to meet the challenges of our time.

For your free weekly e-news roundup go to: siliconsemiconductor.net

# **COVER STORY**

# Trends and drivers for next-generation process vacuum

Edwards Vacuum examines several emerging production processes with an eye towards identifying trends that will drive the development of next-generation vacuum systems.

# 14 Global 300mm fab spending expected to total \$374 billion

In its latest 300mm Fab Outlook, this robust investment reflects fab regionalization and surging Al chip demand for data centers and edge devices.

# 24 Imec lights the path to utility scale for Dirag's quantum chips

Silicon qubits made using advanced industrial manufacturing methods have met key performance criteria, paving the way to mass production of functional quantum computers.

# 26 Checking the quality of materials just got easier with a new AI tool

Acting as a "virtual spectrometer," SpectroGen generates spectroscopic data in any modality, such as X-ray or infrared, to quickly assess a material's quality.

# 28 Imec achieves milestones in single patterning High NA EUV lithography

imec's High NA EUV ecosystem is pushing the boundaries of High NA EUV patterning technology to A10 and beyond logic nodes.

# 30 Metrology for the 2 nm era

Infinitesima bets on high-speed atomic force microscopy to keep advanced silicon on track

# 32 iDEAL charts a new course for silicon

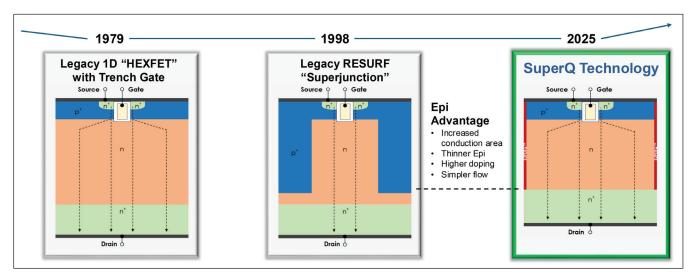

Will the latest MOSFET from iDEAL Semiconductor redefine silicon chip performance?

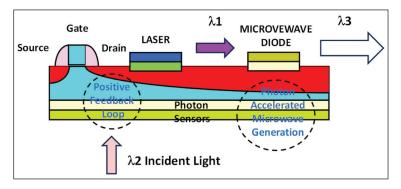

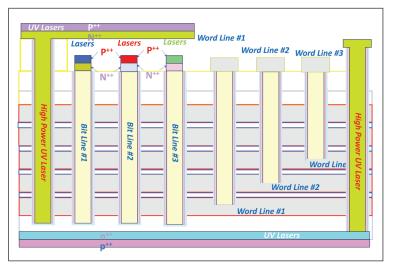

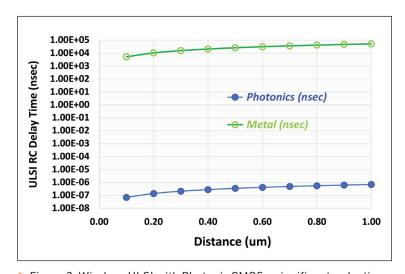

# 34 CMOS: Not just for silicon

While CMOS may be synonymous with the manufacture of silicon ICs, it's a versatile process can also be applied to the production of photonic and microwave circuits employing compound semiconductors

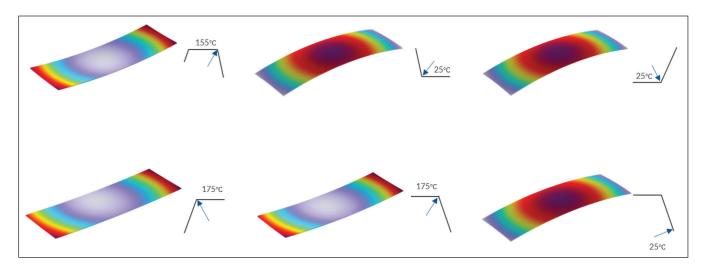

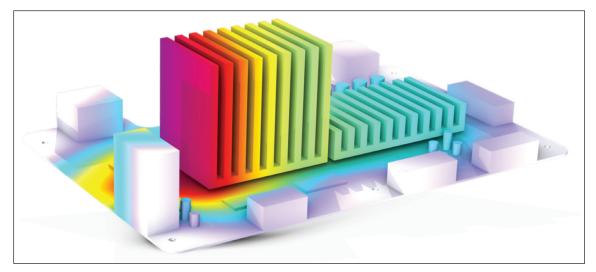

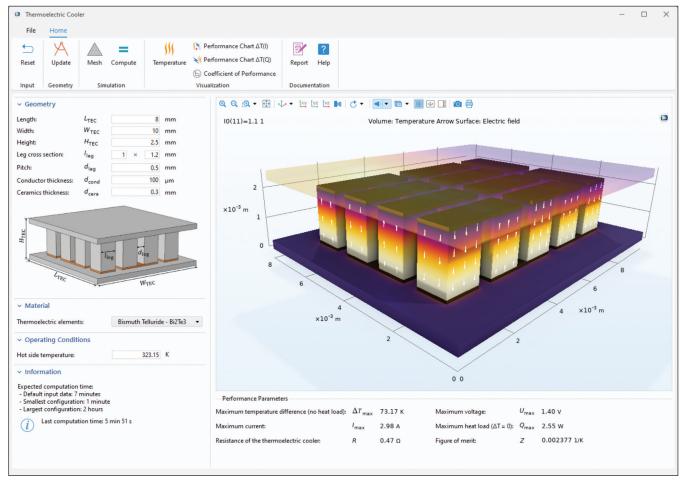

# 38 Targeting packaging pain points with multiphysics simulation

Multiphysics simulation can be used in semiconductor packaging to predict performance and ensure packaging reliability.

# 42 Al enables co-optimisation of devices and materials

In an interview with Silicon Semiconductor, Vijay Narasimhan, Director of R&D Collaboration, EMD Electronics, the North American electronics division of Merck KGaA, explains how AI for materials discovery.

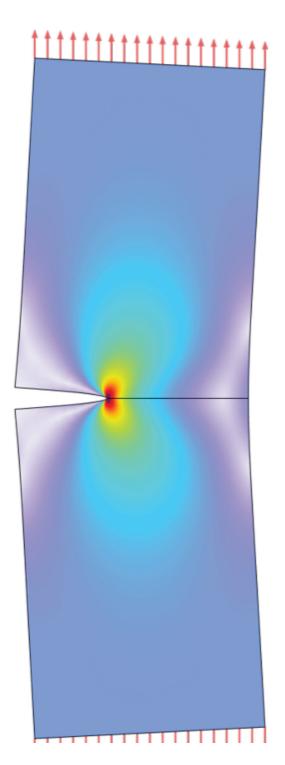

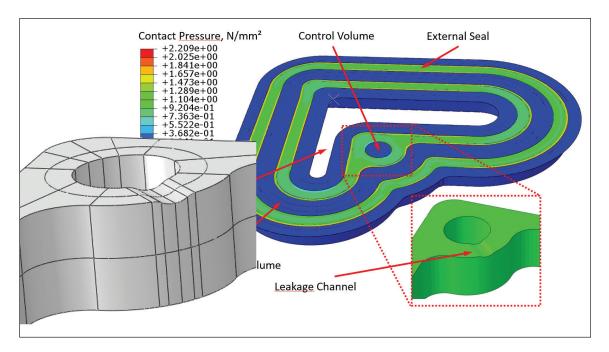

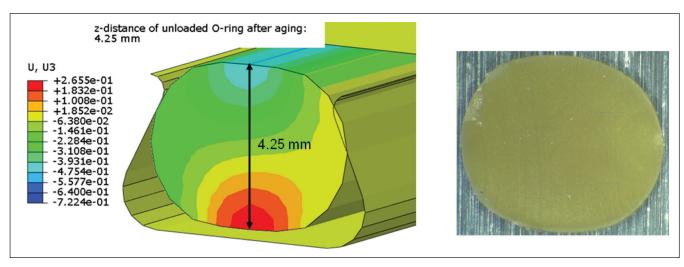

# 48 Simulation-driven engineering optimises sealing performance

The semiconductor industry operates under extreme precision requirements where even microscopic failures can result in significant yield losses and costly downtime.

# 52 Why the automotive industry is the perfect use case for Al

When it comes to everyday life, artificial intelligence is already changing the world around us; if the most ambitious predictions are correct, it promises to transform our lives even further

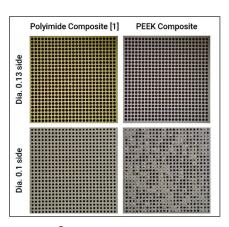

# 54 Next generation polyimide material for test socket applications

We live in an age seemingly defined by advancement in artificial intelligence technologies. To meet the demands of these cutting-edge developments, microchip architecture is rapidly increasing in complexity

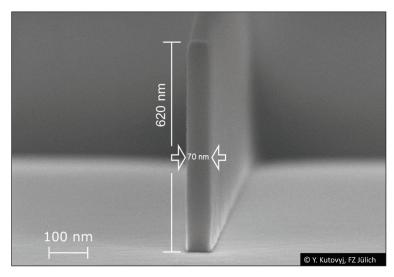

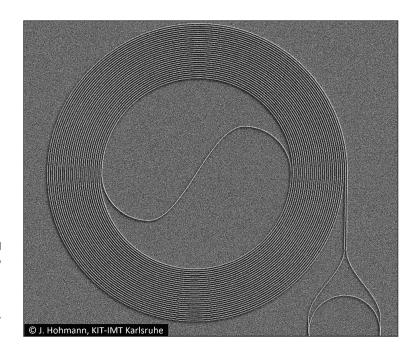

# 56 Inorganic resists redefining standards in electron beam lithography

Demands for resolution, process stability, and material performance are continuously increasing. In electron beam lithography, conventional polymer-based resists are reaching their physical limits.

# **NEWS**

- 06 US-China trade war drives investment in domestic rare earth supply

- 07 TechInsights announces 2026 Semiconductor Market Outlook Report

- 08 Bosch, Volkswagen, Nokia and Europe's Tech Giants unite to secure photonics future in FP10

- **09** The Robotaxi race is heating up globally

- 10 ESIA discusses Europe's semiconductor future

- 11 Vacuum-sealed semiconductor tray market to hit \$2.3 billion by 2033

- 12 Semicon Coalition & industry: a united front to power Europe's semiconductor future

Publisher Jackie Cannon Editor Phil Alsop Sales & Marketing Manager Shehzad Munshi Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams

phil.alsop@angelbc.com shehzad.munshi@angelbc.com sharon.cowley@angelbc.com mitch.gaynor@angelbc.com sukhi.bhadal@angelbc.com scott.adams@angelbc.com

+44 (0)1923 690205

+44 (0)1923 690215

+44 (0)1923 690200

+44 (0)1923 690214

+44 (0)2476 718970 +44 (0)2476 718970 Directors Jackie Cannon, Sharon Cowley

Published by Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road Coventry CV5 6SP, UK.

T: +44 (0)2476 718 970 E: info@angelbc.com

Silicon Semiconductor is published ten times (6x print and 4x video issues) a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00 per annum (UK) . €60.00 per annum ( Europe), \$90 per annum (air mail)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2025. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Silicon Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise. Printed by: The Manson Group, ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2025.

# US-China trade war drives investment in domestic rare earth supply

Rare earth elements and critical minerals are now frequently featured in global news cycles due to the national security and economic impacts of increasing supply disruption.

Growing export restrictions placed on defense-related rare earth materials from China at a time of multiple international conflicts underscores growing demand in the US and Europe to develop alternative supply.

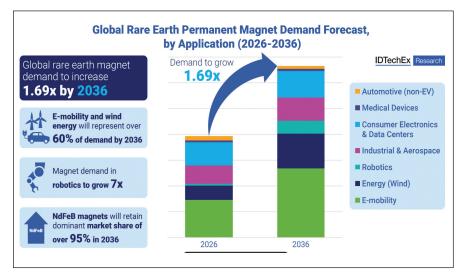

2025 is set to be an inflection point, as a year of tariffs and trade wars drive record investment into strategic Western rare earth supply chains. IDTechEx's latest research, 'Rare Earth Magnets 2026-2036: Technologies, Supply, Markets, Forecasts' explores rare earth investment and supply chain partnership trends driven by increasingly restrictive global rare earth supply.

China's latest export restrictions on critical rare earth elements applies yet more pressure to what are already tightly controlled materials. The latest round of restrictions extends to erbium, europium, holmium, thulium, and ytterbium, targeting defense and semiconductor chip applications. This announcement follows controls placed on neodymium magnet materials in April 2025, which sent the automotive industry scrambling for alternative supply and notably caused Ford to temporarily shut down some of its production plants.

Market disruption caused by export restrictions is unavoidable due to a lack of alternative rare earth sources and an absence of viable alternative materials in many integrated applications. China mines 69% of rare earth minerals, processes 88% of rare earth concentrates, and refines 90% of rare earth metals globally, with limited additional capacity available from other regions. On the demand side, rare earth magnets remain a dominant technology in applications such as high performance electric motors. Despite developments in rare earth-free motor technologies, IDTechEx forecasts that over 70% of electric vehicle motors will

rely on rare earth permanent magnets over the next decade.

The US is the first (and best positioned) player addressing rare earth supply risks, announcing significant public investment into domestic production. In July 2025, the US Department of Defense (DoD) entered a public-private partnership with MP Materials, North America's only major rare earth mine. The partnership includes capital investment of over \$400M and important rare earth purchase price commitments to ensure the mine's profitable operation.

The US is in a strong position to leverage its established rare earth mining base to expand downstream refining and production capacity, with investment and partnership trends beginning to reflect this. USA Rare Earths announced it will acquire UK-based rare earth refiner Less Common Metals for approximately \$220M, securing supply of crucial feedstock for its planned 5,000 tonne magnet production facility in Stillwater, Oklahoma. In August, Noveon Magnetics also announced a multi-year supply agreement with General Motors

to deliver rare earth magnets for its SUVs and trucks. The US rare earth ecosystem is moving fast to capitalize on its key advantage: the potential to insulate every supply chain stage from external dependence on China and mitigate the impact of future export controls.

The European rare earth market looks to be keeping pace with the US, despite the absence of established domestic rare earth mines. Frenchbased Carester has secured €216M in financing from the French government and Japanese investors to build its separation plant capable of processing 5,000 tonnes of mineral concentrates and 2,000 tonnes of recycled magnets annually. Carester will join Solvay to offer separated rare earth products to European magnet producers Vacuumschmelze and Neo Performance Materials Silmet, the latter of whom began magnet production at its site in Estonia in 2025. Without primary mineral supply within Europe, the key to success will be securing offtake agreements with external partners while developing new secondary rare earth sources, such as recycled waste magnets and mining tailings.

# TechInsights announces 2026 Semiconductor Market Outlook Report Series

Reports provide forward-looking insight into the state of the semiconductor sector across a number of technologies and markets.

TechInsights has released its 2026 Outlook Report Summary that covers key technology and vertical market trends and forward-looking expectations for next year.

According to David MacQueen, TechInsights' director, executive insights, "Datacenters will continue to drive growth in 2026, particularly for accelerators and processors and support for large language models (LLMs), resulting in a bottleneck for power. Despite on-device inference benefits like lower costs, power efficiency, and privacy, cloud Al will be the key market driver, and the shift to autonomous edge machines will not become a mass-market trend in 2026."

The industry will reach a pivotal moment in 2026 as it transitions from FinFET to gate-all-around (GAA) transistors with next-generation 2nm manufacturing processes, promising lower power consumption and improved performance. High-bandwidth memory (HBM), the most high-margin memory product ever, used almost exclusively for artificial intelligence (AI) accelerators, continues to drive the memory market upward. In the future, it could be replaced by high-bandwidth Flash (HBF) memory; TechInsights expects to see the release of HBF prototypes in 2026. Additionally, next year promises to be the inflection point for silicon photonics, in the form of co-packaged optics (CPO), and glass substrates, which help to improve data transfer performance while addressing heat dissipation and power usage.

"The rapidly shifting technology landscape seems almost slow compared to the pace of change happening at a global political level, with tariffs and trade restrictions creating a fluctuating business environment," MacQueen added. "The industry will have to navigate an increasingly fractious and fragmented geopolitical landscape. Tariffs and export restrictions, particularly affecting trade involving the US and China, are more likely to escalate than abate in 2026."

TechInsights will release its semiconductor market outlook report series, which covers memory, advanced packaging, artificial intelligence (AI), automotive, PC/laptop, mobile and more, from October through November, according to the release schedule below. The TechInsights Outlook

Summit Webinar Series will provide attendees with a summary of the reports and will be held from October 15, 2025 through January 21, 2026.

Access all reports for free here. The 2026 Market Outlook Report release schedule is as follows:

- LIVE: Advanced Packaging report release

- O LIVE. Memory report release

- LIVE. Al report release

- LIVE: Compute report release

- LIVE: Power report release

- LIVE: Sensor report release

- Oct. 22: Automotive report release

- Oct. 29: Manufacturing report release

- Nov. 5: PC/Laptop report release

- Nov. 5: Connectivity report release

- O Nov. 12: Mobile report release

- Nov. 19: Consumer electronics report release

The rapidly shifting technology landscape seems almost slow compared to the pace of change happening at a global political level, with tariffs and trade restrictions creating a fluctuating business environment

# Bosch, Volkswagen, Nokia and Europe's Tech Giants unite to secure photonics future in FP10

Bosch, Volkswagen, Nokia, ZEISS, TRUMPF and other industry giants urge the EU to create a €2 billion photonics programme in FP10.

SOME of Europe's biggest industrial names, including Bosch, Volkswagen, Mercedes-Benz, Nokia Bell Labs, ZEISS, TRUMPF, and EssilorLuxottica, have joined forces to urge the European Commission to place photonics at the heart of the next EU Framework Programme (FP10).

In a Joint Statement released, leaders from across Europe's defence, automotive, healthcare, manufacturing, and telecoms sectors warn that without a bold and dedicated strategy, Europe risks falling further behind China and the US in the global race for photonics – the light-based technologies that underpin 20% of the EU economy.

With FP10 set to shape Europe's research and innovation agenda for 2028–2034, industry leaders argue that only a dedicated programme can ensure Europe's photonics sector remains globally competitive – powering breakthroughs in Al, quantum, energy, healthcare, mobility, and beyond.

"Photonics is the invisible force behind everything from AI and quantum computing to secure communications, energy, healthcare, defence, and mobility," said Dr Lutz Aschke, President of Photonics21.

"But Europe is at risk of losing its critical, competitive edge unless FP10 delivers a stand-alone €2 billion photonics programme, capable of unlocking €6-8 billion in industrial coinvestment."

The signatories stress that photonics is one of the few digital technologies where Europe has long been a leader, but warn that China's share of the global photonics market has surged

from 10% in 2005 to 32% in 2022, while Europe's has slipped to 15%.

"Photonics is a strategic technology for Europe's prosperity, autonomy, and security. This joint statement shows that Europe's industrial leaders stand united," said Dr Aschke.

The joint statement calls on the EU to:

- Establish a €2 billion stand-alone photonics programme under FP10.

- Launch Photonics Grand Challenge Proposals in fields such as Al, space, quantum, and defence.

- Strengthen resilient European supply chains for critical photonics components and materials.

The request brings together voices from across the European economy – from defence leaders such as Diehl Defence and WB Electronics, to automotive innovators at Volkswagen, Scania, and Mercedes-Benz, to healthcare pioneers ZEISS and EssilorLuxottica, and research powerhouses Nokia Bell Labs and ams-OSRAM.

Specialists with 30 year+ pedigree and in-depth knowledge in overlapping sectors

Expertise: Moderators, Markets, 30 Years + Pedigree

Reach: Specialist vertical databases

Branding: Message delivery to high level influencers via various in house established magazines, websites, events and social media

## For more information contact:

Jackie Cannon T: 01923 690205 E: jackie@angelwebinar.co.uk W: www.angelwebinar.co.uk T: +44 (0)2476 718 970 E: info@angelbc.com W: www.angelbc.com

# The Robotaxi race is heating up globally in 2025

2025 has been a massive year so far for SAE level 4 autonomous vehicles, including the first foray outside of robotaxis.

MARKET INTELLIGENCE firm IDTechEx's report, "Autonomous Driving Software and AI in Automotive 2026-2046: Technologies, Markets, Players", analyzes the progress of robotaxi services to date, and forecasts the software revenue attributed to robotaxis up to 2046, split by region. The role of these different players and their approaches are analyzed, compared, and used to forecast the overall autonomous driving software market.

#### Increased competition in the US

Waymo has established itself as the leader of robotaxi services, operating in Phoenix, San Francisco, Los Angeles, Atlanta, and Austin, and has even established partnerships with Uber and Lyft, the two major ride-hailing companies, which could be considered competitors to Waymo's business model. With testing being done in Tokyo, it has also recently begun its first activities in international markets.

Tesla launched its robotaxi service in June 2025 and later increased its operational area to approximately 170 square miles in Austin, Texas. In September, these rides were opened to the public, and no longer have an onboard human supervisor, while maintaining the remote operators that all robotaxis have. However, more time is required to ascertain whether the technology is mature enough to scale.

Two other companies have opened robotaxi services in the US this year: Zoox and May Mobility. Unlike other companies, Zoox's robotaxi has been built from the ground up to be an autonomous vehicle. While Waymo's robotaxis are currently retrofitted Jaguar I-PACEs, and Tesla uses its Model Y, Zoox's robotaxi doesn't have a steering wheel, pedals, or a driver's seat. May Mobility began operating a robotaxi pilot program in September 2025 in collaboration with Lyft,

using modified hybrid Toyota Sienna minivans. Since the exit of Cruise in December 2024, the only company operating robotaxis commercially was Waymo. In the past two months, the activities of other companies suggest that robotaxis could be set to take off. IDTechEx forecasts that by 2046, the US will make up almost a quarter of the software revenue from the robotaxi market globally.

# China's Market Continues to Grow, Europe Will Expand

With the second-largest population in the world, the addressable market for robotaxis in China is massive. In terms of scale, Waymo's only current competitor is from Apollo Go, owned by technology giant Baidu. Apollo Go is operational in over twelve Chinese cities, including Beijing, Shanghai, Shenzhen, and Wuhan. With a fleet of over one thousand vehicles, it has indicated its intention to serve foreign markets, targeting the UK and Germany by 2026. Considering the current state of the European market and the activities of European companies such as Wayve and Motor AI, Europe could become a key battleground for technology superiority in the future.

The domestic market also has players with hundreds of vehicles, such as Pony.ai and WeRide, and upcoming companies such as Momenta and Black Sesame that are developing autonomous vehicle technology.

With such a competitive domestic market, IDTechEx expects China to make up over half of the robotaxi software revenue in 2046.

Another player, AutoX, has come out with the world's first private SAE level 4 autonomous vehicle, under the new brand name Tensor. Under the name AutoX, the US-based company closed its robotaxi service in China two years ago. It remains to be seen whether this vehicle will enter the market, what it would cost, and how it would handle different responsibilities and liabilities associated with a private autonomous car.

IDTechEx's projections for software revenue from autonomous vehicles over the next twenty years, by region. Source: Autonomous Driving Software and AI in Automotive 2026-2046: Technologies, Markets, Players.

# ESIA discusses Europe's semiconductor future

Semiconductor leaders unite to shape the next policy framework in support of Europe's chip ambitions.

THE EUROPEAN SEMICONDUCTOR INDUSTRY ASSOCIATION (ESIA) recently hosted a high-level policy event in Brussels, bringing together key voices from industry and government to discuss the future of Europe's semiconductor strategy. The event, entitled "Next-level policy blueprint for Europe's chip ambitions", marked a timely intervention as the review of the EU Chips Act officially gets underway.

Frédérique Le Grevès, STMicroelectronics EVP Public Affairs Europe and President of ST France, who serves as Vice-President of ESIA, declared: "Europe has the technologies, the talent, and the ambition to lead in key segments of the semiconductor industry in Europe – but we must move faster

The revision of the EU Chips Act is an excellent chance for the EU to develop a vision for an industrial strategy and implement it in a way

that strengthens the European semiconductor ecosystem. Europe's strengths – in sensors, microcontrollers, power semiconductors, edge AI align perfectly with the needs of key end markets such as Al infrastructure and applications, automotive, factory automation, robotics, connectivity, energy infrastructure, aerospace, and defence. If a second EU Chips Act helps us scale those strengths, we will be in a better position to lead in key technologies underpinning the next wave of global growth." During the high-level event, policymakers, industry leaders, and stakeholders engaged in a forward-looking dialogue on how the semiconductor ecosystem in Europe can be strengthened. The event featured keynote speeches from Member of the European Parliament Matthias Ecke (Socialists & Democrats, Germany), and Dr Andreas Schumacher, Executive Vice-President and Head of Strategy, M&A at Infineon Technologies.

The subsequent panel discussions explored how Europe's semiconductor policy framework must evolve to meet the challenges of global competition, technological sovereignty, and supply chain resilience. It featured perspectives from the manufacturing side through Ms Le Grevès, as well as up- and downstream views from CEA-Leti Chief Executive Officer Sébastien Dauvé and Pierre Millette, Chief Technology Officer at the European Automobile Manufacturers' Association (ACEA). Furthermore, Dr Tim Schulze, Senior Policy Officer

at the German Federal Ministry for Economic Affairs and Energy, provided policymakers' insights from the EU's most populous Member State. Discussions focused on the need for a more agile, innovation-driven approach that supports both industrial growth and strategic autonomy.

The event concluded with closing remarks from Pierre Chastanet, Head of Unit for Microelectronics and Photonics at the European Commission, who reaffirmed the Commission's commitment to working closely with stakeholders to shape the next phase of semiconductor policy. As Europe revisits its Chips Act, ESIA's event served as a timely exchange for aligning public and private sector ambitions, ensuring that the continent remains competitive and resilient in a rapidly evolving global landscape.

During the high-level event, policymakers, industry leaders, and stakeholders engaged in a forward-looking dialogue on how the semiconductor ecosystem in Europe can be strengthened. The event featured keynote speeches from Members of the European Parliament, and Infineon Technologies

# Vacuum-sealed semiconductor tray market to hit \$2.3 billion by 2033

According to Research intelo, the Global Vacuum-Sealed Semiconductor Tray market size was valued at \$1.2 billion in 2024 and is projected to reach \$2.3 billion by 2033, expanding at a robust CAGR of 7.5% during the forecast period of 2025–2033.

THE primary growth driver for the vacuum-sealed semiconductor tray market globally is the surging demand for advanced semiconductor packaging solutions, propelled by rapid advancements in consumer electronics, automotive electronics, and industrial automation.

As the semiconductor industry continues its transformation to support next-generation devices with higher precision and reliability, vacuum-sealed trays have become indispensable for safe wafer handling, chip packaging, and component storage. This market is witnessing increased investments in automation and material innovation to ensure contamination-free transportation and storage of sensitive semiconductor components, thereby fueling sustained growth worldwide.

The global semiconductor industry continues to grow rapidly, driven by rising demand for consumer electronics, automotive electronics, and advanced computing systems. As chips become smaller, more complex, and highly sensitive, protecting them during transportation and storage has become a critical challenge.

This is where vacuum-sealed semiconductor trays play a pivotal role. Designed to provide a controlled environment, these trays prevent contamination, moisture intrusion, and electrostatic damage, thereby ensuring chip reliability and performance.

The vacuum-sealed semiconductor tray market is witnessing steady expansion as manufacturers and suppliers align with the needs of semiconductor fabrication plants, assembly units, and packaging facilities. The growing focus on efficiency, sustainability, and advanced packaging technologies is further shaping the market landscape.

#### **Key Drivers**

Miniaturization of Semiconductors

The shift toward smaller and more

powerful chips, such as those

used in smartphones, wearables,

and IoT devices, has increased the

vulnerability of components. Vacuumsealed trays safeguard these delicate

semiconductors from dust, static, and

oxidation.

## **Rising Global Chip Demand**

With the semiconductor shortage exposing supply chain vulnerabilities in recent years, manufacturers are investing heavily in protection and logistics solutions. Vacuum-sealed trays ensure that chips reach their destinations without compromising quality.

#### **Adoption in Automotive Electronics**

The automotive industry's shift toward electric vehicles (EVs), autonomous systems, and advanced driverassistance systems (ADAS) has spurred demand for high-reliability semiconductors. To maintain consistent quality standards, vacuum-sealed trays are becoming a crucial packaging solution.

#### Challenges

Despite promising growth, the market faces challenges such as high production costs and the need for customization. The design of trays varies based on chip type, size, and packaging style, making it difficult

for manufacturers to standardize production. Additionally, the increasing emphasis on eco-friendly materials poses challenges for companies reliant on plastics and non-recyclable materials.

#### **Technological Advancements**

Technological innovation is reshaping the vacuum-sealed semiconductor tray market. Modern trays incorporate: Electrostatic Discharge (ESD) Protection: Many trays are designed with conductive or dissipative materials to prevent electrostatic buildup, which can damage semiconductor circuits.

## Moisture Barrier Films: Advanced

sealing technologies ensure chips are shielded from humidity, crucial for devices used in medical and aerospace industries.

#### **Automation-Friendly Designs:**

Trays compatible with robotic handling and automated assembly lines streamline production and reduce operational errors.

The future of the vacuum-sealed semiconductor tray market looks promising, fueled by:

Growth of Al and IoT Devices: As billions of connected devices hit the market, the demand for semiconductors and consequently secure packaging will rise.

#### Sustainable Packaging Trends:

Companies are exploring recyclable and biodegradable tray materials, aligning with global sustainability goals.

# Expansion of Global Semiconductor Supply Chains:

As governments and corporations invest in new fabs, tray manufacturers will find growing opportunities worldwide.

# Semicon Coalition and industry: a united front to power Europe's semiconductor future

In a clear signal of unity and shared ambition, the 'Semiconductor Coalition Europe' has unveiled its Joint Declaration that seeks to strengthen and revitalise Europe's position in the global semiconductor industry

ALONGSIDE a broad alliance of semiconductor industry leaders issued its Endorsement, calling for bold action, proper preconditions, and a market-driven business case for Europe.

On the sidelines of the EU

Competitiveness Council meeting, the

Semiconductor Coalition Europe (or

Semicon Coalition), supported by the

EU Member States, presented their

Declaration calling for a revised EU

Chips Act, a little over six months since

the initial formation and first Common

Statement.

Their message is clear: semiconductors are vital to our society, our competitiveness, and our security. Also in attendance supporting this pivotal initiative was a broad alliance of over seventy semiconductor companies, industry associations, and research & technology organisations (RTOs) spanning the European and global value chains that have joined forces to back the Coalition's vision.

The signatories of the Industry Endorsement welcome and support the Coalition's initiative and urge them to immediately start the

process of defining clear goals that are underpinned with a measurable execution strategy and developed in closest partnership with industry. More concretely, the undersigned call for bold action and clear ownership from the European Commission and Member States, the establishment of necessary regulatory, societal, and economic pre-conditions, and the development of a compelling, market-driven business case by the end of 2025.

As global demand for semiconductors accelerates, Europe's future competitiveness will de-pend on timely, coordinated action among public authorities and private players to address sector challenges and align industrial strategy with market needs.

ESIA urges the European Commission and EU Member States to immediately launch the necessary process to turn these ambitions into concrete results

# Dedicated webinars for the silicon semiconductor industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of Silicon Semiconductor, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 55,000 silicon semiconductor professionals.

Find out how Angel Webinar can help you organise and run a webinar within the silicon semiconductor industry.

- Brand Awareness

- Lead Generation

- Thought Leadership

Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

# HYBRID AND FUSION BONDING FOR HETEROGENEOUS INTEGRATION

- Enabling advanced 3D device stacking and chiplet integration for CMOS image sensors, memory and 3D system-on-chip (SoC)

- High-volume production equipment and process technology for Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding

- GEMINI® FB Automated Production Wafer Bonding System delivers industry leading alignment accuracy and bonding performance

- Heterogeneous Integration Competence Center™ serving as leadingedge innovation incubator for EVG customers and partners

VISIT US AT BOOTH #B1241

SEMICON®

EUROPA

**GET IN TOUCH** to discuss your manufacturing needs **www.EVGroup.com**

# Global 300mm fab equipment spending expected to total \$374 billion over next three years

In its latest 300mm Fab Outlook, this robust investment reflects fab regionalization and surging Al chip demand for data centers and edge devices, while underscoring the growing commitment to semiconductor self-sufficiency across key regions through localized industrial ecosystems and supply chain restructuring.

WORLDWIDE 300mm fab equipment spending is expected to surpass \$100 billion for the first time in 2025, growing 7% to \$107 billion. The report projects investment will increase 9% to \$116 billion in 2026, 4% to \$120 billion in 2027, and 15% to \$138 billion in 2028. "The semiconductor industry is entering a pivotal era of transformation, driven by unprecedented demand for Alenabled technologies and a renewed focus on regional self-sufficiency," said Ajit Manocha, President and CEO of SEMI. "Strategic global investments and collaboration are driving robust, advanced supply chains and faster deployment of next-generation semiconductor manufacturing

technologies. The global expansion of 300mm fabs will enable progress in data centers, edge devices, and the digital economy."

#### **Segment Growth**

The Logic & Micro segment is projected to lead equipment expansion with \$175 billion in total investments from 2026 to 2028. Foundries are expected to be the primary drivers of this growth, fueled by sub-2nm capacity buildouts. Key enablers include advanced technologies such as gate-all-around (GAA) architecture and backside power delivery, which are essential to enhancing chip performance and power efficiency for increasingly demanding

Al workloads. More advanced 1.4nm process technology is expected to enter volume production by 2028-2029. Additionally, Al performance improvements are anticipated to drive massive growth in edge-devices including automotive electronics, IoT applications, and robotics. Beyond advanced processes, demand across all nodes and various electronics devices is expected to surge significantly, fueling mature process equipment investment.

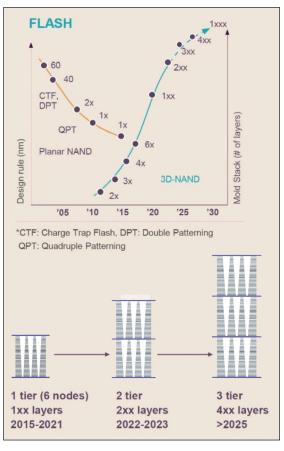

The Memory segment is projected to rank second with \$136 billion in spending over the three-year period, marking the beginning of a new growth cycle for the segment. DRAM-related equipment investment is expected to exceed \$79 billion from 2026 to 2028, with 3D NAND investment reaching \$56 billion over the same period. Al training and inference have driven comprehensive demand increases across various types of memory.

Al training requires greater data transmission bandwidth and extremely low latency, significantly boosting high bandwidth memory (HBM) demand. Moreover, model inference generates higher quality and more diverse Al digital content, creating substantial demand for end storage capacity and driving 3D NAND Flash requirements. This robust demand has sustained elevated levels of supply

chain investment in memory over the medium to long term, helping to mitigate potential downturns from traditional memory cycle fluctuations. Analog-related segments' anticipated investment is projected to exceed \$41 billion over the next three years.

Including Compound semiconductors, the power-related segment is expected to invest \$27 billion from 2026 to 2028.

#### Regional Growth

China is expected to continue to lead in 300mm equipment spending with \$94 billion in projected investments from 2026 to 2028, sustained by national self-sufficiency policies.

Korea is projected to rank second in global 300mm equipment spending over the three-year period with \$86 billion invested, supporting industries worldwide in generative AI demand. Taiwan is expected to invest \$75 billion in 300mm equipment over the three years, ranking third. Investment will concentrate primarily on 2nm and sub-2nm capacity to maintain dominance in advanced foundry capacity and technology leadership.

The report projects Americas to invest \$60 billion from 2026 to 2028, rising to fourth position. U.S. suppliers are expanding advanced process capacity to meet surging Al application demands while catalyzing domestic industrial and investment upgrades to maintain global technology development leadership.

Japan, Europe & Middle East, and Southeast Asia are projected to invest \$32 billion, \$14 billion, and \$12 billion, respectively, over the three-year period. Policy incentives aimed at alleviating critical semiconductor supply concerns are expected to increase equipment investment by more than 60% in these regions by 2028 compared to 2024.

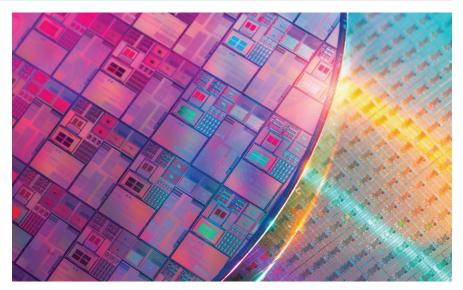

# Global silicon wafer shipments to rebound 5.4%

Global shipments of silicon wafers are projected to increase 5.4% in 2025 to 12,824 million square inches (MSI)

followed by steady growth through 2028 when the market is expected to reach a new industry record of 15,485 MSI, SEMI reported today in its annual silicon shipment forecast.

In 2025, the increase in silicon wafer shipments has been supported by strong Al-related growth, including advanced epitaxial wafers for leading edge logic devices and polished wafers for high bandwidth memory (HBM). Wafer shipments for non-Al applications, however, are just beginning to demonstrate a gradual recovery from the recent downcycle. The steady growth is expected to continue through 2028, driven by Al's expanding compute footprint in data centers and at the edge.

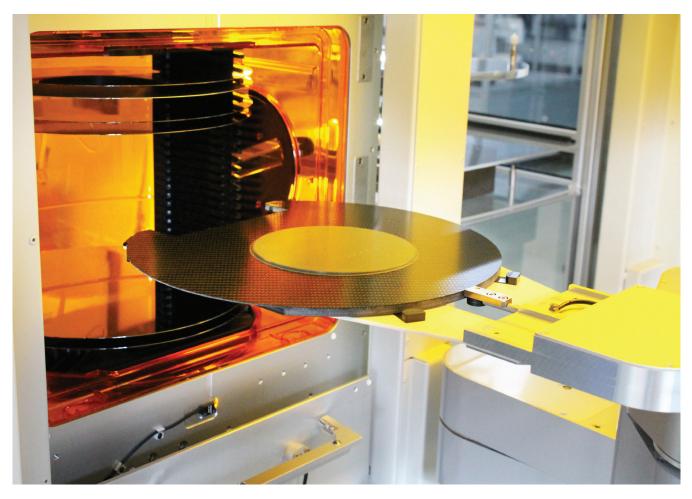

Silicon wafers are the fundamental building material for the majority of semiconductors, which are vital components of all electronic devices. The highly engineered thin disks, produced in diameters of up to 300 mm, serve as the substrate material on which most semiconductor devices, or chips, are fabricated.

All data cited include polished silicon wafers and epitaxial silicon wafers shipped by wafer manufacturers to end users. The data does not include non-polished or reclaimed wafers.

# SEMI updates International Board of Directors

SEMI has announced updates to the SEMI International Board of Directors. Tetsuro (Terry) Higashi, Chairman of the Board of Directors for Rapidus, has been elected and began his three-year term on the SEMI International Board.

The following six board members have been reelected and were announced during the SEMI annual membership meeting on October 8, 2025, at SEMICON West:

- Tim Archer, President and CEO, Lam Research

- Doris Hsu, Chairperson and CEO, GlobalWafers

- Toshiki Kawai, Representative Director, President and CEO, Tokyo Electron

- Jon Kemp, President, Electronics and Industrial, DuPont

- O Yong Han (YH) Lee, Chairman, Wonik

- Sue Lin, Vice Chairman, Hermes Epitek

The 18 voting directors and 10 emeritus directors on the SEMI International Board represent companies from across the global microelectronics supply chain, positioning SEMI to best support innovation in all areas of the industry. SEMI directors are elected by the general membership as voting members of the Board and can serve a

China is expected to continue to lead in 300mm equipment spending with \$94 billion in projected investments from 2026 to 2028, sustained by national self-sufficiency policies

total of five, three-year terms.

# NNME debuts ChipPath

To help meet the growing demand for skilled workers in the U.S. semiconductor and microelectronics industry, the National Network for Microelectronics Education (NNME), operated by the SEMI Foundation, has launched ChipPath, a first-of-its-kind, Alenabled career platform that connects individuals directly to real opportunities across the industry.

With over 90,000 live job postings and counting, ChipPath is already one of the most comprehensive semiconductor workforce tools in the country. Unlike traditional job boards, ChipPath autonomously scrapes and aggregates open positions from the websites of SEMI member companies, capturing tens of thousands of roles across the full microelectronics supply chain, from design and manufacturing to automation, facilities, and materials.

"ChipPath is more than a job board, it's a bridge to opportunity," said Shari

Liss, Vice President of Workforce Development and Initiatives at SEMI. "It's a movement to make the semiconductor workforce accessible to all Americans. This platform opens doors for students, veterans, career changers, and seasoned engineers, helping to see themselves in this industry and take real, actionable steps toward building their future in it."

# Building the Bridge Between Talent and Opportunity

The semiconductor industry is expanding at record speed, yet many potential job seekers don't know how to start an industry career. ChipPath bridges that gap by helping users explore, prepare, and connect through an integrated set of tools designed specifically for semiconductor careers.

The platform includes four powerful components:

Smart Resume Builder: Creates professional, industry-aligned resumes in minutes using Al-driven prompts that highlight relevant skills, certifications, and experience. Career Mapping &

**Exploration:** Helps users discover the breadth of opportunities in semiconductors and visualize clear pathways to advancement.

- Training & Development

Resources: Connects learners to certificate programs, apprenticeships, and degree pathways offered by NNME partners across the country.

- Live Job Openings

Nationwide: Features over 90,000

active roles scraped directly

from SEMI member company

websites, providing a real-time view

of the industry's hiring landscape.

"For too long, semiconductor careers have been somewhat invisible, seemed out of reach or hard to navigate," said Michelle Williams, Executive Director of the SEMI Foundation. "ChipPath changes that. It illuminates opportunities, empowers people to see where they fit, and gives them the tools to get there. No gatekeeping, no quesswork."

### Next Up: Employer Dashboard Launching in 2026

The NNME and SEMI Foundation are already developing the next phase of ChipPath: a robust Employer Dashboard set to debut in early 2026. This feature will enable companies to curate and prioritize the skills and qualifications most important to their workforce needs, search and connect directly with job seekers, and gain data-driven insights into national workforce trends. The platform already operates autonomously, capturing tens of thousands of opportunities in real time.

- Based around a hot topic for your company, this 60-minute recorded, moderated zoom roundtable would be a platform for debate and discussion

- Moderated by Editor, Phil Alsop, this can include 3 speakers

- Questions prepared and shared in advance

Cost: £5995

**Contact:** Jackie Cannon jackie.cannon@angelbc.com

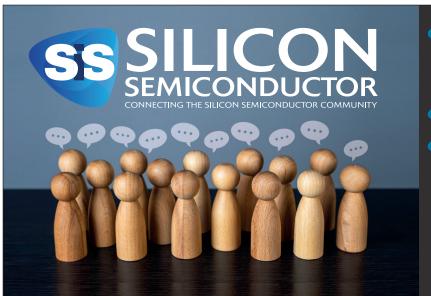

# motomation

Providing innovative and competitive solutions worldwide. From individual modules to entire platforms, for semiconductor and flat panel display industry as well as laboratory automation.

Visit us at Semicon Europa and Semicon West or www.motomation.com

With our partners at:

# Trends and drivers for next-generation process vacuum

Edwards Vacuum examines several emerging production processes with an eye towards identifying trends that will drive the development of nextgeneration vacuum systems.

MOST semiconductor manufacturing processes require a vacuum in the process chamber to provide the pristine environment needed to ensure fault-free production and to remove excess process gases and reaction by-products. A modern fab with 60,000 wafer starts per month may contain 1000 or more vacuum process tools.

To support them the fab may need as many as 3500 dry vacuum pumps, most located below the fab in the sub-fab, and perhaps another 1200 turbomolecular pumps, located either in the sub-fab or attached directly to the process chamber/airlock to provide rapid wafer exchange and chamber pump-down. As process complexity continues to increase, the impact of vacuum system performance on process performance and productivity is also growing. Without vacuum the process stops, making overall reliability, especially the avoidance

of unplanned downtime, the first priority. Minimizing total cost of ownership by extending the mean-time-between-service (when a pump is normally replaced from spare inventory and sent off-site for refurbishing) is a close second. As new processes and new materials are brought into high volume production, other details of vacuum system design and operation become more complex and more important. Here we will look at several emerging production processes with an eye towards identifying trends that will drive the development of next-generation vacuum systems.

#### A look back

Although the integrated circuit (IC) was invented in 1958, it was 1971 before the first processors based on now-familiar CMOS technologies were mass-produced (Intel's 4004). The manufacturing process, involving the sequential deposition and

patterning of multiple layers, was fundamentally the same then as it is now; though minimum feature sizes then measured in the tens or hundreds of micrometers, many thousands of times larger than today's nanometer-scale features. Then, as now, most process steps required vacuum conditions in the process chamber to control the chemical composition of the process environment. Most vacuum pumps in use in the first generations of integrated circuits (IC) were oil-sealed rotary vane pumps.

By the 1980s, IC production was expanding rapidly. New processes and increasing gas flows led to problems caused by aggressive chemicals and solids collecting in the pump oil. Frequent maintenance procedures to change very expensive specialty pump oils interrupted production, reduced productivity, and increased cost-of-ownership. In addition, new processes with more stringent requirements for contamination and cleanliness were intolerant of oil back-streaming from the vacuum system.

In 1980 Edwards introduced the first viable "dry" (oil-free) pump. The key innovation was a unique arrangement of roots and claw mechanisms in a multi-stage configuration that delivered clean vacuum with no need for oil to seal and lubricate the pump. Dry pumps were quickly adopted by semiconductor manufacturers and were arguably a critical enabler for the continuing development of increasingly complex semiconductor processes. Continuous innovation ever since has resulted today in a range of dry pumps, each tailored to address the specific challenges of new processes and process chemistries. In many cases, processes that are now commonplace would not have been possible without major innovations in vacuum systems.

# Significant innovations since the dry pump include:

- New designs that prevent the accumulation of powders or the deposition of condensable by-products inside the pump

- Sophisticated data collection and analysis systems that optimize performance, coordinate maintenance schedules, monitor system health and predict maintenance requirements.

- Special coatings for pump components that resist attack by harsh process chemicals

- Green mode operation that reduces energy consumption by putting the pump in a low power mode when the process tool is idle

New developments in vacuum technologies have also significantly impacted the environmental profile of semiconductor manufacturing. Improving energy efficiency has been a persistent focus. Process-vacuum pumps can represent 12% or more of the total energy consumed by a semiconductor manufacturing facility. Current generation semiconductor dry pumps use less than half the

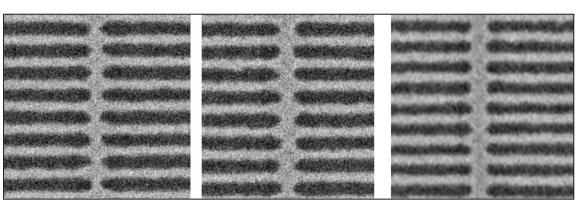

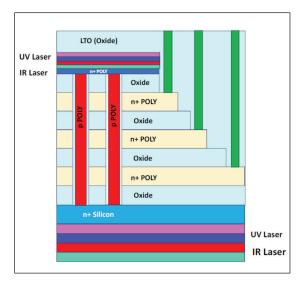

> Figure 1. 3D NAND flash memory uses very high aspect-ratio holes to create memory lines. The channels, and other HAR features must be lined with multiple thin conformal layers of various materials.

energy consumed by their predecessors, while providing higher levels of performance, extended service intervals, and smaller footprints that improve sub-fab space utilization. In addition to reducing operating costs, the improved energy efficiency also reduces greenhouse gas emissions that result from energy production.

#### Looking ahead

As manufacturers develop new processes and introduce new materials, vacuum technologies must continue to evolve. The overall pressure in the process chamber as well as the partial pressure for each reacting gas will remain primary considerations. Pumping speed determines how fast the chamber can be brought to the required vacuum level and thus impacts process throughput and productivity. This effect is multiplied by processes such as atomic layer etch and deposition, which require frequent exchanges of gases in the chamber. Stability of the vacuum environment is also critical as it affects process variation, defect creation, and consequently process yield.

A brief survey of expected developments in several mainstream device technologies illustrates the challenges next-generation vacuum systems will need to address. For decades device manufacturers focused their efforts to pack more capability into less space on increasing aerial density, i.e., shrinking the size of individual components in an essentially two-dimensional layout. Those efforts resulted in the remarkable progress first observed by Intel's Gordon Moore: that the number of transistors in an

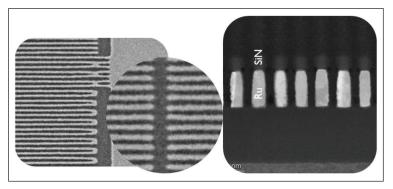

> Figure 2. **Current DRAM** designs use verticallyoriented capacitors to store information. Manufacturers must reduce the diameter and pitch of the capacitors to increase memory density. Future designs will adopt a 3D architecture that arranges horizontally oriented capacitors in many layers.

integrated circuit doubles about every two years. In recent generations, as transistors have become much smaller, further shrinking has become more difficult and more costly, resulting in a general slowing of the doubling rate. The last decade has seen the emphasis in many applications shift from two-dimensional layouts to more complex three-dimensional architectures that exploit the vertical dimension to pack more computing power into less space. The examples below illustrate this transition in 3D-NAND memory, DRAM, and logic.

## **New Architectures**

3D NAND memory – 3D-NAND flash memory provides non-volatile data storage. It is used extensively in applications like solid state storage, where it replaces magnetic storage on disk drives. The defining characteristic of 3D-NAND is its storage of data in vertical strings of memory cells, thus multiplying, relative to conventional planar designs, the amount of data that can be stored in a given area on the wafer. Current generation 3D-NAND uses stacks (tiers) of around 200 layer-pairs. Some devices stack multiple tiers to increase capacity. Manufacturers' roadmaps predict significant increases in the number of layers per tier and the number of tiers per module over the next decade.

**DRAM** – DRAM (dynamic random-access memory) is faster than 3D-NAND, but also more expensive. And it is volatile – it loses the stored information when power is turned off. Its speed suits it well for operational applications, but its higher cost and volatility make it unsuitable for long-term storage of large amounts of data. Each memory cell may comprise only a single transistor and a single capacitor, with the absence or presence of charge on the capacitor determining the logical state of the cell. Current DRAM designs are essentially planar with a tubular capacitor oriented vertically above each transistor. Beginning as vertical holes, the

capacitors are fabricated by depositing concentric layers of conductive and dielectric materials. To increase memory density, manufacturers must make the capacitors taller and thinner. The diameter and pitch of the capacitors are expected to shrink substantially over the next ten years, and heights to increase. The most significant change in DRAM will be a predicted transition to 3D architectures, in which multiple transistors and horizontally oriented capacitors are stacked vertically.

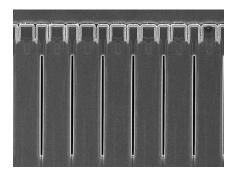

**Logic** – Logic, the network of variously interconnected, on-or-off transistors that actually performs computations is also becoming more complex as it transitions to three-dimensional architectures. The transistors are generally field effect transistors (FET). In a conventional planar FET, a gate is positioned above a semiconducting channel that connects a source and a drain. A voltage applied to the gate generates an electric field in the channel. The presence or absence of the field controls the flow of current through the channel, turning the transistor off or on. To improve performance of the transistor while reducing its size, designers have sought to provide better gate control over the channel. FinFETs, now widely produced with high-volume processes, feature a vertical fin structure surrounded on three sides by the gate. Gate-all-around (GAA) transistors take this further by wrapping the gate entirely around the channel, improving electrostatic control. The next innovation, complementary FET (CFET) stacks n-type and p-type transistors one atop the other. In most GAA transistors the channels are formed from very thin "nanosheets" of semiconducting material. New channel materials, such as transition metal dichalcogenides (TMD), could enable transistor gates as thin as a single molecular monolayer.

#### **New Processes**

HAR etch – More complex architectures incorporate novel features such as tall, narrow (high-aspectratio) holes and trenches. HAR features, such as the holes for memory strings and trenches in 3D-NAND and capacitors in DRAM begin with a specialized etch process. These highly directional (anisotropic) processes use complex chemical and physical interactions among the etched material, etching gases, and energetic ions/radicals to create features with tightly controlled sizes and profiles. The great depths and small etch fronts at the bottoms of HAR features extend etching times and reduce throughput. Longer etch steps require innovative mask materials that can resist the etching action to preserve the desired layer pattern. Highly reactive gases and process by-products are removed from the chamber by the vacuum system.

Chemical Vapor Deposition (CVD) – CVD uses chemical reactions to create thin films of solid materials on a heated surface. There are many variants, including atmospheric pressure CVD, but most processes used in semiconductor

manufacturing (PECVD, LPCVD, SACVD) proceed under vacuum conditions. In a CVD process the heated substrate is exposed to process gases containing precursors of the desired material, which react in the gas phase and accumulate on the wafer surface to form the deposited layer. The processes are relatively fast, and the deposition continues as long as the surface is exposed to the process. The thickness of the film is a complex function of flow rate, partial pressure, temperature, plasma settings (frequency, power, etc.), and process time.

To increase productivity, manufacturers are demanding higher flow rates and increased utilization (the ratio of production to capacity). At the same time, they are introducing new chemistries and materials that may have unexpected impacts on process equipment. Excess process gases and by-products can be toxic, corrosive, or explosive, raising significant safety concerns. Process windows are narrowing for film properties and uniformity. Thermal budgets must be carefully managed to avoid damage to the device being fabricated.

Advanced device architectures pose specific challenges. In particular, CVD processes are not good at maintaining uniformly thick films in the presence of significant topography, especially the extreme topography of HAR features, where the deposition process has restricted access to the internal vertical walls and deeply recessed bottoms of the features.

Atomic Layer Deposition (ALD) - ALD may be considered a variant of CVD. It offers an elegant solution for depositing highly conformal, precisely controlled thin films on complex, deeply recessed surfaces. The deposits accumulate one atomic layer at a time as the surface is exposed to a repeating cycle of precursor and reactant gases. In the first phase, the precursor reacts with specific sites on the surface. The reaction is self-limiting – once all sites have been occupied by a precursor molecule, the reaction stops. Next, the precursor gas is removed from the chamber, and a reactant gas is introduced. The reactant interacts with the previously deposited precursor, again in a self-limited way, to complete the deposition and recreate the original surface chemistry. The newly deposited monolayer is ready for another ALD cycle. Because both reactions

are self-limiting, film thickness is a function of the number of cycles, not exposure time. This gives process engineers the luxury of allowing each cycle of the process to continue as long as needed to be sure all surfaces are completely and uniformly covered. The biggest drawback of ALD is its slow speed. It is best suited to the deposition of very thin films that require fewer deposition cycles.

#### **New Materials**

The development and integration of new materials have played an essential role in semiconductor innovation throughout its history. Through 1990, most fabrication schemes used process chemicals containing no more than a dozen elements: H, B, N, O, F, Al, Si, P, Cl, Ar, As, and Sb. The nineties saw the incorporation of 5 more: Ti, Cu, Br, Ta, and W.

The aughts added a whopping 43 elements: He, C, Ca, V, Cr, Fe, Co, Ni, Zn, Ge, Sr, Y, Zr, Nb, Mo, Ru, Rh, Pd, Ag, In, Ba, La, Hf, Re, Os, Ir, Pt, Au, Pb, Bi, Ce, Pr, Nd, Pm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, and Lu. And since 2010, 8 more: Mg, Mn, Ga, S, Se, Te, I, Xe. Fully 68 of the first 83 elements have now found their way into the production process. Most of these materials pass through the vacuum system, and each requires careful consideration to ensure safe, efficient handling.

# New Vacuum Requirements

What effects do evolving device architectures and fabrication processes have on the vacuum systems tasked with removing excess process gases and byproducts from process chambers?

To increase productivity, manufacturers are demanding higher flow rates and increased utilization (the ratio of production to capacity). At the same time, they are introducing new chemistries and materials that may have unexpected impacts on process equipment. Excess process gases and by-products can be toxic, corrosive, or explosive, raising significant safety concerns

Figure 3. Logic transistors began the transition from planar to 3D more than a decade ago. FinFETS are in their 5th generation. Advanced devices are now adopting gate-allaround designs that stack multiple gates. Complementary **CFET will** position stacks of n-type and p-type GAA transistors one over the other.

**Footprint** – Process tools are trending toward larger platforms with more chambers, fitting more production capacity into less fab space. This increase in the density of chambers in the fab and demands commensurate footprint reductions in the sub fab, where supporting pumps and abatement systems must fit within the shadow of the process tool above.

**Speed** – New process technologies need higher flow rates, lower pressures, and faster pump-down times, all of which increase demand for higher speed and capacity from pumps and abatement systems. This is especially true for processes such as ALD, which require frequent exchanges of all gas in the process chamber.

Efficiency – Energy efficiency is one of the rare instances when the economic and environmental priorities of semiconductor manufacturers align. Vacuum systems account for as much as 25% of the energy consumed by a modern fab. Improving efficiency reduces both operating costs in the fab and any greenhouse gas emissions associated with power production.

Adaptation to new processes and materials – If the vacuum fails, the process stops. Avoiding unplanned downtime and maximizing process equipment availability require careful attention to the impacts of new materials and processes on supporting vacuum systems. Etch gases are highly corrosive. Some process gases and by-products can condense and solidify, blocking vacuum lines and seizing pumps – these deposits can be managed by controlling temperature along the lines and through the pump. Some gases generate powders that must be moved through the system and properly disposed of. Still others may be flammable, explosive, pyrophoric, or toxic, constituting health and safety hazards.

Collaboration and customization - The semiconductor industry has seen a fundamental change over the last decade as the era of lockstep two-dimensional shrinks has given way to innovative approaches that continue to pack more power into less space. The shared industry roadmap that efficiently guided manufacturers for decades has become less clear, and manufacturers are less open about their internal roadmaps. In diversification lies great opportunity. Innovation new architectures, new processes, new materials - continues to emerge. Everyone wants innovation, but no one really wants to be first. The onus has shifted to individual manufacturers and suppliers to collaborate in developing customized solutions. Close relationships that encourage information exchange and early involvement in applicationspecific vacuum system design will be essential, and supplier knowledge and expertise based on broad engagement across the industry will acquire new

#### Stay tuned

value.

We have looked here at the growing complexity of semiconductor device manufacturing as the industry transitions from simple two-dimensional shrinks to complex three-dimensional architectures, including examples from logic, 3D NAND and DRAM. New architectures have generated the need for new processes and materials, e.g. ALD and HAR etch, which in turn have placed new demands on process tools and the vacuum systems most of those tools depend on. We have reviewed the requirements for vacuum systems, both fundamental: reliability and MTBS; and emerging: footprint, speed, efficiency, adaptation, customization, and collaboration. These and more are driving our efforts to develop the next generation vacuum platform. Stay tuned, there is much more to come.

SCREEN

# **Wafer Cleaning System**

Wet Station | Spin Scrubber | Single Wafer Cleaner

15,000+ units shipped

**SCREEN** Semiconductor Solutions Co., Ltd.

SEMICON° EUROPA Nov 18–21, 2025, SCREEN Booth #B1700

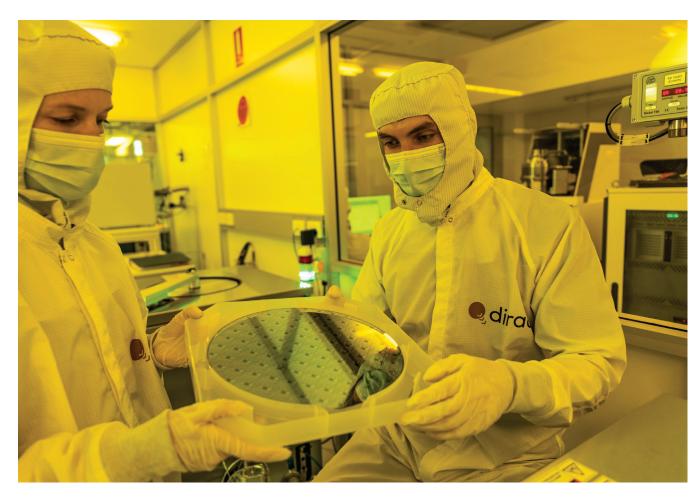

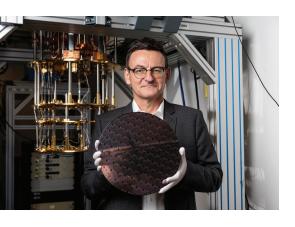

# Imec technology lights the path to utility scale for Diraq's quantum chips

Silicon qubits made using advanced industrial manufacturing methods have met key performance criteria, paving the way to mass production of functional quantum computers.

IMEC and Diraq, a pioneer of siliconbased quantum computing, have demonstrated that industrially made silicon quantum dot qubits consistently show error rates that surpass the values needed for quantum error correction.

The results, reported in Nature, show that Diraq's qubits can be manufactured reliably with the tools of the silicon microchip trade, confirming the potential of imec's industrial manufacturing techniques for developing large-scale silicon-based quantum computers.

Leveraging nearly a decade of careful optimization and engineering of spin-qubit fabrication at imec, Diraqdesigned devices were shown to consistently achieve over 99% fidelity in operations involving two quantum bits (or 'qubits'). This feat, made possible by imec's advanced spin qubit technology platform, is a crucial step in Diraq's roadmap toward utility scale — the point at which a quantum computer's value exceeds its cost.

Diraq's CEO and Founder, Andrew Dzurak, said, "Achieving utility scale in quantum computing hinges on finding a commercially viable way of producing high-fidelity qubits at scale. Diraq's collaboration with imec makes it clear that silicon-based quantum computers can be built by leveraging the mature semiconductor industry, which opens a cost-effective pathway to chips containing millions of qubits while still maximizing fidelity."

## Technical summary

The fidelity of a quantum operation quantifies how close the actual operation is to its ideal version and is a key metric for enabling large-scale quantum computers. Ideally, fidelities must (far) exceed 99% across all operations. Only then are errors rare

# RESEARCH NEWS | QUANTUM CHIPS

enough for quantum error correction methods to work successfully. In this work, fidelities were reproducibly measured for a set of silicon quantum dot spin qubit operations across multiple devices state preparation and measurement of the qubits (SPAM), and one- and two-qubit gate operations performed on the qubits to control their state and entangle them — the elementary operations required for a utility-scale quantum computer.

Fidelities above 99.9% were achieved for SPAM operations, and fidelities systematically exceeding 99% were shown for one- and two-qubit gate operations, making quantum error correction of industrially fabricated quantum dot qubit devices now a realistic prospect.

Typically, quantum devices fabricated in academic clean rooms are selected for measurement on the basis of their quality, a process that produces 'hero' devices, obscuring the reproducibility of the results. In the Nature publication,

Diraq measured devices that were selected at random, obtaining reproducible data on sets of two-qubit devices, each consisting of a double quantum-dot structure. The devices were fabricated using imec's 300mm spin qubit platform for silicon quantum-dot structures, which is optimized for low electrical noise and high uniformity.

In order to also suppress the magnetic noise from residual nuclear spins in the substrate, the quantum-dot structures were fabricated on an isotopically enriched 28Si layer.

Kristiaan De Greve, fellow and program director for quantum computing at imec: "For the first time, silicon MOS based quantum-dot spin-qubit devices realized with industrial manufacturing techniques perform as well as academic hero devices. This shows that imec's 300mm process flow for MOS based quantum-dot structures enables a lownoise qubit environment, resulting in high fidelity values for a set of critical qubit operations. The methods used

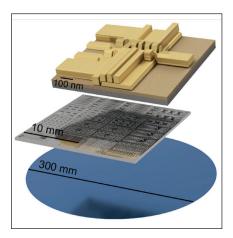

> Figure 1. Schematic of a Diraq two-qubit device on a 300mm wafer, showing the full wafer, single die and single device level (Dumoulin Stuyck et al, Nature – 2025).

and insights gained from it also show us that there is further room for fidelity improvement, as higher fidelities can be achieved through even further isotopic enrichment of the silicon-channel layer with 28Si."

# Checking the quality of materials just got easier with a new Al tool

Acting as a "virtual spectrometer," SpectroGen generates spectroscopic data in any modality, such as X-ray or infrared, to quickly assess a material's quality.

## BY JENNIFER CHU, MIT NEWS

MANUFACTURING better batteries, faster electronics, and more effective pharmaceuticals depends on the discovery of new materials and the verification of their quality. Artificial intelligence is helping with the former, with tools that comb through catalogs of materials to quickly tag promising candidates.

But once a material is made, verifying its quality still involves scanning it with specialized instruments to validate its performance — an expensive and timeconsuming step that can hold up the development and distribution of new technologies.

Now, a new Al tool developed by MIT engineers could help clear the quality-control bottleneck, offering a faster and cheaper option for certain materials-driven industries. In a study appearing today in the journal Matter, the researchers present "SpectroGen," a generative AI tool that turbocharges scanning capabilities by serving as a virtual spectrometer. The tool takes in "spectra," or measurements of a material in one scanning modality, such as infrared, and generates what that material's spectra would look like if it were scanned in an entirely different modality, such as X-ray. The Al-generated spectral results match, with 99 percent accuracy, the results obtained from physically scanning the material with the new instrument.

Certain spectroscopic modalities reveal specific properties in a material: Infrared reveals a material's molecular groups, while X-ray diffraction visualizes the

➤ The circle with the chip symbolizes SpectroGen, with the connecting threads depicting the process of generating a material's spectrum.

Credit: Courtesy of the researchers.

material's crystal structures, and Raman scattering illuminates a material's molecular vibrations. Each of these properties is essential in gauging a material's quality and typically requires tedious workflows on multiple expensive and distinct instruments to measure.

With SpectroGen, the researchers envision that a diversity of measurements can be made using a single and cheaper physical scope. For instance, a manufacturing line could carry out quality control of materials by scanning them with a single infrared camera. Those infrared spectra could then be fed into SpectroGen to automatically generate the material's

X-ray spectra, without the factory having to house and operate a separate, often more expensive X-ray-scanning laboratory.

The new Al tool generates spectra in less than one minute, a thousand times faster compared to traditional approaches that can take several hours to days to measure and validate. "We think that you don't have to do the physical measurements in all the modalities you need, but perhaps just in a single, simple, and cheap modality," says study co-author Loza Tadesse, assistant professor of mechanical engineering at MIT. "Then you can use SpectroGen to generate the rest. And this could improve productivity,

efficiency, and quality of manufacturing." The study's lead author is former MIT postdoc Yanmin Zhu.

#### **Beyond bonds**

Tadesse's group at MIT develops Al-informed optical and spectroscopy systems that aim to advance disease diagnosis, therapy, and global health, in efficient, sustainable ways.

"Diagnosing diseases, and material analysis in general, usually involves scanning samples and collecting spectra in different modalities, with different instruments that are bulky and expensive and that you might not all find in one lab," Tadesse says. "So, we were brainstorming about how to miniaturize all this equipment and how to streamline the experimental pipeline."

Zhu noted the increasing use of generative AI tools for discovering new materials and drug candidates, and wondered whether AI could also be harnessed to generate spectral data. In other words, could AI act as a virtual spectrometer?

A spectroscope probes a material's properties by sending light of a certain wavelength into the material. That light causes molecular bonds in the material to vibrate in ways that scatter the light back out to the scope, where the light is recorded as a pattern of waves, or spectra, that can then be read as a signature of the material's structure. For AI to generate spectral data, the conventional approach would involve training an algorithm to recognize connections between physical atoms and features in a material, and the spectra they produce. Given the complexity of molecular structures within just one material, Tadesse says such an approach can quickly become intractable.

"Doing this even for just one material is impossible," she says. "So, we thought, is there another way to interpret spectra?"

The team found an answer with math. They realized that a spectral pattern, which is a sequence of waveforms, can be represented mathematically. For instance, a spectrum that contains a series of bell curves is known as a "Gaussian" distribution, which is associated with a certain mathematical expression,

With SpectroGen, the researchers envision that a diversity of measurements can be made using a single and cheaper physical scope. For instance, a manufacturing line could carry out quality control of materials by scanning them with a single infrared camera

compared to a series of narrower waves, known as a "Lorentzian" distribution, that is described by a separate, distinct algorithm. And as it turns out, for most materials infrared spectra characteristically contain more Lorentzian waveforms, while Raman spectra are more Gaussian, and X-ray spectra is a mix of the two.

Tadesse and Zhu worked this mathematical interpretation of spectral data into an algorithm that they then incorporated into a generative Al model.

"It's a physics-savvy generative AI that understands what spectra are," Tadesse says. "And the key novelty is, we interpreted spectra not as how it comes about from chemicals and bonds, but that it is actually math — curves and graphs, which an AI tool can understand and interpret."

### Data co-pilot

The team demonstrated their SpectroGen Al tool on a large, publicly available dataset of over 6,000 mineral samples. Each sample includes information on the mineral's properties, such as its elemental composition and crystal structure. Many samples in the dataset also include spectral data in different modalities, such as X-ray, Raman, and infrared. Of these samples, the team fed several hundred to SpectroGen, in a process that trained the Al tool, also known as a neural network, to learn correlations between a mineral's different spectral modalities. This training enabled SpectroGen to

take in spectra of a material in one modality, such as in infrared, and generate what a spectra in a totally different modality, such as X-ray, should look like.