Volume 20 Issue 1 2014

🔁 @compoundsemi

www.compoundsemiconductor.net

#### Going green with cubic GaN

#### Taking VCSELs into the blue

# Gan HEMTs for solid-state lighting

Nano-patterning enhances UV LEDs

IEDM considers flaws in GaN HEMTs

**COMPOUND** SEMICONDUCTOR Free Weekly E News round up , go to <u>www.compoundsemiconductor.net</u>

### 200mm GaN-on-Si Batch Reactor

# 5x200mm

### AIX G5+

#### AIX G5+ for GaN-on-Si

- Dedicated technology package

- Compatible with the AIX G5 HT platform

- Enables Si-style mass manufacturing

- Builds on planetary technology: Excellent and symmetric uniformities, controlled bow behavior, using standard Si substrates.

AIXTRON SE · info@aixtron.com · www.aixtron.com

# editorialview

by Dr Richard Stevenson, Editor

#### Finding favour with the foundries

IT'S COMMON KNOWLEDGE that silicon CMOS is struggling to keep pace with the rate of progress suggested by Moore's law. Maintaining efficiency gains that have traditionally come from geometrical scaling is getting tough, and it will require the introduction of higher mobility materials into the channel.

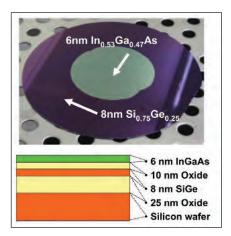

When this will happen is not set in stone – a best guess is the 7 nm node – and it is also unclear how silicon foundries will manufacture this new form of IC that will probably sport a pFET based on germanium and *n*-type cousin built from InGaAs.

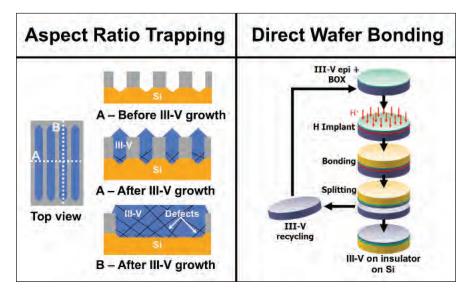

One way to make such a chip is to turn to a technology known as aspect ratio trapping: trenches are etched in the silicon wafer, before being filled with high-mobility material that forms the channel. This approach addresses the problem of defects formed by lattice matching – imperfections propagate in the direction of a crystal plane before terminating at a trench wall.

It will be interesting to see if foundries go down this trench-filling route by investing in new tools and introducing new deposition processes. After all, they may prefer an alternative way forward – pioneered by IBM – that would ultimately lay many of the new manufacturing challenges at the door of substrate makers. IBM's approach, described in detail in the feature "Turbocharging channel with compounds" (see p30), is to begin with an engineered wafer featuring two very thin high mobility layers: one is a III-V material and the other is an excellent hole

conductor, such as SiGe or germanium. A thin insulating layer separates these two.

Strengths of this technology include an insulator beneath the III-V that cuts leakage currents from source to drain. In addition, because the high mobility materials are present across the entire wafer, circuit designers have more freedom over the placement of their transistors.

So will this wafer-based method catch on? That's hard to say. But it's certainly an interesting option that I'll be keeping my eye on.

| Editor Dr Richard Stevenson                 | richardstevenson@angelbc.com<br>+44 (0)1291 629640 | Circulation & Subscriptions Assistant Annette Weatherilt                            | annette.weatherilt@angelbc.com<br>+44 (0)1923 690220 |  |

|---------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------|--|

| Contributing Editor Dr Rebecca Pool         | editorial@rebeccapool.com                          | Chief Operating Officer Stephen Whitehurst                                          | stephen.whitehurst@angelbc.com                       |  |

| News Editor Dr Su Westwater                 | suwestwater@angelbc.com                            |                                                                                     | +44 (0)2476 718970                                   |  |

| Director of SEMI Publishing Jackie Cannon   | jackie.cannon@angelbc.com                          | Directors Bill Dunlop Uprichard - CEO, Stephen Whitehurst - COO, Jan Smoothy - CFO, |                                                      |  |

|                                             | +44 (0)1923 690205                                 | Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal, Jason Holloway.            |                                                      |  |

| Senior Sales Executive Robin Halder         | robin.halder@angelbc.com                           |                                                                                     |                                                      |  |

|                                             | +44 (0)2476 718109                                 | Published by Angel Business Communications Ltd,                                     |                                                      |  |

| Sales Manager Shehzad Munshi                | shehzad.munshi@angelbc.com                         | Hannay House, 39 Clarendon Road, Watford, Herts WD17 1JA, UK.                       |                                                      |  |

|                                             | +44 (0)1923 690215                                 | T: +44 (0)1923 690200                                                               |                                                      |  |

| USA Rep: Brun Media: Tom Brun               | E: tbrun@brunmedia.com                             | F: +44 (0)1923 690201                                                               |                                                      |  |

|                                             | Tel: +001 724 539-2404                             | E: ask@angelbc.com                                                                  |                                                      |  |

| Janice Jenkins                              | E: jjenkins@brunmedia.com                          |                                                                                     |                                                      |  |

|                                             | Tel: +001 724-929-3550                             | Angel Business Communications Ltd                                                   |                                                      |  |

| Director of Logistics Sharon Cowley         | sharon.cowley@angelbc.com                          | Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK.           |                                                      |  |

|                                             | +44 (0)1923 690200                                 | T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com                   |                                                      |  |

| Design & Production Manager Mitchell Gaynor | mitch.gaynor@angelbc.com                           |                                                                                     |                                                      |  |

|                                             | +44 (0)1923 690214                                 |                                                                                     |                                                      |  |

| Circulation Director Jan Smoothy            | jan.smoothy@angelbc.com                            |                                                                                     | re finished with                                     |  |

|                                             | +44 (0)1923 690200                                 | BUSINESS COMMUNICATIONS this magazine                                               | please recycle it.                                   |  |

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd will be happy to part without the written consent of the publisher. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Cont, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP UK. The 2012 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: Pensord Press. ISN 1096-598X (Print) ISN 2042-7328 (Online) © Copyright 2014.

# Book your place at the **CS International Conference**

Tuesday 18th & Wednesday 19th March 2014

Save the Date

The compound semiconductor industry continues to evolve, developing and manufacturing new devices that will help to shape the world of tomorrow. This industry is currently debating answers to a handful of key questions: -

Will silicon CMOS overtake GaAs as the primary technology in the front-end handset market?

How long will it take for GaN and SiC make a substantial impact in the RF and power electronics arenas?

How quickly can LED chipmakers trim the cost-per-lumen and unlock a revolution in solid-state lighting?

Does the future for triple-junction solar cells lie in space or on the ground?

What devices can 'green' optical networks?

Are III-Vs the logical choice for next-generation microprocessors?

To know what the leading industry insiders are thinking about these important issues, make sure that you attend.

#### **Book your place NOW!**

Sheraton Frankfurt Airport Hotel, Germany Register: www.cs-international.net

Contact: Stephen Whitehurst T: +44 (0)24 7671 8970 E: stephen.whitehurst@angelbc.com

Connecting the leading compound semiconductor industry insiders

#### features

#### 30 Turbocharging channels with compounds To maintain the improvements in efficiency, foundries will have to replace silicon channels with those based on higher mobility

semiconductors. This could be implemented by turning to engineered wafers with separate layers for p-type and n-type transistors.

#### 36 Addressing weaknesses of GaN transistors

Researchers reveal how to slash dynamic resistance, minimise interface traps and identify the origin of current collapse.

#### 40 Bringing the inverter onto the chip

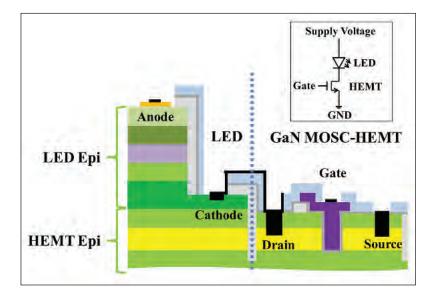

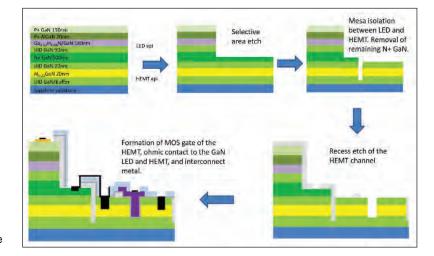

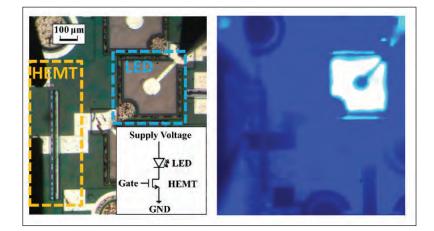

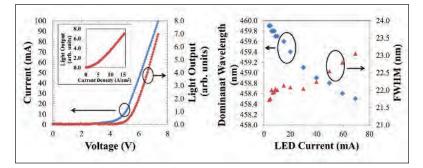

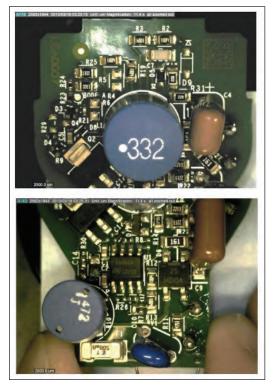

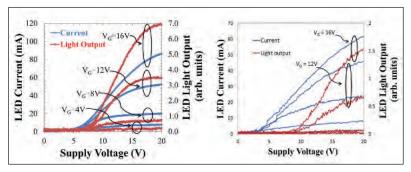

Monolithic integration of LEDs and transistors is helping to usher in a new era for solid-state luminaires, where the emitter and its control electronics are united on single chip.

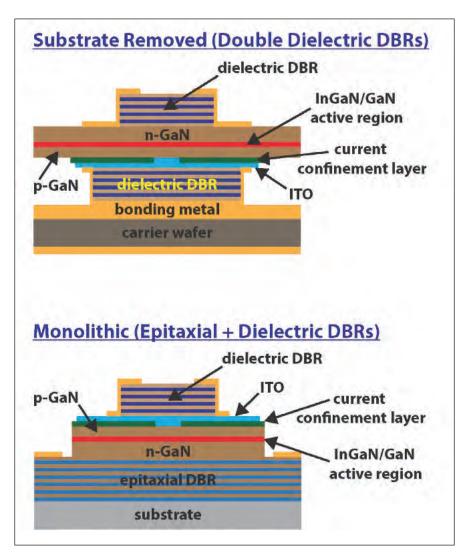

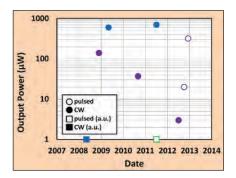

44 The evolving GaN VCSEL Building a GaN VCSEL is far harder than making one from GaAs, but progress is being made through different types of mirrors, alternative current injection schemes and new crystal orientations.

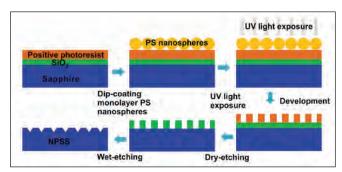

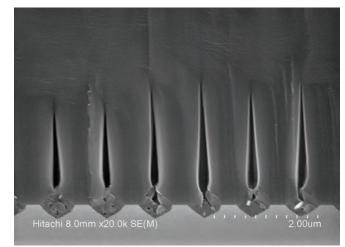

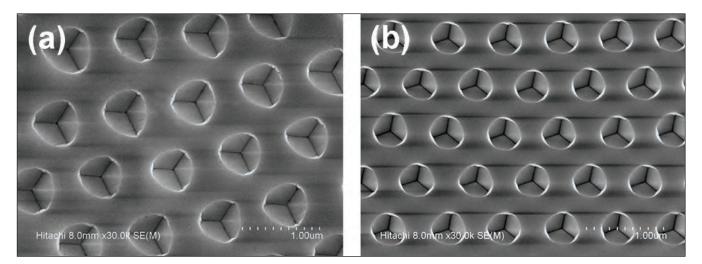

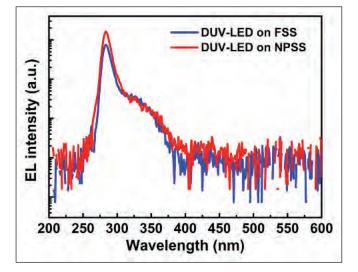

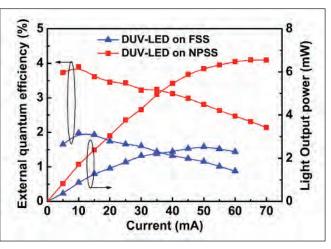

#### 50 Increasing ultraviolet efficiency with nano-patterned sapphire

Switching from conventional patterning of sapphire to a nano-scale variant trims epitaxial growth times and materials costs while boosting extraction efficiency.

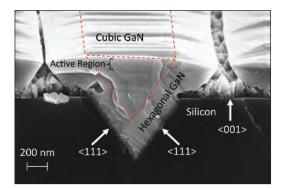

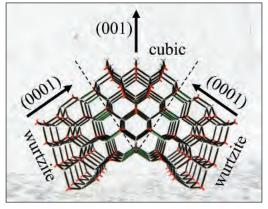

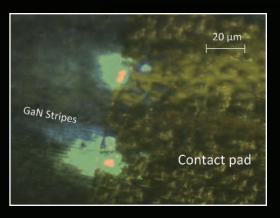

#### 54 Going green with cubic GaN

Conventional green LEDs are plagued by strong internal electric fields, which impair recombination and make it difficult to address droop. The solution: switch to growth on the cubic phase of GaN.

#### news analysis

- 16 Anvil to serve up cheap SiC switches

- 18 GaN growth: an extra inch

- 24 GaN-on-silicon LEDs slated for market growth

- 26 A rocky road to real power conversion

- 28 GaN advances into defence electronics

#### research review

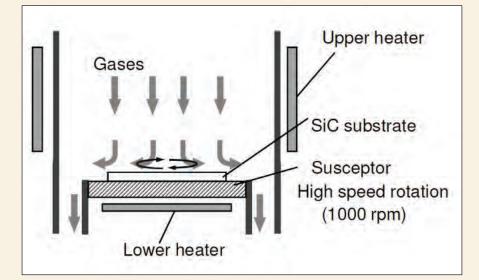

- 58 Accelerating SiC growth and throughput

- 60 Debut for double-quantum-well tunnel FET 61 Combatting droop in ultraviolet LEDs

Magazine and front cover

designed by

Mitch Gaynor

#### NEWS REVIEW

#### Infinera InP PICs to be used in several Telstra networks

INFINERA AND TELSTRA have announced the upgrade of multiple ultra-long haul submarine cable routes, optimising capacity and providing scalability and reliability on key routes of Telstra's network.

The Infinera Intelligent Transport Network will enable Telstra to quickly deploy 10G, 40G and 100G Ethernet and OTN services on: Telstra Endeavour - a 9,124 kilometre submarine cable connecting Sydney and Hawaii; Telstra's Designated Fibre Pair on the Asia America Gateway (AAG) submarine cable connecting Hawaii and California; Reach North Asia Loop (RNAL), which spans 9,000 kilometres to connect Hong Kong, Taiwan, Japan and South Korea Darrin Webb, Chief Operating Officer for Telstra Global, says, "As a trusted network supplier, our job is to ensure we are adapting and creating capacity where it is required. Demand for network services in the Asia Pacific region is growing exponentially and the addition of Infinera's DTN-X platform means we will be well placed to meet the speed and capacity needs of our customers."

"We are continually developing our network to meet customers' requirements and this is just one of the projects we are working on to ensure our network is always growing, improving and providing world class services," adds Webb. David Welch, Infinera CTO, Co-Founder and President, says, "As global businesses turn to cloud-based offerings, we're seeing increasing demand for reliable, global connectivity.

We are delighted to build on our existing relationship with Telstra Global to deploy an Intelligent Transport Network across these major submarine routes.

"With an Infinera Intelligent Network deployed across Endeavour, AAG and RNAL, Telstra can deploy highly reliable, differentiated services to their customers while reducing capital and operating costs through scale, multi-layer convergence and automation. Telstra Global's deployment is a great example of how long-haul super-channels with SD FEC are accelerating the pace of global communities."

The Infinera DTN-X is designed to scale without compromise to enable future upgrades to terabit super-channels and Terabit Ethernet.

The DTN-X converges five Terabits of non-blocking OTN switching into the same platform, resulting in more efficient network utilisation when compared to conventional WDM architectures.

Intelligent software combined with this converged platform automates manual operations to lower operational costs and enable faster service delivery.

Telstra Global provides innovative and flexible global communications services and solutions for organisations looking to maximise the benefits of globalisation, particularly across growth regions such as Asia, whilst driving sustainability and enhancing business agility.

Together with its offshore subsidiaries and international investments, Telstra Global serves companies spanning Asia Pacific, EMEA and the Americas. It operates award-winning networks which are amongst the largest and most diverse in Asia Pacific. It has licences in Asia, Europe and the US and facilitates access to over 1,900 PoPs in 230 countries and territories across the globe.

#### Anadigics' InGaP technology used in GALAXY Trend 3

ANADIGICS is shipping production volumes of its AWT5001 and AWT5008 ProVantage power amplifiers (PAs) to Samsung Electronics for the new GALAXY Trend 3.

The ProVantage solutions leverage Anadigics' InGaP-Plus technology to space-saving integration and lower overall system cost.

The GALAXY Trend 3, powered by ProVantage PAs, features a 4.3inch display, dual-core 1.2 GHz processor, and Android 4.2 Jelly Bean operating system.

"We are very pleased to be powering the new GALAXY Trend 3 by Samsung Electronics," says Jerry Miller, senior vice president of Cellular Products at Anadigics. "Our ProVantage solutions deliver outstanding value by providing a best-in-class combination of high power mode efficiency, linearity, and reduced system costs.

With a complete portfolio of industryleading solutions we continue to help Samsung bring to market a diverse set of mobile devices that target a wide range of segments."

Anadigics ProVantage power amplifiers help extend battery life by offering three selectable bias modes that optimize efficiency for low, medium and high output power levels, as well as a shutdown mode with low leakage current.

These power amplifiers are also designed for use with an external switch mode power supply (SMPS), in applications using average power tracking (APT), to further increase efficiency and reduce current consumption at low and medium operating powers.

#### Firecomms unveils green transmitter

FIRECOMMS has announced the availability of its 530 nm DC-1 Mb RedLink(R) transmitter for applications requiring extended link lengths over Plastic Optical Fibre (POF).

Operating in the green spectrum at 530nm, the new FT01MHNG transmitter exploits one of the lower attenuation windows of POF. At 0.1 dB/m, the attenuation of the FT01MHNG is considerably lower than that of traditional POF transmitters that operate in the red spectrum with an attenuation of approximately 0.2 dB/m.

These lower attenuation characteristics of the FT01MHNG transmitter make it possible to implement POF links up to 150 m or even 200 m where traditionally link lengths have been limited to 50 m.

Ideally suited for sensing, CANbus/ RS485/RS232 links, gaming, Smart Meter or other industrial command and control applications, the FT01MHNG transmitter opens up new possibilities for the equipment designer to replace more expensive silica-based solutions with POF, remove repeaters which are no longer needed, and implement new designs requiring galvanic or optical isolation where costs or distances have been previously prohibitive.

"Firecomms, a world leader in the research and development of light sources for POF, has pioneered the development of Resonant Cavity LEDs (RCLED) for the past decade," says John Lambkin, Firecomms CTO. "This announcement of a 530 nm based transmitter using extremely rugged InGaN semiconductors is another example of Firecomms' commitment to innovation and investment in our RedLink product line."

Firecomms has now completed a full qualification of these devices verifying

how the wavelength and output power remain remarkably stable over the entire industrial temperature range of -400 °C to +850 °C, and demonstrating their suitability for the most demanding of applications.

Link tests performed using this new transmitter with the Firecomms FR01MHIR receiver have shown transmission distances of up to 200 m depending on actual throughput.

#### Epistar unveils efficient infrared LED

#### LOTS OF FORWARD-LOOKING

technologies have been well developed and now applied to LED chip production. These include novel transparent conductive thin films, compound mirror structures, and new EPI structure designs for reducing the absorption of light. Recently, Epistar Lab claims to have made an amazing improvement on the infrared products and believes it has set new records in the LED industry.

According to latest data, the infrared product SFPN42 (chip size 1 x 1mm<sup>2</sup>) achieved wall plug efficiency of 75 percent with an operating current of 40mA and of greater than 70 percent at 350mA; the power even exceeds 1W and has reached 1027mW with the operating current of 1A. Such an impressed efficiency development has made LED chips more energy saving and eco friendly.

Now the infrared products are mostly adopted in the security monitor, smart touch panel and wireless communication systems. In the future, Epistar wants to use these products in other high potential markets to keep the competitive strength of its customers.

MEI enters Taiwanese market with advanced etch tool order MEI Wet Processing Systems and Services has received an order from a Taiwan based customer for its Advanced Etch Solution.

The tool is based on MEI's Revolution Wet Processing System, a semiautomated rotary wet processing system designed for batch wet processing (etch or solvent) for semiconductor and MEMS (micro-electromechanical systems) applications.

The Advanced Etch wet bench will be used for copper etch and titanium etch wet chemical processing of 200 mm compound semiconductor or MEMS wafers. "This is a prime example of the Advanced Etch applications market that MEI specialises in supporting," says Ed Jean, MEI's Sales Manager.

"Most wet process equipment suppliers tend to focus on either single wafer processing or generic equipment sales. There is a real need for semiconductor processing solutions that focus on challenging applications solutions, and MEI Wet Processing Systems and Services is meeting these specialised application needs, including proprietary Advanced Etch, Gold Etch, InGaP Etch and patented Metal Liftoff solutions." Founded in 1990 and based in Albany, Oregon, MEI Wet Processing Systems and Services LLC, is a wet processing equipment and service company serving the semiconductor, MEMS, solar, and high technology industries.

MEI's specialties include patented solutions for wet processing applications, automated and semi-automated wet process systems and services, linear and rotary wet benches for the semiconductor and material processing industries, automated chemical delivery systems and control automation software.

#### Soitec secures €21.3m funding for R&D

THE EUROPEAN COMMISSION has decided that the aid granted by France to the Soitec group to help it conduct the Guépard research and development project complies with the EU rules on state aid. This project is aimed at developing a new concentrated photovoltaic (CPV) technology. The aid addresses a genuine market failure without unduly distorting competition.

Commission Vice-President Joaquín Almunia, who is in charge of competition policy, says, "EU state aid rules encourage innovation and allow public aid to be targeted on projects that contribute to European growth and competitiveness. The Guépard project is a very good example of this: it will develop a high-efficiency photovoltaic cell that will not only contribute to making solar energy more attractive but also provide a credible technological alternative to the European photovoltaic sector, which has recently been destabilised."

# Reasons to sponsor CS International Conference 2015 Reach a global audience - a great platform for your company and products Increase your brand awareness - 8 months of marketing to the global industry Lead generation - pre, during and post conference Benefit from media exposure - HTML, social media, direct mail Form global partnerships - extensive networking opportunities Highly targeted marketing - reach over 80,000 compound semiconductor professionals

Reach new contacts - the only conference to cover the entire compound semiconductor industry

#### www.cs-international.net

Call now +44 (0)24 7671 8970 or email event@cs-international.net for sponsorship details

Connecting the leading compound semiconductor industry insiders

At the end of the Guépard project, Soitec will have produced a high-efficiency III-V multi-junction CPV cell.

CPV cells work by concentrating sunlight before transforming it into electrical energy. They are potentially much more efficient than today's silicon or thin film photovoltaic cells at converting solar energy. The Guépard project will be carried out in cooperation with an SME (InPact) and a research institution (CEA-LETI). The lead player, Soitec, will receive  $\in$ 21.3 million in state aid:  $\in$ 5.9 million in subsidies and  $\in$ 15.4 million in reimbursable advances.

The commission examined the compatibility of the aid in relation to its guidelines for state aid for research and development and innovation. After examining the file, the commission concluded that the Guépard project was affected by market failures. In particular, the partner research institution is expected to make the results of its research widely known through academic publications and training. The commission also recognised that investment in new solar technologies could be discouraged in the short and medium term, as the market has recently been destabilised by the dumping of Chinese solar panels. The commission considers that the aid is necessary and sufficient to allow Soitec to carry out the project.

In the absence of state aid, the company's R&D efforts would have been considerably reduced: it would for example have abandoned development of high-efficiency cells, considered to be an excessive risk. This would undoubtedly have affected the development of the CPV sector. Finally, the commission was convinced that the target market (ground-based solar power plants) offers good growth prospects, and that the risk of distorting competition could be removed. Soitec's future market share will be minimal compared to the current market share of leading companies in the sector.

The photovoltaic modules sector has a specific profile; since 2009 the average price of these modules has fallen by two thirds, while at the same time certain Asian companies have seen a sharp increase in their market share.

**Loomis Industries, Inc.** 1204 Church Street St. Helena, CA 94574

T. 707-963-4111 F. 707-963-3753 info@loomisinc.com www.loomisinc.com

#### THE LSD-155

Cutting Edge automated III-V Laser Diode and Wafer Processing

#### KEY ADVANTAGES:

- Increased Operator Productivity

- Integrated Scribe and Break Capabilities

- Bar Array Dicing (Grids of Laser Bars)

- Multiple Cleaving Options

- Multiple Wafer Holding Media Options

- High Resolution Optics

- Pattern Recognition with Micron Level Accuracy

- Cleaved Edge, Vision, When standard pattern alignment is not good enough.

#### EASE OF OPERATION:

- Easy to Navigate User Interface

- Password Protected Levels of Access

- Hands-Off Media Rotation

- Software/Recipe Controlled Process

Parameters, Pressures, and Speeds

#### LOOMIS LSD-155

Speed, product quality and yield speak for themselves. Contact Loomis Industries for information or a demonstration.

# GaN power defence project reaches conclusion

A GOVERNMENT and industry team led by engineers from the Air Force Research Laboratory's Materials and Manufacturing Directorate (AFRL/RX) have completed a GaN program.

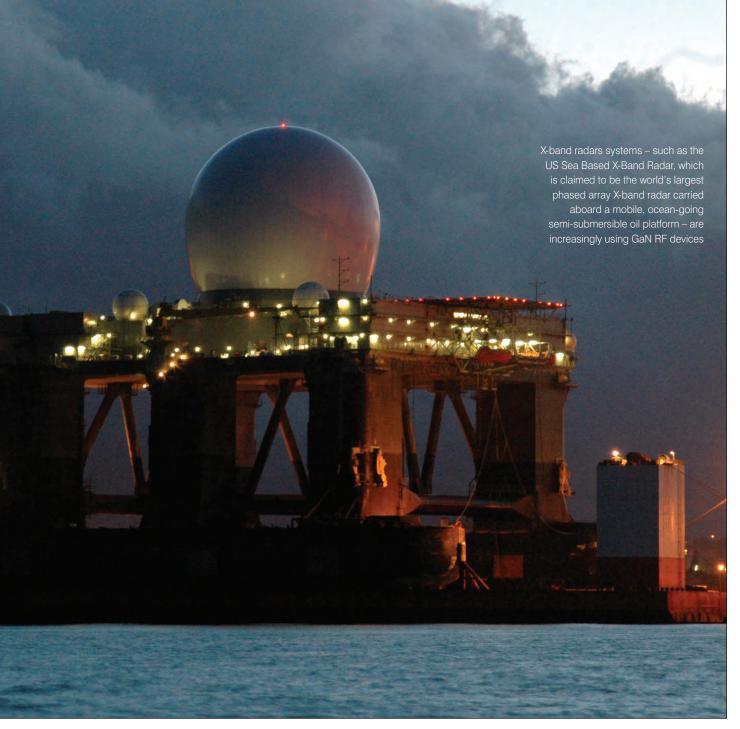

The project focused on assessing, improving, refining, and validating a domestic source of supply for X-Band GaN Monolithic Microwave Integrated Circuits (MMICs). Because GaN semiconductors enable devices and MMICs with improved power, efficiency and bandwidth, MMIC technology offers the highest level of integration and the smallest form factor and they have become the technology of choice for power amplifiers and radars.

MMIC technology typically provides better high-frequency performance by reducing parasitic circuit elements and provides enhanced reproducibility as a result of uniform processing and integration of all circuit elements. GaN products include power amplifiers and supporting MMIC solutions, such as low-noise amplifiers, driver amplifiers and limiters. GaN power amplifier technology significantly enhances the warfighters' capabilitie by increasing radar ranges, sensitivity, and search capabilities when compared to existing radar platforms based on other semiconductor technologies. Additional defence applications for GaN MMICs include communication systems, electronic warfare applications, imaging, and sensor systems.

The Manufacturing and Industrial Technologies Division (AFRL/RXM) Defence Production Act (DPA) Title III team is responsible for conducting this work. Title III is a Department of Defence (DoD)-wide initiative under the Deputy Assistant Secretary of Defence, Manufacturing and Industrial Base Policy (MIBP). The Air Force serves as the Executive Agent for the Title III Program within the Department of Defence and the Title III Program Office is located at Wright-Patterson AFB, Ohio, as a

component of AFRL/RXM.Jeffrey Smith, an engineer from RXM, serves as Air Force Executive Agent Program Manager. "The Title III Program is a governmentfunded venture that aides manufacturers who specialize in materials used for defence applications," Smith says. "Production capabilities that would otherwise be inadequate are transformed to support the material requirements of defence programs in a timely and affordable manner."

Smith notes Title III focuses on materials and components that could be used in a broad spectrum of defence systems. He says, "The direct and indirect benefits to defence programs resulting from Title III initiatives are substantial, and Title III projects create numerous economic and technological benefits for domestic industries and consumers."

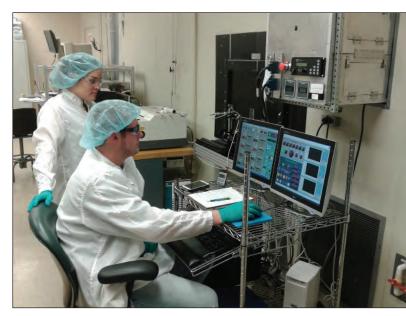

DPA Title III engineers worked with Raytheon to execute the program at its Compound Semiconductor Foundry, located within its Integrated Air Defence Centre in Andover, Mass. Raytheon, headquartered in Waltham, Mass., possesses a broad international and domestic customer base, including the U.S. Missile Defence Agency, the U.S. Armed Forces, and the Department of Homeland Security. In addition, its IADC facility is a Department of Defence Category 1A Trusted Foundry (the highest category awarded by the DoD), and is recognized for providing trusted, national security critical components. Their foundry employs 30 researchers and 100 device, circuit and module engineers in addition to numerous production staff operating a 23,000 square foot, Class-100 clean room facility.

This Title III project achieved the primary objective of improving and maturing the production of GaN MMICs by producing a manufacturing process capable of Low Rate Initial Production (LRIP).

"The project achieved a Manufacturing Readiness Level

of 8, meaning the fabrication processes are ready for LRIP for insertion into defence systems," Gene Himes, the AFRL/RXM program manager for the initiative says. "When comparing the final results to the baseline.

Manufacturing Readiness Assessment, Raytheon exceeded all threshold yield key performance parameters resulting in a three times improvement in product yield and a 76 percent cost reduction for its GaN MMICs."

In addition to yield improvements, the team logged more than one million hours of reliability testing over the course of the project. Comprehensive reliability testing helped to eliminate early MMIC failures and exceed the median time to failure key performance parameters by 1,000 times.Raytheon engineers also enhanced their GaN MMIC computer design model, which resulted in first pass design successes, robust models incorporating temperature and process variations, and comprehensive design kits for use in two separate software packages.

"This program exploited the material properties of GaN semiconductors to enable devices and MMICs with higher power, higher efficiency and bandwidth, and superior performance than existing semiconductor technologies," Himes adds.

#### NEWS REVIEW

#### AJC deploys Infinera technology for submarines

AUSTRALIA JAPAN CABLE (AJC), operator of the AJC cable system between Japan and Australia, has deployed the Infinera DTN-X platform across its submarine network.

The InP based Infinera Intelligent Transport Network, featuring the DTN-X platform with SD FEC super-channels and integrated OTN switching, enables AJC to significantly expand their cable's capacity and rapidly deliver 10, 40 and 100 Gigabit Ethernet services.

Australia Japan Cable offers connectivity and bandwidth, serving their customers, with a 12,700 km submarine fibre optic cable network from diverse landings in Australia, Guam and Japan. leading service providers including Telstra, AT&T, NTT, Verizon and Softbank.

Infinera provides AJC with the DTN-X platform featuring long haul superchannels with SD-FEC based on one of the industry's most widely deployed Photonic Integrated Circuit and the FlexCoherent Processor, supporting up to 500 Gigabit per second (Gb/s) in a single line card.

The DTN-X platform is also equipped with 1 Tb/s per slot to support higher capacity 1 Tb/s super-channel line cards for future scaling needs.

"To meet the growing bandwidth needs of carrier, enterprise and ISP customers, AJC is significantly increasing the capacity of our network," says Philip

Murphy, Head of Engineering at Australia Japan Cable. "We selected an Infinera Intelligent Transport Network because it allowed us to scale capacity while simplifying operations.

"The Infinera Intelligent Transport Network provides AJC a mesh network of 500 Gb/s super-channels with soft decision forward error correction, ensuring the AJC network delivers increased network resiliency while delivering the capacity demanded by their customers," continues Andrew Bond Webster, Vice President Sales at Infinera.

AJC is composed of a consortium of

#### Soraa GaN LED lamps knock out halogen drawbacks

CALIFORNIA based gallium nitride expert Soraa has launched its first line of high colour and white rendering, high light output LED GU10 230V dimmable lamps.

The company says it has released a 10 degree spot version, not available in halogen or from other LED manufacturers, as well as a 25 degree version that has a peak intensity higher than halogen and all other LED GU10 products.

Now customers can buy transformer-free, full visible spectrum Soraa LED GU10 lamps that spectacularly render colours and whites; without beam striations, artefacts or multiple shadows visible in other manufacturer's LED products.

"Soraa's no compromise, full visible spectrum, high colour rendering LED lamps are simply the best on the market today. Our products excel in the key elements that define quality of light: light output, colour rendering, white rendering, and beam definition. The Soraa GU10 lamps provide unmatched light output, perfectly uniform beams, exceptional rendering of colors and whites, full dimmability, long lamp life, dramatically improved energy efficiency, and excellent compatibility," says Jeff Parker, CEO of Soraa. "All these features are made possible through our proprietary GaNon=GaN LED technology and innovative lamp design."

The company's continuous full visible spectrum Soraa Vivid 2 LED GU10 lamps, with a CRI of 95 and R9 greater than 90, render deep reds and cyans dramatically and accurately and have no artificial spectral "blue-peak". And just like natural light, the violet component of the full visible spectrum makes whites in fabrics and fibres stand out in their intended brightness and tint.

#### **NEWS** REVIEW

#### VPEC orders more Aixtron MOCVD reactors

VISUAL PHOTONICS EPITAXY CO. LTD. (VPEC) has ordered two more AIX 2600G3 IC MOCVD systems fully equipped to handle seven 6-inch substrates (7 x 6") in a single run.

VPEC placed the order to expand its microwave epiwafer volume production. The systems have been installed by Aixtron's local Taiwanese office.

Neil Chen, VPEC Vice President, comments, "Our RF microwave device business operation unit will be using the new systems to support our latest capacity expansion designed to meet ever higher demand from customers. We have been using the AIX 2600G3 for more than ten years now with our last multiple systems order having been completed in 2010. This last production capacity addition has put us in the solid commercial position to invest once more in Aixtron's high quality equipment."

VPEC chose the Aixtron systems due to

their robustness and extended uptime, along with high throughput. "Aixtron excels at supplying equipment with these features, along with prompt service and process support, all of which are vital for our successful business," Chen concludes.

Aixtron's Vice President Southeast Asia Christian Geng adds, "Driven by the demand for mobile phones and Wi-Fi, the need for RF power amplifiers based on compound semiconductor heterojunction bipolar transistors (HBTs) continues to rise and microwave device makers are presently adding MOCVD production capacities."

Visual Photonics Epitaxy Co. Ltd., a semiconductor epitaxial wafer pure play foundry, was founded in 1996 and is based in Ping-Jen City, Taiwan. The company provides solutions for wireless communications, optical fibre communications, and solar cell applications.

#### Plessey order ALSI laser tool

ADVANCED LASER SEPARATION INTERNATIONAL (ALSI) NV has received an order for a laser dicing system from Plessey Semiconductors for its Plymouth, UK based LED manufacturing facility. Keith Strickland, Chief Technology Officer at Plessey says, "An essential process step to achieve our cost and LED performance targets is the singulation of the finished wafer into LED dies.

ALSI demonstrated their experience in dicing and proved in short turnaround time to be able to meet our challenging process, cost and delivery requirements. "ALSI's multi-beam process will be key to the backend processes to be included in the fabrication line in Plymouth."

#### IHS: LED lamp retail price falls 11.8%

The December 2013 release of IHS' LED lamp retail price tracker has found the global average LED lamp retail price was \$24.5, indicating a fall of 0.4 percent in December over November 2013 and 11.8 percent fall over the same time last year.

IHS says that over the past twelve months the lumens per dollar ratio of LED lamps has increased by 31 percent to 29.9 lumens per dollar. IHS has been tracking the LED lamp retail pricing trends for over two years. Each month IHS analysts sample over 2,500 individual LED lamps sold in retailers across 15 countries globally.

#### Many players to monopolise chip on board LED market

ACCORDING to Infiniti Research's report, "Global Chip on Board LED Market 2014-2018", the global Chip on Board (COB) LED market will grow at a CAGR of 41 percent over the period 2013 to 2018. One of the key factors contributing to this market growth is the declining ASP of LEDs.

The global Chip on Board LED market has also been witnessing the increasing demand of COB LED in general lighting applications. However, the fluctuating global economic conditions could pose a challenge to the growth of this market.

The key vendors dominating this market space are Citizen Electronics co. Ltd., Cree Inc., Nichia Corp., Osram Opto Semiconductors GmbH, Philips Lumileds Lighting Co., Samsung Electronics Co. Ltd., and Seoul Semiconductor Co. Ltd. Other vendors mentioned in the report are Everlight Electronics Co. Ltd., Lumens Co. Ltd., and LG Innotek Co. Ltd.

Commenting on the report, an analyst from the team says the shift from traditional lighting sources to solid-state lighting technology has resulted in the wider adoption of COB LEDS.

COB LEDs are wide-area light emitters and thus, are increasingly used in highway and street lighting, which require large amounts of light spread across a large area. COB LEDs produce better colour mixing, better lighting effect, and require very low thermal resistance systems, thereby enhancing the total consumer experience. Thus, greater power density, efficient heat dissipation, small space requirement, and high performance makes COB LEDs more suitable than conventional LED packages for various general lighting applications.

**RADIANCE** BECAUSE NOT ALL SPUTTER SYSTEMS ARE THE SAME

evatec process systems

It's all about choice: cassette to cassette handling solutions, batch or single process modules, flexible process geometries, and a range of dep & etch technologies. The Radiance technology together with Evatec **HB LED** and **III-V** thin film know how gives you the best choice for the future. To find out more visit the Evatec web site **www.evatecnet.com/products/radiance-sputter-tool**

RADIANCE

LEDs • POWER DEVICES • TELECOMS • PHOTOVOLTAICS • MEMS • EVATEC - THE THIN FILM POWERHOUSE

www.evatecnet.com

#### NEWS REVIEW

# 3D-Micromac acquires the TLS-Dicing technology of Jenoptik

JENOPTIK is transferring its thermal laser separation (TLS-Dicing) technology as part of a so-called asset deal to 3D-Micromac AG.

As of January 1st, 2014, know-how, patents and results of the development from Jenoptik's Laser & Materials Processing Division have been transferred to 3D-Micromac AG in Chemnitz. Immediate commercialisation of the technology by 3D-Micromac will be possible with the transfer. With the acquisition, the company reinforces its know-how as a system provider for laser systems in the semiconductor industry and advances the expansion of its product portfolio in this area. Jenoptik's Laser & Materials Processing Division will continue in the future to focus on the

3D processing of plastics and metals, for example in the automobile industry.

According to Tino Petsch, CEO of 3D-Micromac AG, TLS-Dicing will enable the company to obtain a technology that will perfectly complement its product portfolio in the semiconductor industry and enable it to expand its market position.

Petsch adds, "In addition to component processing at wafer level we can now also offer innovative solutions for separating of microchips. In the coming months, we will continue to further develop the process in co-operation with the Fraunhofer IISB and implement it in industry-ready machine technology." "Jenoptik's Laser & Materials Processing

Division has increasingly focused on its core markets and sharpened its portfolio in recent months," says Dietmar Wagner, general manager of Jenoptik Automatisierungstechnik GmbH, following the contract's signing. 'We are pleased that with 3D-Micromac AG we have found a buyer for TLS-Dicing, which wants to successfully commercialise the technology in the shortest possible time".

TLS-Dicing (thermal laser beam separation) is used in the semiconductor industry's back-end to separate semiconductor wafer in components. A laser heats up the material locally and a cooling medium cools it down immediately afterwards.

The thermally induced mechanical stress leads to a complete cleaving of the wafer. The method is suitable for most brittle materials in the semiconductor industry, including silicon, SiC, germanium and GaAs wafers.

#### **Sem**r | Global Expositions

# EXPAND YOUR BUSINESS WORLDWIDE

without

nits.

#### Discover the Power of SEMI<sup>®</sup> Global Expositions

Whether you are looking to explore new regions, technologies, or markets, SEMI Expositions are the ideal platform to showcase your brand, connect to customers, and grow your business worldwide. Let SEMI help you build an exhibition and marketing program that gains maximum exposure and takes your business to the next level!

### For details on all SEMI Expositions, visit www.semiexpos.org

#### **Upcoming SEMI Expositions**

SEMICON Japan 2013 December 4–6 Chiba, Japan www.semiconjapan.org

• SEMICON Korea 2014 February 12–14 • Seoul, Korea www.semiconkorea.org

LED Korea 2014 February 12–14 Seoul, Korea www.led-korea.org **SEMICON China 2014** March 18–20 Shanghai, China www.semiconchina.org

**FPD China 2014** March 18–20 Shanghai, China www.fpdchina.org

**LED Taiwan 2014** March 20–22 Taipei, Taiwan www.ledtaiwan.org **SEMICON Singapore 2014** April 23–25 Singapore www.semiconsingapore.org

SEMICON Russia 2014 May 14–15 Moscow, Russia www.semiconrussia.org

**SEMICON West 2014** July 8–10 San Francisco, USA www.semiconwest.org **SEMICON Taiwan 2014** September 3–5 Taipei, Taiwan www.semicontaiwan.org

**SEMICON Europa 2014** October 7–9 Grenoble, France www.semiconeuropa.org

**PE 2014 Exhibition** and Conference October 7–9 Grenoble, France www.plastic-electronics.org

#### NEWS ANALYSIS

### Anvil to serve up cheap SiC switches

With Schottky diodes scheduled for next year and MOSFETs to follow, power semiconductor developer, Anvil Semiconductors, looks set to deliver what industry wants; efficient and cheap SiC devices.

In 2011, UK-based Warwick University launched Anvil Semiconductors to develop cheap but high quality SiC power semiconductor switches. Two years and some £2 million in funds later, the company has just won the National Microelectronics Institute Innovation in power electronics award and will soon deliver its first products.

SiC holds incredible promise as the material for tomorrow's power electronics applications. Devices are faster, more efficient and can withstand much higher voltages and currents than the straight silicon equivalent. SiC Schottky diodes have pretty much replaced silicon *p*-*n* diodes in switched-mode power supplies for computers, while SiC transistors are making

in-roads into hybrid and all-electric vehicle, photovoltaic applications and more. But despite rapid progress, cost is a major stumbling block. Anvil Semiconductors could make a difference. The company has developed a process to produce SiC power switches at a similar cost to silicon by growing layers of SiC on silicon wafers instead of using expensive bulk SiC.

"Our essential cost reduction is substituting a \$1000 4H-SiC substrate with a \$40 silicon substrate," states Anvil founder and managing director, Peter Ward. "We're [depositing SiC on] 100 mm silicon wafers at the moment but will get up to 200 mm wafers within our pre-production time-scales." Today, the likes of Infineon and Cree are busy developing SiC devices based on 4H SiC crystalline materials. This polymorph is grown via PVT as a single crystal and then sliced to produce relatively defect-free wafers, up to 6-inches in diameter. However, the growth process is slow and energy-intensive, yielding very pricey substrates.

But a second polymorph could provide an alternative. In theory, layers of 3C-SiC could be grown epitaxially on silicon wafers as this polymorph has a cubic crystal structure just like silicon. But while the resulting wafer could be produced much more cheaply than a 4H-SiC wafer, lattice mismatches and differences in thermal expansion coefficients between the 3C-SiC layers and silicon seed wafer induce in-plane stresses that cause wafer bowing. Device performance plummets and so manufacturers have stuck with the costly 4H-SiC wafers.

However, Ward, and colleagues, have developed a novel, low pressure CVD 3C-SiC growth process, that they claim bypasses these problems. Prior to SiC growth, a mask is placed over the silicon wafer to define structures in the scribe lines of the wafer. The team then deposits a 1.5  $\mu$ m-thick layer of heavily doped, dislocated material onto the silicon seed wafer. This helps to relieve stresses from lattice mismatches that lead to wafer bowing, and also allows vertical conduction through the interface.

"This layer is doped with dopants from the silicon wafer and nitrogen, allowing us to conduct through the silicon carbidesilicon heterojunction," says Ward. "So we can conduct from the top to the back of the wafer and have built devices where you cannot see additional resistance at the interface. This makes us very competitive with GaN-on-silicon, which can't conduct vertically."

In the same run, monocrystalline SiC is then grown in the die areas between the scribe lines, with polycrystalline SiC forming in the scribe lines. As Ward says: "We are effectively interfering with the epi-process and producing polycrystalline SiC in the scribe lines while growing single crystalline epilayers where we want to build the device."

Crucially, the resulting mesh of polycrystalline SiC helps to relieve the thermal expansion differential stresses across the wafer that also lead to bowing.

"Instead of trying to fabricate a 100 mm wafer, in terms of stress we are effectively making a 5 mm die," he adds. "This makes our process very scalable and essentially independent of wafer diameter."

Indeed, as Ward highlights, his company is only limited to 100 mm wafer sizes at the moment due to the industry's shortage of higher temperature, large wafer diameter epireactors. "Silicon reactors typically run at 1000 °C, but we need a reactor that has been designed to reach 1370 °C and the only ones that exist have been built for [100 mm] 4H SiC wafers," he explains. "So there aren't so many of these reactors right now, but we know where they are and who they belong to, and we've worked with most of these [organisations]."

Ward is also adamant the process is scalable to mass production, stating: " I have spent more decades than I would care to working with silicon, and having spent a lifetime We hope to stay as a niche product manufacturer but we see a very clear value chain from Schottky diodes to MOSFETs and probably to driver circuits as well.

manufacturing silicon devices, I see no reason why this shouldn't scale."

In the meantime, the Anvil team is busy building prototypes. A standard Schottky diode, similar to 4H-SiC versions but cheaper, is scheduled for release in 2014. And the company is also running a parallel MOSFET program, which could see prototype devices being released six months after the first Schottky diodes.

Ward won't talk about performance figures yet, only to say his team is pushing for very low on-resistance devices and is focusing on producing 650 V Schottky diodes and MOSFETs. As he explains, using 3C-SiC on silicon, his team can fabricate a very cost competitive 650 V device.

"Once we prove these 3C-SiC devices are a go-er we will start licensing commodity products," he adds. "We hope to stay as a niche product manufacturer but we see a very clear value chain from Schottky diodes to MOSFETs and probably to driver circuits as well."

> © 2014 Angel Business Communications. Permission required.

The Anvil Semiconductor team has been working with researchers at the University of South Florida to hone SiC device development and reactor technology

# Gan growth: an extra inch

GaN crystal newcomer, Fairfield Crystal Technology, is ready to take substrates to greater lengths.

WHEN IT COMES TO GROWING high quality, decent-sized GaN crystals, the US government is keen to fund companies that are making it happen.

In the last two years, vertically integrated developer of GaNon-GaN LEDs, Soraa, has won more than \$5 million from DoE agency, Advanced Research Projects Agency-Energy (ARPA-E), to develop large area, low cost GaN substrates. Meanwhile GaN crystal developer, Kyma, recently bagged some \$3 million to advance its technology for manufacturing substrates, shortly after releasing commercially available 2-inch GaN substrates.

But now, in the same wave of funding, a third company, Fairfield Crystal Technology, has also attracted \$1.5 million to develop a new technique to speed up the growth of GaN single-crystal boules. Perhaps lesser known in the GaN crystal field, the Connecticut-based crystal developer has been manufacturing semiconductor and optical crystal materials since 2004 – key crystals include AIN, ZnS and ZnO – but started looking at GaN two years ago.

"A lot of organisations take one crystal and focus on that but we've looked at different crystals which has given us a good understanding of crystal growth with different techniques, using a range of furnaces," says chief executive, Andy Timmerman. "You know we've done a lot on ZnO, have successfully launched AIN, so we see this as the next stepping stone to advance our crystal growth technology and work it into commercialisation."

Naturally, government backing helps. ARPA-E sees the material as crucial to a new generation of power devices, hence the hefty

#### NEWS ANALYSIS

weighting in its \$27 million SWITCHES program, Strategies for Wide Bandgap, Inexpensive Transistors for Controlling High Efficiency Systems.

And as Timmerman highlights only last month, the Department of Defense opened up solicitations for projects on GaN Technology for GPS L-band space power amplification, as part of its Small Business Innovation Research program. "GaN really has a good fit for our overall research and commercialisation of different products," he adds.

However, Fairfield Crystal is no stranger to US government interest in crystal growth. Preceding 2010, it had won just over \$1 million from the National Science Foundation to develop ZnS, CdS, ZnSe and AIN crystals.

Then come 2010, it received \$200,000 from the independent government agency to develop a novel approach, and demonstrate and sample 1-inch diameter free-standing GaN wafers for III-Nitride light emitters and detectors. Three years on, NSF funds run into the millions of dollars with the company working on pilot production of 2-inch GaN.

But what exactly is the novel approach? Timmerman remains tight-lipped; when asked if the process is based on either HVPE or ammonothermal methods, he confirms it is not based on the latter.

"It is the current state of the art. We know some folks are using ammonothermal, Kyma has been using a HVPE process, and others are looking at a combination of the two. But ours is different," he says. "It's using a combination of expertise from other crystal growth, be it AIN or ZnO, or even just some of the techniques we've gleaned from growing our optical crystals."

One such technique entails a novel method for growing a ZnO single crystal boule from a ZnO seed within an iridium crucible placed inside an induction-heated physical vapour transport (PVT) furnace system. According to Timmerman, the technique overcomes inadequacies in hydrothermal, CVT and melt growth techniques, but 'is a distinct technology differing from Fairfield's GaN technologies'.

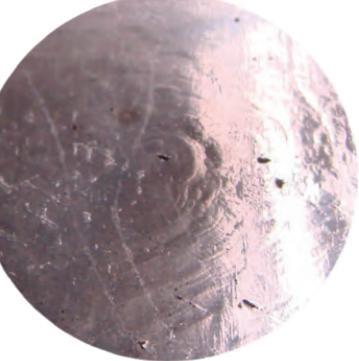

The top surface of a GaN single crystal of about 1-inch in diameter produced at Fairfield Crystal; the company has achieved a dislocation density of 1 X  $10^7\,\rm cm^{-2}$

"However, we have found that having a very very clean source material is a priority [for the GaN process]," he adds. "And we've developed an in-house process with high quality source material.

With this in hand, the team now intends to drive GaN substrate costs down by growing longer boules and slicing more wafers per growth run. And of course, a crucial part of the ARPA-E grant, is to grow 3-inch GaN crystals, within the next three years.

"The time frames are very aggressive, especially since in a number of years other organisations have also been trying," admits Timmerman. "We're cautious but confident we can get there, although we are not dismissive of the challenges."

> © 2014 Angel Business Communications. Permission required.

The team now intends to drive GaN substrate costs down by growing longer boules and slicing more wafers per growth run. And of course, a crucial part of the ARPA-E grant, is to grow 3-inch GaN crystals, within the next three years

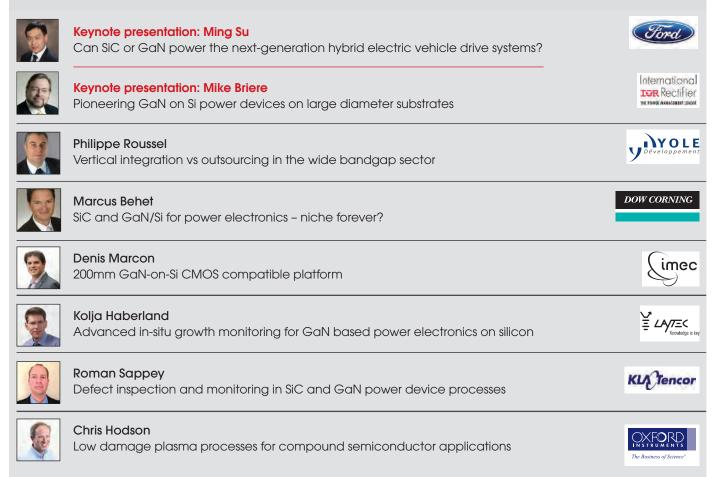

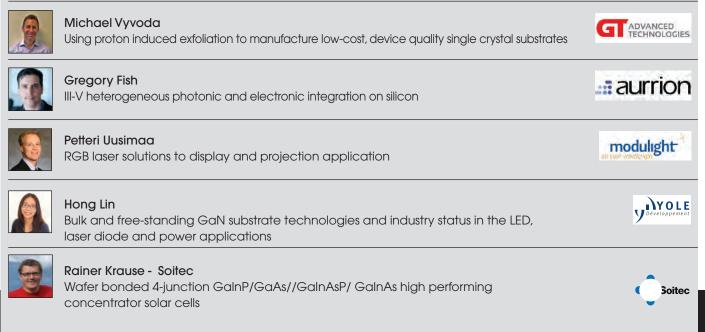

#### 4<sup>th</sup> CS International Conference

#### 6 themes and 36 inspiring presentations\*

## Gain a comprehensive overview of the entire compound semiconductor industry at this leading international conference.

The 4th CS International conference will be held at the **Sheraton Frankfurt Airport Hotel in Germany over two days on Tuesday 18<sup>th</sup> & Wednesday 19<sup>th</sup> March 2014.** Delegates will have the unique opportunity to network with the world's top executives in compound semiconductor technology. Hear about the breakthroughs in device technology; insights into the current status and the evolution of compound semiconductor devices; and details of advances in tools and processes which could help boost fab yields and throughputs. This event is held once a year and brings together the best in class of the compound semiconductor industry.

#### Book your place NOW

Please visit www.cs-international.net/register.php for further information

#### Chaired by

Andrew Nelson

#### LEDs

LEDs are the dominant source for backlighting screens of all sizes. To penetrate new markets and grow revenues, can chipmakers now trim the cost-per-lumen of the LED or equip the device with additional features?

|   | Keynote presentation: Young Soo Park<br>Slashing LED costs with 200 mm silicon substrates                                            | SAMSUNG                      |

|---|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|   | William Henry<br>Applications and opportunities for MicroLED emitters                                                                | NILED 😽                      |

|   | Pallavi Madakasira<br>LED light bulbs: When and how will the lighting of tomorrow become the lighting of today                       | Iuxresearch                  |

|   | Ulrich Steegmueller<br>Success factors in the increasingly competitive LED ecosystem                                                 | OSRAM<br>Opto Semiconductors |

| R | David Kepniss<br>Sub part-per-billion analysis of high purity hydrogen - process improvement applications with<br>the HEMS™ analyzer | Power+Energy                 |

|   | Reinhard Benz<br>Increasing LED performance and reducing production costs to accelerate the growth of LED ligh                       | hting                        |

#### Integration of CMOS and III-Vs

Silicon is running out of steam, and the future is widely tipped to be high-mobility channels made from germanium and III-Vs. But how will these materials be introduced in the world's leading silicon foundries?

#### **Keynote presentation: Jean Fompeyrine** Co-integration of III-V and Ge CMOS

The University of Tokyo

#### Thorsten Matthias

Direct wafer bonding: Enabling technology for future photonic and electronic integration

#### Shinichi Takagi

III-V and germanium FET technologies on Si platform

#### Aaron Thean

Beyond silicon CMOS: Transforming transistors with heterogeneous material integration

#### **Power Electronics**

Silicon has dominated the power electronic market for decades, but wide bandgap semiconductors will soon replace this material. What's the primary role for SiC, and where will GaN feature?

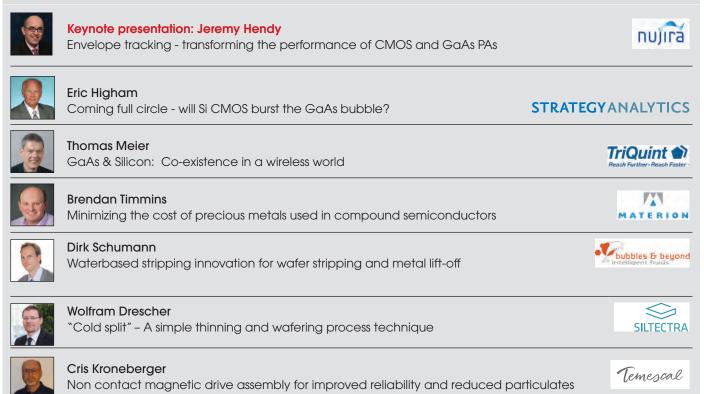

#### Front Ends for Mobile Devices

Handset front-ends are becoming more complex, due to an ever-increasing number of bands used for mobile communication. Will this trend play into the hands of GaAs chipmakers? Or is silicon CMOS technology going to grab market share?

#### Lasers, PICs and PV

Rocketing levels of internet traffic are putting greater and greater strain on optical networks and data centres. Can this be addressed by advancing the performance of conventional lasers, or does the market need to turn to greater use of PICs?

ONECHIP

#### Keynote presentation: Michael Lebby

Photonic integration in InP: A regrowth-free platform for the fabless manufacturing model

#### Wide Bandgap RF Devices

GaN and SiC have a great set of attributes that make them very promising materials for producing RF devices. But are they now fulfilling their potential and netting substantial sales?

#### Keynote presentation: Andrew Barnes

Overview of GaN reliability improvement activities at the European Space Agency

#### Chris Horton Enabling material solutions for GaN in the RF arena

OMMIC

Innovating with III-V

#### Marc Rocchi

100nm GaN/Si mmW foundry service and MMICs

#### Book your place NOW

Please visit www.cs-international.net/register.php to secure your place

Connecting the leading compound semiconductor industry insiders

#### NEWS ANALYSIS

# GaN-on-silicon LEDs slated

### for massive market growth

IHS predicts silicon-based LEDs will nearly rival sapphire-based devices on market share come 2020.

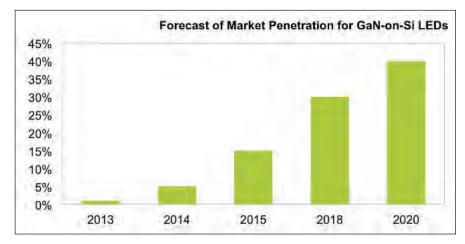

LATE LAST YEAR, analyst business, IHS, forecast GaN-on-silicon LEDs will increase market share from today's 1 percent to an incredible 40 percent by 2020. This monumental 69 percent compound annual growth rate is at odds with other 2013 forecasts, but IHS analyst and author of GaN LEDs on Silicon -World - 2013, Dkins Cho, is certain the technology is poised for strong growth. "In 2013, 95 percent of GaN LEDs were manufactured on sapphire wafers with only 1 percent manufactured on silicon," says Cho. "Come 2020, 40 percent will be manufactured on silicon, maybe 3 percent on SiC, with the remainder on sapphire substrates."

According to Cho's forecast, the GaNon-sapphire LED is still set to retain the largest market share – but only just. However, given GaN-on-silicon's technical challenges, such as the lattice mismatch between GaN layers and the silicon wafer, as well as questionable manufacturing yields, is his forecast of near-market domination realistic?

Cho thinks so. As he points out, a few leading suppliers, most notably in Asia, have recently made good progress performance as well as throughput and yield on 6-inch to 8-inch wafers. Declining to name companies he says: "Looking at the leading GaN-on-silicon LED companies, performance-wise, these manufacturers are producing devices with a similar performance to sapphirebased LEDs. Production yields are more of a problem, but some companies have already overcome this." As Cho highlights, GaN-on-silicon LEDs have been successfully fabricated on 8-inch wafers using legacy CMOS fabrication facilities and equipment with just minor modifications. Indeed, many GaN-onsilicon LED heavyweights already own legacy 8-inch CMOS facilities, and could well be ready to migrate manufacturing to these fabs.

"Samsung and Toshiba already have CMOS semiconductor lines and have produced good devices," he says. "I also expect to see at least one Taiwan-based and two China-based companies enter the market."

The draw to silicon is largely ease of manufacturing and being able to use existing inspection tools. "Silicon has better machining characteristics than

Forecasts of Market Penetration for GaN-on-silicon LEDs

sapphire for laser cutting, grinding and polishing," says Cho. "CMOS fabrication on silicon has a long history of production using state-of-the art technologies so there is much greater process knowledge [than sapphirebased LED production]. And the process equipment is well developed and deployed over the entire front-end and back-end process," he adds. "GaN-onsilicon LED production can make use of legacy tools and facilities... to enhance process yields as well as overall yields and through-puts."

Legacy CMOS equipment can also be used for *in-situ* monitoring and inspection, potentially leading to faster improvements in performance than has been achieved with sapphire-based LEDs to date. Still, Cho does not expect the likes of Toshiba and Samsung to convert to CMOS manufacturing immediately. "It is unlikely re-purposing will happen overnight," he says. "Instead we forecast a shift during the coming years."

#### **CMOS rivals**

While manufacturers of GaN-on-silicon LEDs will, without a doubt, chip away at the sapphire market share in coming years, other analysts do no concur with IHS's bold predictions. In the Summer of 2013, Lux Research analyst Pallavi Madakasira released her report *Dimming the Hype: GaN-on-silicon Fails to Outshine Sapphire by 2020.* As she asked *Compound Semiconductor* at the time: "Can we really expect an organisation that has invested billions of dollars in its GaN-on-sapphire line to stop running that?" Questioning the performance of GaN-on-silicon LEDs, she also stated: "You have to remember that [GaN-onsilicon LED manufacturers] are catching up on a moving target. GaN-on-sapphire performances will keep improving and costs are going to keep coming down."

And then there's the added complication of Cree. With its continued investment in SiC production and successful transition from 4-inch to 6-inch diameter wafers, can industry really expect the US-based industry heavyweight to lose out to silicon rivals in such a big way?

Still, Cho is standing by his forecasts. Cheap fabrication costs aside, he believes a rising demand for LEDs for medium power lighting as well as applications such as LED-backlit LCD displays will boost GaN-on-silicon LED manufacturing. He also highlights how he has analysed the manufacturing cost and price behaviour of major suppliers across the supply chain as well as interviewed GaN-on-silicon developers and companies not moving to GaN-onsilicon technology.

"The companies making GaN-on-silicon LEDs have sold out production," he says. "Sapphire and silicon carbide market share will continue to go to silicon."

© 2014 Angel Business Communications. Permission required.

Market analyst Dkins Cho expects at least one Taiwan-based and two China-based companies enter the GaN-on-silicon LED market

# **Rocky road** to real power conversion

The market-ready high voltage GaN-on-silicon power device has been a long time coming. Compound Semiconductor asks Venture-Q's Zel Diel if the industry will deliver soon.

IN 2010, ZEL DIEL, managing director of US-based power electronics analyst business, Venture-Q, started investigating how and when GaN-on-silicon devices for power conversion applications would be commercialised. Within months, he had concluded that by 2016 industry would see high-voltage FETs in low quantities so designers could use them to build demonstration systems. These structures would be deposited on 200 mm silicon wafers to achieve an acceptable cost parity with silicon alternatives.

Nearly four years on and having just unveiled his latest report on commercialization strategies for GaN-on-silicon power devices, Diel's time-frame has shifted. "We're not so far off now. By 2018 system designers will be able to say, yes, I can buy [HEMTs] for \$5 or \$6 and at a system level cost parity," he says.

Still, the road to true commercialisation is going to be rocky. As Diel asserts, time and time again, market research forecasts, largely relying on vendors' unrealistic product availability timetables, have underestimated the challenges GaN-on-silicon developers face and proven optimistic.

While Efficient Power Conversion (EPC), US, introduced the first commercially available low voltage GaN-on-silicon HEMT nearly four years ago, this company and every other vendor has since struggled to deliver commercially-viable high voltage – 600 V – devices. EPC has repeatedly pushed back delivery of high voltage devices and the only generic 600 V GaN-on-silicon HEMT device publicly introduced by Transphorm has been offered to select partners under non-disclosure agreements.

So why the slow progress? For starters, myriad industry infrastructure constraints exist. "We are dealing with a completely different technology in a system level design

that power system designers have never seen, never had experience with and never been trained with," he says. "We have no reliability systems in industry, only JEDEC, but this is a silicon standard so qualifying for JEDEC doesn't mean a thing; you can't even qualify a part and send it to be integrated into a system as there is no standard on paper."

What's more, both GaN-on-silicon developers and oscilloscope manufacturers have also highlighted the test and measurement challenges posed by high-voltage, high-bandwidth GaN devices. "Tektronix has said it had no oscilloscope fast enough to measure switching in these devices," highlights Diel.

And then there's the technology issues. While the lattice mismatch between the silicon substrate and GaN layers has hampered development, so-called current collapse is proving to be the primary stumbling block stymieing progress.

The phenomenon is an inherent attribute of GaN-on-silicon, as well as GaN-on-SiC HEMT device structures, which manifests as an increase in the device's on-resistance during high voltage operation, degrading performance. Crucially, current collapse, especially in GaN-on-silicon devices, is exacerbated at 400 V operation and higher and is now the the primary focus of research and development efforts in industry and academia.

"Current collapse is the kiss of death and we cannot find a cure," says Diel. "Since 1999 at least 1000 PhD theses have been written on this and still people are struggling with the problem. Vendors are tackling this challenge but no-one has a solution."

So don't these technology challenges twinned with industry infrastructure constraints make a 2018 commercialisation timeline ambitious? Diel thinks not, highlighting recent industry developments that signal real progress.

In October 2013, Powerdec, a developer of GaN-on-silicon HEMTs, demonstrated a 600 V, 10 A HEMT it had produced alongside the University of Sheffield, UK. The device was fabricated using the organisation's proprietary polarisation super-junction process, which Powerdec claims suppresses current collapse.

And then in November 2013, Fujitsu, and University of California Santa Barbara spin-off, Transphorm, signed a deal to integrate the GaN power device businesses of each. The move will boost the market competitiveness of Transphorm's cutting edge GaN technology by capitalising on Fujitsu's manufacturing prowess. In short, industry should see high volume, high performance and cheap GaN devices sooner rather than later.

"Due to long-time research at UCSB and with Cree, Transphorm's technology is very advanced... but moving into manufacturing brings many complex issues," says Diel. "Transphorm has realised this, and this where Fujitsu, a manufacturing powerhouse, comes in."

And we can expect more of the same. Diel predicts we will soon see EPC, in reality the only vendor currently offering GaN-on-silicon HEMTs on the open market, teaming up with a systems manufacturer.

"More and more vendors are now recognising that what they are dealing with is not as simple as research and development presented at conferences," he says.

"I speculate that this Fujitsu-Transphorm deal will be repeated quite frequently as we go forward, and those that don't do this will become laggards."

> © 2014 Angel Business Communications. Permission required.

# GaN advances into **defence electronics**

ABI Research analyst, Lance Wilson, predicts GaN will drive pulsed RF power device market growth. **Compound Semiconductor finds out more.**

WITH THE MARKETS for pulsed RF power semiconductor devices set to top \$250 million by 2018, the future for GaN in defence electronics applications looks very healthy.

As Lance Wilson, ABI Research analyst and author of a recent study *Pulsed RF Power Semiconductors* puts it: "Despite everything in the news about defence markets being cut, we are going to see a higher percentage of spending going towards defence electronics."

Wilson has identified what he calls a 'quantum shift' in defence-related procurement away from capital-intensive equipment such as fighter aircraft and towards relatively cheap, electronicsweighty applications such as radar and electronics warfare.

"This does not mean the defence electronics industry gets a free ride – the next three to five years will be tough – but once medium term budget battles are over, I think defence electronics is going to come out as the big winner," he says.

Right now, the pulsed RF power device market is crowded to say the least. Myriad manufacturers from Cree, Freescale, M/A-Com to Microsemi, RFMD, TriQuint, and more, are developing devices based on pure or various blends of silicon, SiC, GaAs and GaN.

Silicon-based devices dominate the sub-1 GHz radar market, both GaN and silicon development is rife for 1-3 GHz markets while in radar applications at 3 GHz and more, market share is all going to GaN. But still, product differentiation isn't easy and consolidation is to be expected.

"Certainly over the next five years we will see consolidation within these frequency divisions," says Wilson. "This isn't based on technical issues but rather on economic and market forces."

The analyst won't name names, but asserts companies with a track record of working with government and defence organisations will have an advantage over new entrants.

"Northrop Grumman and Raytheon, for example, also make their own GaN and use it in radar systems," he adds. "I don't want to say this gives them an advantage but it gives them a manufacturing efficiency that other companies might not have."

#### GaN drives growth

Crucially, however, Wilson believes GaN is going to drive most of the market growth between now and 2018. Beyond 4 GHz frequencies, GaN, with its high voltage, high power and high frequency performance, is the only truly viable option.

As Wilson explains, silicon devices can't operate at these frequencies while GaAs cannot produce the peak power levels demanded by most pulsed applications here. As a result, all the above 4 GHz frequency applications that were served by microwave tubes are now open to GaN, and so solid-state device manufacturers are now turning to GaNon-silicon and GaN-on-SiC devices.

"Most pulsed silicon device suppliers are going into GaN as they recognise a large portion of the business will drift over to the material and they don't want to lose market share," says Wilson. "And for those companies that don't appear to have a GaN program, they do, they all do. Some companies are less vocal than others but all the principle silicon manufacturers have robust GaN development."

Still, this doesn't sound the death knell for manufacturers of vacuum tubes for

#### NEWS ANALYSIS

radar applications. As Wilson asserts, these manufacturers 'have not been sitting still and watching their business disappear' and have been developing smaller and smaller micro travelling wave tubes (TWTs) for high power and wideband RF transmission, that are similar in size to solid-state amplifiers.

"The wide bandwidths of these TWT amplifiers are very difficult to replicate in solid state, so not all of the tube market will go over to GaN," he says. "And at very higher power – hundreds of kilowatts or megawatts of power – TWTs will never be replaced by solid -state amplifiers."

But when it comes to GaN, does Wilson see a winning technology emerging? Not yet.

While many manufacturers are focusing on GaN-on-SiC devices, US-based Nitronex, for example, is busy churning out GaN-on-silicon RF power devices based on its proprietary SIGANTIC manufacturing process. Here, buffer layers, including an AIN layer, are deposited on the silicon wafer, which in Wilson's words is 'not an easy process'.

"Most people are opting for the epitaxial GaN device on a SiC substrate as there is much better thermal matching," he says. "From a practical standpoint, GaN on silicon substrates are the way things are going, but which one is better from a technology standpoint? The jury is out."

© 2014 Angel Business Communications. Permission required.

# Turbocharging channels with compounds

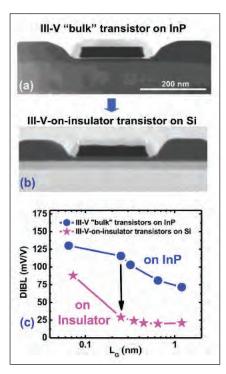

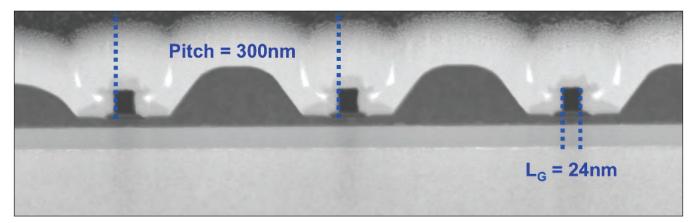

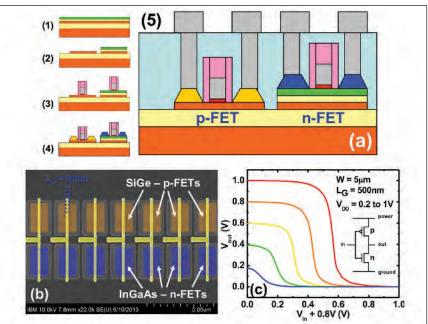

To maintain the improvements in efficiency that traditionally result from shrinking transistor dimensions, foundries will soon have to replace silicon channels with those based on higher mobility semiconductors. This move, a monumental upheaval for the silicon industry, could be easiest to implement by turning to engineered wafers with separate layers for the p-type and n-type transistors, argues Lukas Czornomaz from the Advanced Functional Materials Group at IBM Zurich.

FOUR DECADES of scaling CMOS technology has revolutionized our society. By making transistors ever smaller, faster, cooler, and cheaper, and being able to pack billions of them on the same chip, engineers have enabled the smartphone to become a commodity. This sleek, portable device has fundamentally changed the way we live: Now, wherever we are, we can be participating members of social networks and surfers of the web.

Performance of the smartphone will continue to increase, but it will not be easy to realise further gains in the computational capability of the chips that lie at the heart of these devices. That's because the microelectronic industry is facing some really serious challenges in shrinking dimensions beyond the 14 nm node.

Even getting as far as we have today has not been easy. For the last decade, pure geometrical scaling has failed to deliver the expected benefits in terms of performance and power consumption, and industry has gradually moved to innovation-driven scaling, bringing to market chips based on the likes of strained silicon-on-insulator, high-K/ metal gate technology and tri-gate devices. Now researchers everywhere are foreseeing that in the coming years, silicon – regardless of its form - will probably fail to meet the ultra-low power consumption targets imposed by the exploding demand of 'Mobile-Everywhere' applications.

The main lever for power scaling is the operating voltage of the chips. The target is to trim this from 0.8-0.9 V, which is where it stands today, down to 0.5 V. This cut in operating voltage must go hand-in-hand with a maintaining of the drive-current for the transistors, in order to ensure no reduction in performance. But realising this will not be easy. It will require the charge carriers in the

transistor's channel – either electrons or holes, depending on the particular transistor – to travel far faster from the source to the drain. Today, increases in the charge carrier velocity in silicon often result from the application of very high levels of strain in the material, but the opportunities for further gains are now minimal, especially for *n*-type transistors.

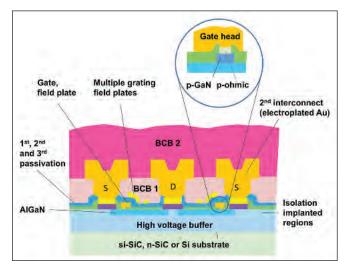

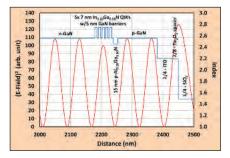

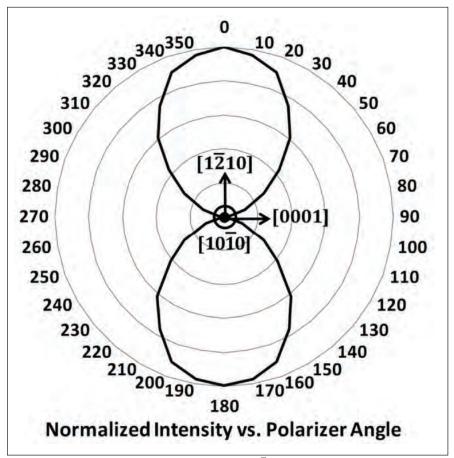

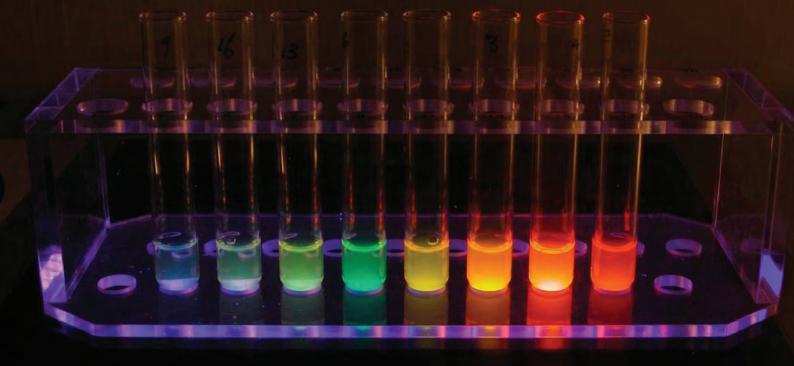

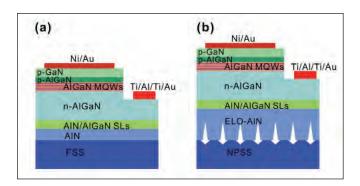

What is possible is that the next revolution in the semiconductor industry will come from the introduction of compound semiconductors as channel materials. Electron and hole mobilities in silicon are just 1400 cm<sup>2</sup> V<sup>1</sup> s<sup>-1</sup> and 450 cm<sup>2</sup> V<sup>1</sup> s<sup>-1</sup>, respectively, and far