Volume 20 Issue 7 2014

🔁 @compoundsemi

www.compoundsemiconductor.net

#### Great GaN yields better devices

# Cooling HEMTs with diamond

#### Turbo-charging the VCSEL

# Bigger wafers for GaN-on-silicon

# Translucent

Perfecting GaN-on-silicon

**COMPOUND** SEMICONDUCTOR Review, News Analysis, Features, Research Review and much more. Free Weekly E News round up , go to www.compoundsemiconductor.net

# 200mm GaN-on-Si Batch Reactor

# 5x200mm

# AIX G5+

#### AIX G5+ for GaN-on-Si

- Dedicated technology package

- Compatible with the AIX G5 HT platform

- Enables Si-style mass manufacturing

- Builds on planetary technology: Excellent and symmetric uniformities, controlled bow behavior, using standard Si substrates.

AID

AIXTRON SE · info@aixtron.com · www.aixtron.com

# editorialview

by Dr Richard Stevenson, Editor

# A really radical device

AT THE HEART OF EVERY ISSUE OF this magazine lie a collection of features detailing breakthroughs at the chip level. All these articles describe some aspect of novelty, which is more radical in some cases than others.

Breakthroughs that are important, but not revolutionary, would include improvements to existing device architectures. This might be the insertion of a superior photonic

structure into an LED that leads to an increase in extraction efficiency, a new gate stack that cuts the density of interface traps in a III-V MOSFET, or a different style of field plate that trims the leakage current in a GaN HEMT.

More radical is the creation of a new device. It might be formed by building an entirely new structure, or it might result from merging two devices into something that exceeds the sum of the parts.

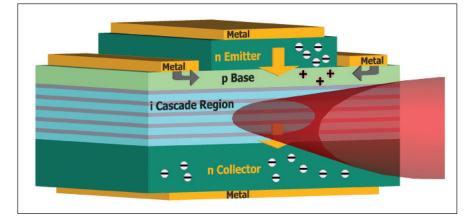

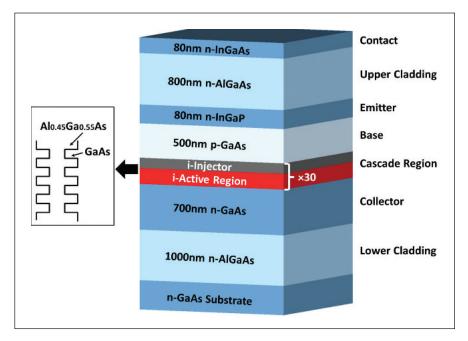

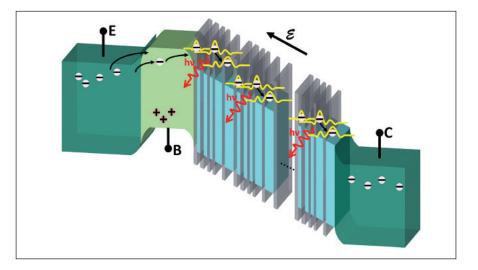

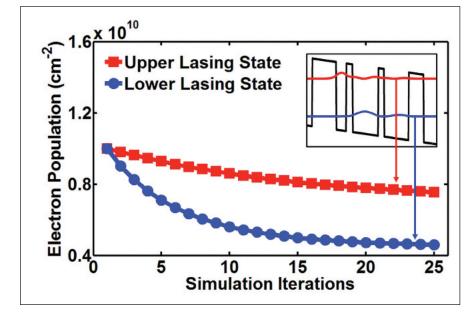

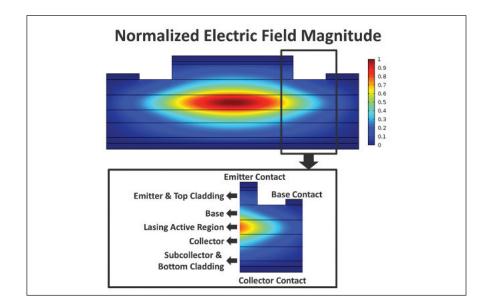

In this issue, we have a contribution in this latter vein from John Dallesasse and Kanuo Chen from the University of Illinois at Urbana-Champaign. This duo has combined a quantum cascade laser (QCL) and a transistor to create a novel source that can produce emission from the mid infrared through to terahertz frequencies.

Their three-terminal hybrid improves on the capability of the QCL, a promising device for gas sensing. With the QCL, changing the operating voltage shifts the emission wavelength, making it possible to conduct a frequency sweep through the absorption peak of gas molecules. However, when the operating voltage of the transistor is changed, it alters the injection of carriers into the active region, and thus the output power of the laser.

Turning to the transistor-injected QCL eliminates this variation in output power, because it is then possible to independently control the injected current and the voltage across the active region. What's more, by dithering the base-collector bias voltage at a fixed emitter-base bias, the laser's frequency can be modulated, aiding the detection of chemical species.

But will this device be used for gas sensing on a grand scale, or will it be confined to academia? Well, signs are good for commercialisation. Its design is similar to a HBT – the main differences are the addition of optical confinement layers on the top and bottom of the device and the inclusion of a cascade region. This means that it should be possible to make the device in a GaAs IC foundry. So maybe, just maybe, this device will be more than just radical – it will be commonplace too.

| Editor Richard Stevenson                    | richardstevenson@angelbc.com                    | Chief Operating Officer Stephen Whitehurst stephen.whitehurst@angelbc.com<br>+44 (0)2476 718970 |  |  |

|---------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|

| Contributing Editor Rebecca Pool            | +44 (0)1291 629640<br>editorial@rebeccapool.com | Directors Bill Dunlop Uprichard – CEO, Stephen Whitehurst – COO, Jan Smoothy – CFO,             |  |  |

| News Editor Christine Evans-Pughe           | chrise-p@dircon.co.uk                           | Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal, Jason Holloway.                        |  |  |

| Director of SEMI Publishing Jackie Cannon   | jackie.cannon@angelbc.com                       |                                                                                                 |  |  |

| U U                                         | +44 (0)1923 690205                              | Published by Angel Business Communications Ltd,                                                 |  |  |

| Senior Sales Executive Robin Halder         | robin.halder@angelbc.com                        | Hannay House, 39 Clarendon Road, Watford, Herts WD17 1JA, UK.                                   |  |  |

|                                             | +44 (0)2476 718109                              | T: +44 (0)1923 690200                                                                           |  |  |

| Sales Manager Shehzad Munshi                | shehzad.munshi@angelbc.com                      | F: +44 (0)1923 690201                                                                           |  |  |

|                                             | +44 (0)1923 690215                              | E: ask@angelbc.com                                                                              |  |  |

| USA Rep: Brun Media: Tom Brun               | E: tbrun@brunmedia.com                          |                                                                                                 |  |  |

|                                             | Tel: +001 724 539-2404                          | Angel Business Communications Ltd                                                               |  |  |

| Brun Media: Janice Jenkins                  | E: jjenkins@brunmedia.com                       | Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK.                       |  |  |

|                                             | Tel: +001 724-929-3550                          | T: +44 (0)2476 718 970                                                                          |  |  |

| Director of Logistics Sharon Cowley         | sharon.cowley@angelbc.com                       | F: +44 (0)2476 718 971                                                                          |  |  |

|                                             | +44 (0)1923 690200                              | E: info@angelbc.com                                                                             |  |  |

| Design & Production Manager Mitchell Gaynor | mitch.gaynor@angelbc.com                        |                                                                                                 |  |  |

|                                             | +44 (0)1923 690214                              |                                                                                                 |  |  |

| Circulation Director Jan Smoothy            | jan.smoothy@angelbc.com                         | Angel 🚫 DY Correcycle                                                                           |  |  |

|                                             | +44 (0)1923 690200                              | BUSINESS COMMUNICATIONS When you have finished with this magazine please recycle it.            |  |  |

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publisher. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Ctd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Periodicals postage paid at Jamaica NY 11431. US Postmaster: Send address changes to Compound Gerifician Langes Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: Pensord Press. ISN 1096-598X (Print) ISN 2042-7328 (Online) © Copyright 2014.

# connecting the compound semiconductor community

# features

# 28 Perfecting GaN-on-silicon power electronics

Inserting rare earth oxides increases material quality, trims wafer bow and boosts transistor performance.

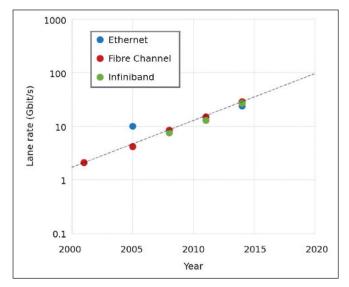

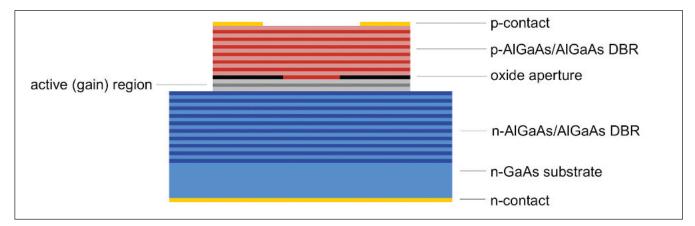

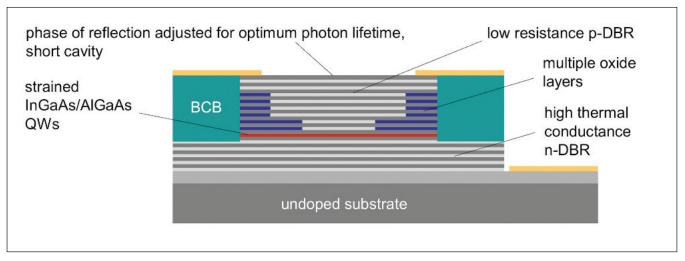

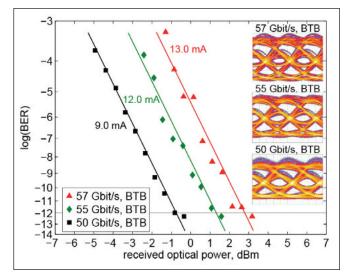

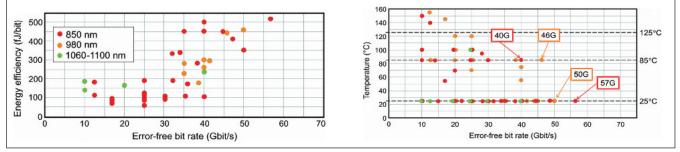

# **34** Faster, more frugal, greener VCSELs

VCSELs that excel in speed and efficiency can aid data centres and play a role in night vision, ultra-high density magnetic storage, cosmetics and healthcare.

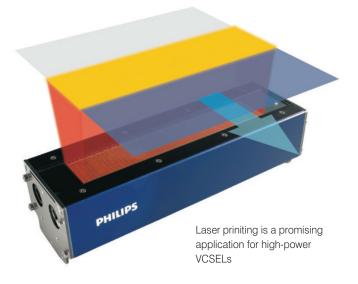

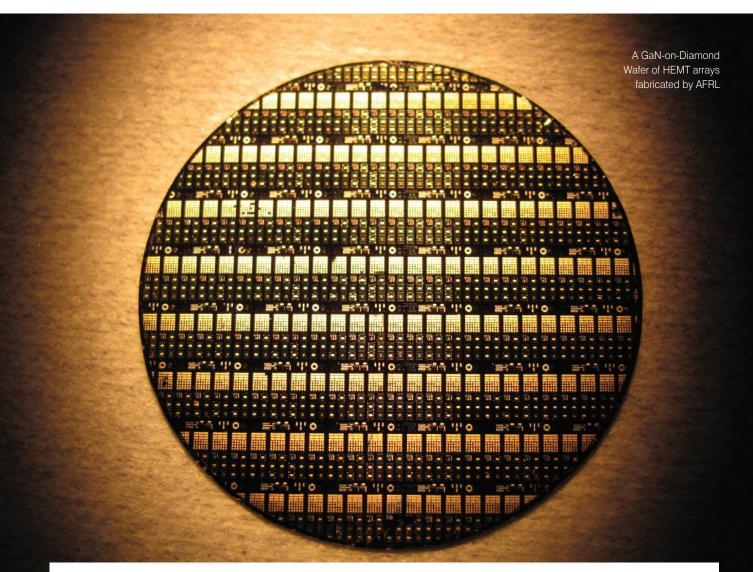

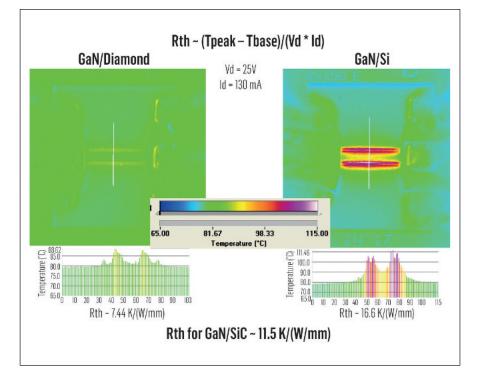

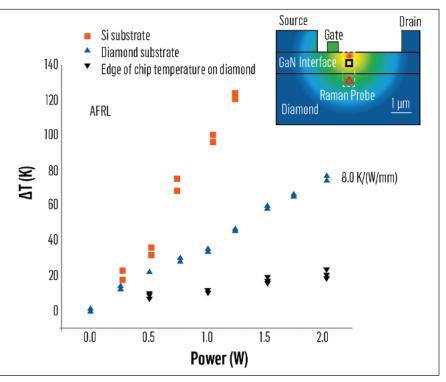

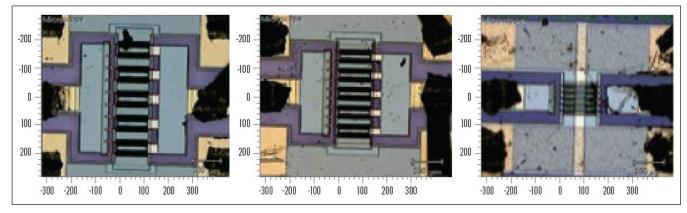

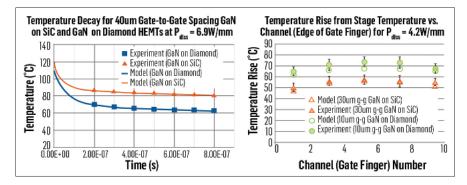

# 41 Keeping cool with diamond

By sucking heat from GaN HEMT better than any other substrate, diamond enables a dramatic reduction in finger spacing.

# 48 Slashing GaN costs with silicon

Production costs for GaN-based devices will plummet when epilayers are formed on 200 mm silicon.

# 54 Increasing the availability of GaN HEMTs

A robust, reliable foundry process will spur a proliferation of GaN applications

# 60 Fantastic foundation yields great devices

GaN substrates formed from ammonothermal growth underpin the fabrication of devices delivering outstanding levels of performance.

# **66** Accessing the mid-infrared and beyond

Merging the quantum cascade laser and transistor promises new applications involving mid-infrared wavelengths through to terahertz frequencies.

#### news

- 06 Global LED market to reach \$42.7 billion by 2020

- 08 Emcore announces sale of space PV activities

- 10 Dow Corning sets new standard for 150mm SiC wafer crystal quality

- 12 Plessey adds in-house LED assembly line to UK facility

- 13 IQE, Win and NTU agree to create compound semiconductor centre in Singapore

- 14 Sofradir's megapixel IR detector for space program

- 15 Merck KGaA to acquire Sigma-Aldrich

#### news analysis

- 16 Electric vehicles: SiC and beyond

- 18 BluGlass rises to MOCVD challenge

- 20 Infineon and International Rectifier: what next?

#### research review

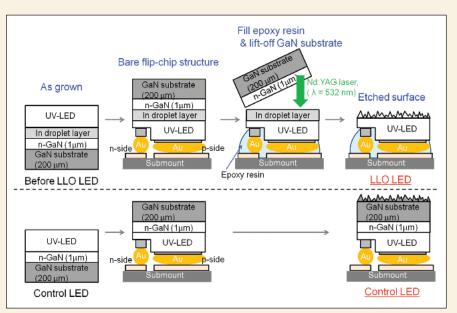

- 70 Laser-lift off for ultraviolet LEDs

- 71 Dislocation-free GaAs on silicon offers a route for scaling CMOS

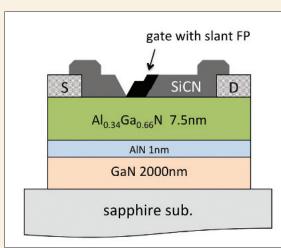

- 72 Slanted field plates spawn superior HEMTs

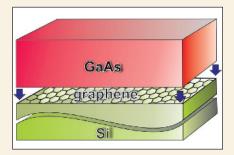

- 73 Graphene unites silicon and GaAs

41

## **NEWS** REVIEW

# Global LED market to reach \$42.7 billion by 2020

ACCORDING to a new market research report *Global Light Emitting Diode* (*LED*) *Market (Technology, Application and Geography), 2013 – 2020* by Allied Market Research, the LED (chips and components) market is forecast to reach \$42.7 billion by 2020, registering a CAGR of 13.5 percent from 2014 to 2020.

Asia Pacific leads the LED technology market with approximately three quarters of the global electronics manufacturing industries. North America, due to its hightech forensic and medical applications leads the market for UV LEDs. It is anticipated that LED lights will command about 20 percent share of the global lighting market by 2020. This will be equivalent to two thirds of the revenue for LED. However, the demand for basic LED in backlighting applications would decline as OLED broadens its horizon of applications and would eventually supersede basic LED mobile displays.

UV LEDs are mainly used in medical treatments and forensic tests. According to the report, further development of the market is expected as companies rigorously work out acquisitions to expand their product portfolio and applications. In January 2013, Noblelight acquired Fusion UV, manufacturer of UV LED technology. Developed regions, though, are early adopters of the UV LED technology; the healthcare sector in developing regions such as Asia Pacific is also contributing to the growth of the technology. The growing medical tourism and lower cost of treatments will strengthen the adoption of UV LED technology in developing regions.

Governments across the globe are implementing LED lighting in most of the public settings to save energy. The US government has already started replacing the conventional street lights with LEDs, which it is anticipated to complete by the end of 2014. Such developments will be instrumental in the growth of the LED market. "The growth in revenue will be slower than the rise in unit sales of LEDs due to the constantly declining price of LEDs; however, the overall market would grow at a constant pace due to growing demand for LEDs and expanding applications" states

AMR analyst Ranjan Singh. "Continuous development in the technology suggests huge underlying potential for OLEDs during the forecast period," adds the analyst citing the recent rollouts of OLED mobile handsets by Samsung and Nokia. High brightness (HB) LEDs hold nearly 60 percent of the market share as it can provide much brighter light with lower voltages as compared to other market alternatives. The rapid growth in 4K TV segment suggests that HB LED will continue to hold the key to the growth of LED technology market. Major companies such as Samsung SDI and RIT Display are investing substantially on the development of advanced OLED display technologies.

Rising application of LED in general lighting has compelled manufacturers to concentrate on new LED lighting products and expand their production. OSRAM opened its LED assembly plant in Wuxi, China, to expand its fully loaded LED capacities and also to strengthen its market position in the global LED market. The company has chosen the plant location in China to capture the highly potential Asian market.

Notable players in this space include and profiled in report are American Bright Optoelectronics, Cree, International Light Technologies, Ledtronics, Philips Lumileds Lighting Company, Samsung Electronics, Seoul Semiconductor, OSRAM Licht AG, Nichia, LG Innotek, GE Lighting Solutions and Toyoda Gosei.

Nichia, Samsung, and Osram held nearly 35 percent share in the global LED market revenue in 2013. Allied Market Research (AMR) is the market research and business-consulting wing of Allied Analytics LLP based in Portland, Oregon, USA.

# RFMD and TriQuint renamed Qorvo

RF MICRO DEVICES and TriQuint Semiconductor have revealed that their combined companies will be renamed Qorvo.

Pronounced kor-vo, the new name is said to convey the combined company's ability to deliver the core technologies and innovation that will enable customers to launch their next-generation designs even faster. "We believe that our new name reflects our company's commitment to keep customers at the centre of all that we do," said Bob Bruggeworth, RFMD president and CEO, who will serve as Qorvo's CEO following closing of the merger. "As a new leader in RF solutions, Qorvo will offer the agility, innovation and precision customers need for success in mobile, infrastructure, and defense markets "

"Our companies have been RF industry pioneers developing many of the core technologies our world now relies on," said TriQuint CEO Ralph Quinsey, who will serve as non-executive Chairman of Qorvo following closing of the merger. "Qorvo is building from our foundation of true innovation to solve our customers' most difficult challenges. We do this so that their customers, whether mobile consumers or troops on the move, will be able to connect with loved ones, protect our security, or voyage to new lands."

Shareholders of both TriQuint and RFMD voted to approve the merger on September 5th, 2014, and the transaction is expected to close in the second half of 2014, following other required regulatory approvals and satisfaction of customary closing conditions. Qorvo is expected to be traded on the NASDAQ Global Stock Market under the ticker symbol 'QRVO' after the merger.

# Optimize the Thermal Performance of your Process Equipment.

Extensive computational tools enable product designs to be highly refined for ultimate performance.

Multi-zone circuit layouts in a polyimide construction are highly customized to deliver exacting performance up to 250°C.

EZ-ZONE<sup>®</sup> RM Multiloop controllers are fully scalable with up to 152 PID Loops and 256 monitor points per system. W atlow provides innovative solutions to help process tool manufacturers meet the needs of the semiconductor technology roadmap. Our approach is to work collaboratively to help solve complex thermal challenges associated with state-of-theart manufacturing processes; helping to improve yield, throughput and cost of ownership. This includes innovative heaters, controllers and sensors for use in front-end and back-end applications such as CVD, PECVD, Etch, Diffusion, Bonding, IC test and more.

WATLO

ASSURANT<sup>™</sup> gas and pump line heaters feature high temperature capabilities with low outgassing.

# Contact Watlow<sup>®</sup> today for the latest thermal solutions for semiconductor applications.

| Europear | Technical Sales Offices               | Italy |

|----------|---------------------------------------|-------|

| Germany  | +49 (0) 7253-9400-0<br>info@watlow.de | Spain |

| France   | +33 1 41 32 79 70<br>info@watlow.fr   | UK    |

italyinfo@watlow.com +34 91 675 1292 info@watlow.es +44 (0) 115-964-0777

info@watlow.co.uk

+39 02 4588841

## NEWS REVIEW

# Emcore announces sale of space PV activities

EMCORE, a provider of compound semiconductor-based components, subsystems, and systems for the fibre optics and space solar power industries, has announced that it has entered into a definitive agreement with an affiliate of private equity firm Veritas Capital.

Under this agreement, the affiliate of Veritas has agreed to purchase Emcore's space photovoltaics business for \$150 million in cash. The transaction is subject to approval by Emcore's shareholders and other customary closing conditions and is currently expected to close in December 2014 or January 2015.

Emcore's Space Photovoltaics business was founded in 1998 and is based in Albuquerque, New Mexico. The business provides products for space power applications including highefficiency multi-junction solar cells, coverglass interconnected cells and complete satellite solar panels, along with terrestrial applications, including high-efficiency multi-junction solar cells for concentrating photovoltaic power systems.

"Veritas Capital is excited to be associated with Emcore's space photovoltaics business. The management and employees at Emcore have an established history of providing leading technology and reliable products to the worldwide satellite industry.

We look forward to continuing this excellent track record under our ownership and to working with the Space Photovoltaics team to expand the business," said Benjamin Polk, Partner of Veritas Capital.

"Veritas' proven track record of fostering growth in high-technology and defense industry companies makes it an excellent fit for Emcore's Space Photovoltaics business. Emcore's board ofdDirectors and management team believe this transaction will benefit our satellite customers while providing considerable value to our shareholders," said Hong Hou, president and CEO of Emcore Corporation.

# US scientists grow GaAs films on low cost substrates

III-V SEMICONDUCTORS such as GaAs make highly efficient solar cells but the GaAs or Ge substrates used for their epitaxial growth account for more than half of the cost, giving limited use in terrestrial photovoltaic applications.

While efforts have been made to grow high quality single-crystalline GaAs and III-V materials on low-cost substrates such as metal foils, they have not been very successful. Either the cost-reduction has been insufficient for making solar cells for terrestrial use or the optoelectronic properties have become degraded so the power conversion efficiency is low.

Now a research team from the University of Houston, South Dakota School of Mines and Technology, and NASA Johnson Space Center, has reported the heteroepitaxial growth of high mobility, single-crystalline-like *n* and *p-type* doped GaAs thin films on inexpensive, flexible metal foils using an MOCVD process. The GaAs films exhibited hole and electron mobilities as high as 66 and 300 cm<sup>2</sup>/V-s, respectively. The epitaxy enabling substrate for GaAs growth was single-crystalline-like Ge thin film on biaxially textured templates made by ion beam assisted deposition on metal foil.

According to the team, the GaAs films on metal foils showed single-crystalline-like nature, strong biaxial texture, low grain misorientation (less than 2°) and strong photoluminescence at room temperature. Precise control of doping and carrier concentration was achieved, resulting in GaAs films with high carrier mobility and electrical conductivity.

The researchers believe the work can pave the path for roll-to-roll manufacturing of flexible III-V solar cells for the mainstream photovoltaics market.

'High mobility single-crystalline-like GaAs thin films on inexpensive flexible metal substrates by metal-organic chemical vapor deposition' by P. Dutta et al, appeared in Appl. Phys. Lett. **105** 092104.

# Riber introduces compact new 3inch research MBE system

RIBER has launched a new 3inch substrate MBE research system, the Compact 21 Discover, which it presented at the 18th International Conference on Molecular Beam Epitaxy, held in Flagstaff, USA.

The new model is claimed to revolutionise research MBE by presenting the reactor on an open frame, enabling 360 degree access to the machine's components and incorporating the transfer rod, traditionally a fragile, long part of the system, into the electronics cabinet.

The company describes it as the most compact and ergonomic 3inch MBE system on the market.

Based on the recent Compact 21DZ, the Discover is also the only 3 inch MBE system on the market to combine 12 symmetric cell ports with a 10 inch central port, offering flexible performance.

Lower Cost LEDs

EPIK700

# Faster LED Adoption

# Another breakthrough from Veeco. This time it's EPIK.

Introducing Veeco's new TurboDisc<sup>®</sup> EPIK700<sup>™</sup> GaN MOCVD system

As global consumption for LED general lighting accelerates, manufacturers need bigger, better MOCVD technology solutions that increase productivity and lower manufacturing costs.

The EPIK700 MOCVD system combines Veeco's award-winning TurboDisc reactor design with improved wafer uniformity, increased productivity and reduced operations expenses to enable a cost per wafer savings of up to 20 percent compared to previous systems.

It also features a reactor with more than twice the capacity of previous generation reactors. This increased volume coupled with productivity advancements within the EPIK700 reactor, results in an unmatched 2.5x throughput advantage over previous reactors.

Learn how Veeco's TurboDisc EPIK700 GaN MOCVD system can improve your LED manufacturing process today.

The advantage is not just big. It's EPIK.

Contact us at www.veeco.com/EPIK700 to learn more.

Veeco's New TurboDisc EPIK700 GaN MOCVD System

### NEWS REVIEW

# Dow Corning sets new standard for 150 mm SiC wafer crystal quality

DOW CORNING, the supplier of silicon and wide-bandgap semiconductor technology, has announced that it now offers 150mm diameter SiC wafers under its Prime Grade portfolio.

Recently launched to set new standards for 100 mm SiC wafer quality, the portfolio also offers three tiers of manufacturing quality 150mm SiC substrates: Prime Standard, Prime Select and Prime Ultra. Each tier offers increasingly stringent tolerances on critical defect types that adversely impact device performance, such as micropipe density (MPD), threading screw dislocations (TSD) and basal plane dislocations (BPD).

"SiC wide-bandgap power semiconductors have rapidly evolved from a cutting-edge niche into an established technology sector that is increasingly focused on the manufacturing economies afforded by SiC crystal quality, wafer size and other critical factors," said Tang Yong Ang, vice president, Compound Semiconductor Solutions, Dow Corning.

"Dow Corning's decision to expand its Prime Grade portfolio to include 150mm diameter SiC wafers aims to meet this very competitive demand.

As we rapidly scale production of these high-quality wafers, our customers will be able to more confidently pinpoint the SiC substrate that optimizes the performance and cost of their nextgeneration device design while leveraging the improved economies of scale offered by larger wafer diameters."

While many SiC wafer manufacturers promise low micropipe densities for their 150mm substrates, Dow Corning is

among the first to specify low tolerances of other defect types, such as TSD and BPD. Such defects reduce device yields, and inhibit the cost efficient manufacture of large-area, next-generation power electronic devices with higher current ratings.

# Bendy LEDs and solar cells are one step closer

#### FLEXIBLE ELECTRONICS and

optoelectronics devices are usually made with organic materials. But inorganic compound semiconductors such as GaN would offer better optical, electrical and mechanical properties if it were possible to grow them on flexible substrates.

In a new open access journal APL Materials, a team of Seoul National University (SNU) researchers led by Gyu-Chul Yi describes their work growing GaN micro-rods on graphene to create transferrable LEDs and enable the fabrication of bendable and stretchable devices. The picture below shows the process.

"GaN microstructures and nanostructures are garnering attention within the research community as light-emitting devices because of their variable-colour light emission and highdensity integration properties," explained Yi.

"When combined with graphene substrates, these microstructures also show excellent tolerance for mechanical

deformation." Ultrathin graphene films consist of weakly bonded layers of hexagonally arranged carbon atoms held together by strong covalent bonds. This means graphene can provide the desired flexibility with mechanical strength. Also it's also chemically and physically stable at temperatures in excess of 1,000 °C.

To create the actual GaN microstructure LEDs on the graphene substrates, the team uses a catalyst-free MOCVD process they developed back in 2002. "Among the technique's key criteria, it's necessary to maintain high crystallinity, control over doping, formation of heterostructures and quantum structures, and vertically aligned growth onto underlying substrates," Yi says.

When the team put the bendability and reliability of GaN micro-rod LEDs fabricated on graphene to the test, they found that "the resulting flexible LEDs showed intense electroluminescence and were reliable - there was no significant degradation in optical performance after 1,000 bending cycles," noted Kunook Chung, the article's lead author and a graduate student in SNU's Physics Department.

"By taking advantage of larger-sized graphene films, hybrid heterostructures can be used to fabricate various electronics and optoelectronics devices such as flexible and wearable LED displays for commercial use," said Yi.

The article, 'Growth and characterizations of GaN micro-rods on graphene films for flexible light-emitting diodes' by Kunook Chung et al appeared today in the journal APL Materials.

# SEMICON® Europa2014

October 7–9 • Alpexpo • Grenoble, France

without limits.

or industry

- Semiconductor Manufacturing Equipment for Front-End and Back-End, Materials and Services

- Electronic Components and Design (new) IC, ASIC, MEMS, Sensors, Design, Foundries, Flexible Electronics

- Electronic Applications (*new*) Imaging, Energy Efficiency, Healthcare, Security

- Allée des Clusters (new)

- Innovation Village (new)

- Science Park

Register now online:

#### EPN5W

*Use promotion code and save 25 Euro! Free access to SEMICON Europa 2014. www.semiconeuropa.org*

# **PROGRAM TOPICS**

- Semiconductor Technology including Fab Management, Automation, 450mm, Lithography, Metrology, New Materials

- MEMS

- Advanced Packaging and Test

- Imaging Conference (new)

- Low Power Conference (new)

- Power Electronics Conference (new)

- Plastic Electronics

- Executive and Market Summit

- Silicon Innovation Forum (new)

- Industrial Sites visits (new)

Supported by:

## NEWS REVIEW

# Plessey adds in-house LED assembly line to UK facility

PLESSEY has added an LED assembly line to its expanding Plymouth UK facility. The company says the assembly line will enable it to focus on its high brightness LED growth plans based around its solid-state lighting and sensing business, taking new products from concept to production in less time whilst also functioning as an innovation centre for next generation LED packages.

The Plessey bespoke assembly line uses a laser saw process and finishes with an automatic test for industry standard PLCC (Plastic, Leadless Chip Carrier) packages.

The line includes die attach, wire bonding, phosphor mixing, encapsulation and singulation, in addition to all the other industry-standard, supporting equipment and processes. Designed specifically around speed and flexibility, the line will provide customers with engineering samples for evaluation and pilot builds ahead of full production. Mike Snaith, Plessey's operations director said: "The industrialisation of GaN-on-Silicon LED technology does not end at producing wafers - it also requires as much attention to the back-end processing to ensure that all the benefits we make at wafer level are fully realised in the final product. This is the best way to provide customers with the LED products they need."

Plessey's Plymouth facility is already demonstrating returns for this transition, enabling it to build working samples of complete in-house filament prototypes for the new market of LED filament replacement bulbs. The filament prototypes use a dedicated die and assembly, all of which is designed and manufactured within the facility.

Keith Strickland, Plessey's CTO, added: "The fact that we are recruiting recognised industry shapers from the world of solid-state lighting is a tangible endorsement that the Plessey value

proposition is both exciting and credible." The facility brings additional benefit with wafer sawing and going forward, new LED packaging standards will be established to match the benefits made at wafer level. Plessey's assembly line investment is the start of this cycle of innovation where a revision of the value chain for LEDs and solid-state lighting is taking place.

Plessey's MaGIC (Manufactured on GaNon-Si I/C) High Brightness LED (HBLED) technology has won awards for its innovation and ability to cut the cost of LED lighting by using standard silicon manufacturing techniques.

Plessey's range of products for lighting applications will be on show at LuxLive, ExCel London, 19-20 November.

# GaN to drive pulsed RF power chip market

MARKETS FOR PULSED RF power devices up to 18GHz are expected to show continued growth over the next five years despite the current economic turmoil and cuts in defense spending. While their association with consumer spending fuels the volatility of many global electronics markets, pulsed RF power devices are supported by quite different priorities. According to market analyst ABI Research, the pulsed RF power semiconductor device market will exceed \$300 million by 2019, with GaN driving growth.

"Many RF power semiconductor manufacturers are on a quest to find markets unrelated to mobile wireless infrastructure," notes ABI Research Director Lance Wilson. "Device prices in wireless infrastructure are falling, and the total available market is flattening out."

Some markets that use pulsed RF power devices, such as transportation safety and military, are experiencing solid growth even in the midst of today's

economic downturn. These devices are used in radars for military, weather and marine applications, and in the current worldwide upgrade of the air traffic control system. There is also a market segment devoted to the avionics transponder and air navigation market, which is also lifted by the overall air traffic control upgrade.

Intrinsically less "optional" than many consumer markets, these segments are therefore less sensitive to economic upheavals than consumer-driven markets, although they are not totally immune to the macro economy. Understanding this, many semiconductor manufacturers are attempting to enter this market space; however, some factors may complicate their efforts. Pulsed RF power device markets are becoming very competitive technologically: GaN and SiC devices are vying for market share along with the more established Si and GaAs based technologies.

However, the market may not be able to support all the new entrants. "Undoubtedly some consolidation will continue to occur. While not guaranteed success, those companies that have a track record working with government agencies and defense contractors are going to have an advantage over those that are new entrants," adds Wilson.

In the article "The maturing MOSFET" in the August&September 2014 edition of *Compound Semiconductor* the name of John Palmour, Cree's chief technology officer, was spelt incorrectly. We apologise for this error.

# IQE, Win and NTU to create compound semiconductor centre in Singapore

IQE has entered into a Memorandum Of Understanding (MOU) with Win Semiconductors and Nanyang Technological University (NTU) to participate in the formation of a centre of excellence for the development of compound semiconductor technology in Singapore.

The MOU anticipates the creation of a new entity called the Compound Semiconductor Development Centre (CSDC), which will be jointly owned by IQE, WIN, NTU, local management and key academics. The centre is expected to start operations next quarter.

The three partners believe that compound semiconductor technology will play a significant role in the future of the overall semiconductor industry, and that this initiative will provide a focal point for effective collaboration between industry and academia in developing next generation technologies.

It recognises the significant investment that is already been made globally into the many emerging markets for compound semiconductors, and its purpose is to accelerate the development of the technology in Singapore, and provide an effective incubator for bringing new innovations to market.

The Economic Development Board of

Singapore has played an important role in pulling this initiative together, which provides a good fit with other compound semiconductor development activities being undertaken in Singapore such as the SMART-LEES initiative. These initiatives are creating next generation IP in Singapore which will support continued economic growth and prosperity in Singapore.

This project forms part of IQE's global reorganisation plan. As part of its contribution to this joint venture, IQE will be providing facilities, equipment and IP on favourable terms to the CSDC. As a consequence, IQE is creating provisions of £4.2m for asset impairment comprising the transfer of tools to the CSDC and £7.7m for the lease of existing buildings and facilities.

Drew Nelson, chief executive of IQE, said: "IQE is proud to be a founding partner of the CSDC. It represents a very innovative approach to making the most of the skills and talent that exist in Singapore. We believe that this will provide an effective route to overcoming the barriers that prevent new ideas and innovations being successfully brought to market and advancing and commercialising new compound semiconductor technologies. This initiative is a strong fit with IQE's strategy for technology leadership."

Yoon Soon Fatt, NTU said: "We have built an exciting compound semiconductor capability within NTU. The CSDC provides a meaningful collaboration for us with two key industrials within the compound semiconductor industry. We are very pleased to be partnering with IQE and WIN. We look forward to the opportunities that this presents"

Terence Gan, director of electronics at the Singapore Economic Development Board said: "Singapore is committed to develop the compound semiconductor industry and welcomes the creation of CSDC. Compound semiconductors make energy efficient LED lighting and fibre optic communications possible, and will enable the creation of ultra-fast and ultra-energy efficient semiconductor integrated circuits. CSDC is an important partner to grow our pipeline of compound semiconductor R&D talent."

# Sofradir announces megapixel IR detector for space programs

SOFRADIR, the French developer of advanced IR detectors, has launched the Next Generation Panchromatic detector (NGP), a 1024 x 1024 visible to short wavelength infrared (SWIR) Focal Plane Assembly.

According to the company, NGP is the first European-made space-oriented megapixel array that space agencies

can consider for deep space science (planets and asteroids studies), Earth observation and Earth monitoring (meteorology, global warming studies, agriculture surveillance,...) applications. Sofradir developed the large format NGP, which is based on mercury cadmium telluride (HgCdTe) technology, as part of an R&D contract with the European Space Agency (ESA). NGP's

#### 8 benefits of sponsoring CS International 2015

- Senior management networking opportunities

- Increased company and brand awareness

- Access to the top strategists within the compound semiconductor industry

- Create, develop and support customer relationships

- Engage in debate, share insight and expertise on industry challenges

- Gain visibility and recognition as an industry leader

- Leverage exposure in multiple industry media

- Demonstrate market innovation and leadership by launching new services, products and systems

# www.cs-international.net

Call now +44 (0)24 76718970, email event@cs-international.net or view the online sponsorship pack at mediapack.cs-international.net

Connecting, informing and inspiring the compound semiconductor industry

1k x 1k format is four times larger than existing Sofradir SATURN starring array IR product currently deployed on observation satellites or spacecraft. The NGP detector has already been selected this year for the SENTINEL-5 mission planned for launch by 2021 on-board METOP-SG satellite in order to monitor the Earth atmosphere from a polar orbit.

"Sofradir is extremely proud to make the large format NGP 1024x1024 visible to SWIR detector available to our customers focusing on space applications," said Philippe Chorier, space department manager at Sofradir. NGP 1k2 attests to Sofradir's increasing technological leadership in producing reliable and high performance IR products for space applications. The product's ready-todeploy feature responds to demands to shorten space mission delivery times or to minimize the risks in delays. Based on its added performance and time saving benefits, we anticipate a lot of interest in NGP 1k2 in future space missions".

Infrared detectors from Sofradir are currently on-board Helios II (Earth observation) and Spirale (early warning system) military satellites, as well as the Venus Express scientific probe (SPICAV / SOIR instrument - Spectrometry for Investigation of Characteristics of the Atmosphere of Venus / Solar Occultation IR-).

Its IR products were also to be deployed in space instruments on Sentinel 2, part of the European GMES (Global Monitoring for Environment and Security) space initiative, on the TROPOMI/Sentinel 5 Precursor (part of the GMES), the hyperspectral Earth observation systems PRISMA (Italy) and HYSUI (Japan), as well as on scientific instruments such as Phobos Grunt and Nomad (ExoMars Trace Gas Orbiter). Other programs in progress include: MUSIS/CSO (successor of HELIOS II), MTG (Meteosat Third Generation, ESA), and SGLI (Second generation GLobal Imager) instrument onboard GCOM-C (Global Change Observing Mission -Climate), HAYABUSA2 (asteroid study) or CHANDRAYAAN-2 (lunar surface mapping).

# Solutions for COMPOUND SEMICONDUCTOR MANUFACTURING

Temporary Bonding and Debonding of Thinned and Fragile Compound Semiconductor Substrates

Spray Coating for Dielectrics, Thick and Thin Resist Layers and High Topography

Optical Lithography for Device Patterning and Advanced Packaging

Wafer Bonding for Layer Transfer and Advanced Packaging

## NEWS REVIEW

# Merck KGaA to acquire Sigma-Aldrich

MERCK KGaA and Sigma-Aldrich have entered into a definitive agreement under which Merck KGaA, Darmstadt, Germany, will acquire Sigma-Aldrich for \$17.0 billion (€13.1 billion), establishing one of the leading players in the \$130 billion global life science industry.

Merck KGaA, Darmstadt, Germany, will acquire all of the outstanding shares of Sigma-Aldrich for \$140 per share in cash. The agreed price represents a 37 percent premium to the latest closing price of \$102.37 on September 19, 2014, and a 36 percent premium to the one-month average closing price. The transaction is expected to be immediately accretive to Merck KGaA,

"This transaction marks a milestone on our transformation journey aimed at turning our three businesses into sustainable growth platforms", said Karl-Ludwig Kley, Chairman of Merck KGaA, Darmstadt, Germany's Executive Board. "For our life science business it's even more than that: it's a quantum leap.

"In one of the world's key industries two companies that fit perfectly together have found each other to present a much broader product offering to our global customers in research, pharma and biopharma manufacturing and diagnostic and testing labs. As such, the

combination of Merck KGaA, Darmstadt, Germany, and Sigma-Aldrich will secure stable growth and profitability in an industry that is driven by trends such as the globalization of research and manufacturing."

He added: "What's more, the combination gives us the possibility to invest even more in innovation going forward. We are delighted to make this compelling proposition to Sigma-Aldrich's shareholders, who will obtain full and certain cash value for their shares."

Rakesh Sachdev, president and CEO of Sigma-Aldrich, said, "We are excited to join forces with Merck KGaA, Darmstadt, Germany, a distinguished industry leader. This transaction is a clear validation of our success in transforming SigmaAldrich into a customer-focused and solutions-oriented global organization. This is a testament to the strength of the Sigma-Aldrich brand and the accomplishments of our 9,000 employees worldwide.

"We believe this is a very positive outcome for our shareholders, who will receive a significant premium, and our employees, who will benefit from enhanced opportunities as part of a larger, more global organisation."

In the Laboratory & Academia business, together EMD Millipore and Sigma-Aldrich will offer their customers a complementary range of products across laboratory chemicals, biologics and reagents. In pharma and biopharma production, Sigma- Aldrich will complement EMD Millipore's existing products and capabilities with additions along the entire value chain of drug production and validation.

Shaped over almost 350 years by a family of owners, Merck believes that the combination will afford new opportunities to employees at both companies. It plans to maintain a significant presence in St. Louis, and in Billerica, following completion of the transaction, as well as in important EMD Millipore sites such as Darmstadt and Molsheim, France.

# Veeco's ion beam technology reaches milestone

VEECO INSTRUMENTS has announced that its new OdysseyIon Beam Deposition(IBD) Upgrade for the NEXUS IBD-LDDSystem has repeatedly produced photomask blanks with zero deposition defects larger than 70 nm. This represents a significant milestone toward the manufacture of semiconductor devices with advanced extreme ultraviolet (EUV) lithography, according to the company.

EUV mask blank defects are, as a practical matter, impossible to repair and can render a semiconductor device useless. Because of this, mask blank defects have been a key obstacle toward high volume manufacturing.

"EUV lithography brings chipmakers the ability to manufacture higher performing

devices at lower cost compared to manufacturing methods which rely on multiple patterning steps," said Ron Kool, senior VP of EUV product and service marketing at ASML, the Netherlandsbased lithography systems company. "As ASML is making steady progress preparing the scanner and light source for industrial high volume manufacturing, the readiness of the EUV industry, including mask blanks, is critically important to our customers. Veeco's dedication to the Odyssey upgrade program, done in coordination with customers, consortia, and other industry stakeholders, is a model for EUV infrastructure advancements."

Veeco IBD technology leads the industry in high film quality, featuring extremely low particulate deposition and precise control of optical properties for single or multi-layer processes. These technology features are required for defect-free, high volume EUV manufacturing. Currently, all of the leading EUV mask blank manufacturers use the Veeco NEXUS IBD-LDD system.

"Veeco is committed to working with our customers and industry partners to advance the EUV roadmap and increase the output of defect-free mask blanks," said Jim Northup, Senior Vice President and General Manager of Veeco Advanced Deposition & Etch. "We have made significant investments in the Odyssey upgrade and consolidated our optical coating and ion beam resources in a single R&D site to ensure ongoing development of our industry-leading IBD technology."

# your EPITAXIAL GROWTH partner

InGa

# Enabling advanced technologies

nA Gal

World leading technology

nGaP

Gaas

- Complete materials range

- ⊖MOCVD, MBE, CVD

- Advanced semiconductor wafer products

- Advanced R&D capabilities

- Multiple, manufacturing sites (Europe, Asia, USA)

www.iqep.com

# Electric vehicles: SiC and beyond

As recent forecasts from Lux Research predict SiC devices will crack auto-markets by 2020, have GaN-on-silicon alternatives stalled? Rebecca Pool investigates

WITH THE MARKET FOR DISCRETE POWER electronics components set to reach some \$15 billion by 2020, manufacturers are racing to deliver SiC and GaN-on-silicon devices with higher current densities and better thermal management than the silicon incumbent. Industrial, electronics and renewables generation applications all demand these smaller, more efficient wide bandgap devices, but right now, by far the most promising market for power electronics makers is electric vehicles.

As Lux Research analyst, Pallavi Madakasira, highlights, efficient power electronics is crucial to reducing battery sizes in electric vehicles, which has massive knock-on benefits for the rest of the automotive system including wiring, packaging and weight.

"Once you start achieving the efficiency savings, you can get away with having a smaller lithium ion battery, and then you only require, for example, a smaller heat sink, so you cut costs and save space and weight," she says. "[Efficiency savings] have a cascading effect across the entire system that really do add up."

In her latest research, Madakasira forecasts SiC device manufacturers, such as Infineon, Cree and ST Microelectronics, will cash in on the automarket's growing performance needs before GaN contemporaries, with SiC diodes displacing silicon devices as early as 2020. "Silicon carbide has a significant lead in the industry primarily due to the sheer number of developers that have invested in the technology," she says. "Big volume manufacturers, such as Infineon and ST churn out several hundreds of thousands if not millions of diodes."

In contrast, Madakasira reckons only around two GaN-on-silicon manufacturers are offering products at lower voltage applications. And as she adds: "We know that the GaN developers are not planning to target the automotive industry anytime in the near future, at least not in the next three to five years."

Instead, these GaN players are already making in-roads to renewable generation and grid storage markets. "Certification [in automotive markets] takes time and GaN players cannot generate revenue overnight here," says Madakasira, "We will see the first GaN solar inverter from Transphorm hitting the market come 2015. The technology must make its mark and establish credibility here before transitioning to what might seem like a more daunting automotive market."

In the meantime, SiC devices looks set to reach plug-in hybrid electric vehicles first, where power savings equate to greater reductions in overall vehicle cost. As Madakasira points out, electric vehicles such as the Nissan Leaf probably won't contain a SiC device, as the battery is already small and a more exotic diode or transistor is simply too expensive for this low-end model.

"The cost savings must offset the pricier SiC device," she explains. "This cannot happen in the Nissan but we do expect plug-in vehicles to be the sweet-spot

for these types of solutions." But it is only a matter of time before GaN-onsilicon devices reach electric automotive markets. Madakasira reckons the technology will probably catch up within the decade, with products being released come 2023, once devices have been tried and tested in other applications.

"It's a common misconception that SiC is the only technology that is ideal for automotives. Yes, SiC can operate at the high temperatures but not every function within the vehicle requires [this]; so for GaN, it's a question of when, not if," she says. "Then we also expect to see hybrid systems, either a combination of silicon, SiC and GaN, or simply a combination of GaN and SiC."

Cost shouldn't pose a major issue for later GaN-on-silicon entrants. While the cost of growing complex buffer layers on silicon substrates negates some of the obvious cost benefits using these large diameter wafers, devices will still be cheaper than SiC products. "GaNon-silicon device prices will never be as cheap as [pure] silicon alternatives but they will likely be cheaper than SiC devices where substrate costs have always been high," explains Madakasira.

And the analyst reckons future prospects may still exist for GaN-on-SiC devices, at the high voltage applications currently reserved for SiC devices. "It's a given that SiC can do really well at high voltages [900 V and beyond], but can GaN-on-SiC do that too?" she asks.

"Companies claim to have the knowhow, still there is not any business commercialising these products right now, so it remains to be seen."

# BluGlass rises to NOCVD challenge

From LEDs to power electronics, BluGlass's low temperature plasma-based CVD process is set to ease GaN-on-silicon fabrication and offer a cool alternative to MOCVD. Rebecca Pool reports

FOLLOWING LAST YEAR'S hefty injection of Aus\$3 million (£1.67 million) in federal funds to demonstrate high efficiency, cheap GaN LEDs, Australiabased semiconductor process developer, BluGlass, is now revealing results.

In July, this year, the company claimed its

best ever light output from a *p*-GaN layer, grown via its low temperature remote plasma CVD process (RPCVD), onto a MOCVD partial LED structure. And in early August, the company unveiled a scaled-up version of its RPCVD system that's set to accelerate the development of brighter LEDs.

The company has spent nearly a decade developing its low temperature process to grow GaN, and more recently, *p*-GaN layers on MOCVD structures. To achieve low temperature growth, the company replaces the ammonia source of an existing MOCVD system with nitrogen gas, passed through an electrical coil to

generate a plasma. Directly supplying nitrogen via a plasma allows the company to deposit layers at relatively low temperatures. Actual figures remain elusive, but BluGlass's aim is to match the temperatures used to grow MOCVD multi-quantum wells.

While the company has worked with Emcore/Veeco systems in the past, this time round it has retrofitted a larger Thomas Swan/ Aixtron system. As Bluglass chief technology officer, Ian Mann, says: "We haven't been trying to build our own system from the ground-up but, more simply, have been retrofitting the most common systems out there."

"This latest reactor is well known, is economical to run, and will be capable of generating a single 8 inch wafer," he adds.

To date, BluGlass has been primarily working with two inch sapphire and silicon substrates, but Mann and colleagues hope the new system will help to prove RPCVD at larger wafer sizes. "The reality is, for silicon, 2-inch substrates aren't relevant in the market and most people are going to silicon at larger scales," he says. "Thanks to our lower temperatures, we aim to have better control over cracking and bow in these larger wafers and we've had considerable interest in how this system is going to perform at these wafer sizes."

Mann also hopes the latest retrofit system will tackle the crucial issue of scaling. As he highlights, he and colleagues are always asked whether or not their plasma-based CVD development-sized systems can reliably scale to production processes.

"This system is our answer to that question," he says. "We aim to convince customers that we have taken what we've been doing on the smaller system and repeated this here, while at the same time improving performance."

And as Mann asserts, that the latest Aixtron system isn't a world away from the full-scale systems populating today's production floors." The technology isn't dramatically different; the main difference is that production systems today are larger" he says. "So we feel quite comfortable that our latest system isn't far away from the final platform we are trying to develop."

With the second larger system installed, the BluGlass team is ready to scale up its RPCVD process for LED and power electronics markets [BluGlass].

Research to date has been primarily focused on depositing the RPCVD *p*-GaN layer onto the MOCVD-grown multi-quantum well layers. As Mann explains, the growth initiation of this layer and subsequent growth had proven a real challenge, so he and colleagues developed their existing reactor to operate with a higher density nitrogen plasma.

"This enhanced plasma system has formed a core part of our intellectual property and has proven critical to good growth," he says. "The way the MOCVD ends becomes the beginning of RPCVD growth, so we've made some subtle but simple changes to the final MOCVD [processes], which has helped ultimate device performance."

And with the growth of RPCVD layers on MOCVD templates in place, researchers are keen to use RPCVD to grow full structures, in much the same way as MOCVD is used to grow entire structures. This second larger system can only help.

"We've been very interested in trying to grow multi-quantum wells and p-GaN layers together in the same chamber," says Mann. "We've been very active on our p-GaN research, but with the larger system up and running, we can afford to push our research programmes in different directions, and this is something we are keen to put to the test."

#### Sapphire and silicon

But it's not all about silicon. As Mann emphasises, BluGlass's technology is intended to be 'substrate-agnostic' and right now, the bulk of the LED market is still fabricating structures on sapphire. Indeed manufacturers have been keen to find out exactly what the company's low temperature RPCVD process can do for multi-quantum well growth.

"With the low temperatures, you can incorporate more indium into the multiquantum wells, which lets you fabricate LEDs emitting at longer green and yellow wavelengths," he says. "Developing quantum well technology has always been on the cards, and is funded by company's federal Grant. Our second system provides more opportunity to explore such avenues."

Crucially, BluGlass also intends to take its low temperature growth process to power electronics markets. As Mann highlights, almost all HEMT structures are grown on silicon, so manufacturers are grappling with many of the same issues as LED players, a fact he and colleagues hope to exploit.

"There is still this cracking and bowing of large wafers, due to lattice and thermal mismatches between silicon and GaN," he says. "So a low temperature GaN on silicon platform could help power electronics manufacturers as well as LED [suppliers]."

And of course BluGlass's latest system – with its 8 inch wafer capacity – opens more doors to these markets. "Both GaN-on-silicon markets are looking towards larger substrates, LED [players] are looking at eight inch sizes and power electronics developers are looking at six inch substrates," says Mann. "These people are expected to move to eight inches in the future."

# Infineon and International Rectifier: WHAT NEXT?

What does Infineon's latest acquisition mean for industry? Rebecca Pool talks to the company to find out its plans

AS THE NEWS SINKS IN that Infineon is to buy International Rectifier, many in the industry are wondering what next?

In its biggest acquisition yet, Germany's largest chipmaker stumped up \$3 billion in cash for IR, bolstering its international presence in the US and Asia, and gaining one of the largest manufacturers of power management chips in the world. The move complement's Infineon's range of high voltage MOSFETs – the biggest chunk of IR revenue came from its low voltage MOSFETs – and also delivers low power IGBTs to its 1000 W to 2000 W range of the same devices. And while Infineon is still reaping the rewards of buying digital power management IC maker Primarion in 2008, IR provides power devices for new markets including

notebooks and game consoles.

Still, the best may be yet to come. Infineon has been manufacturing SiC diodes since 2001, and introduced its first SiC transistor – the 'CoolSiC 1200 V JFET – last year, which combined with MOSFET and driver IC gives a direct drive device for solar, UPS and industrial drives applications.

But while this has meant the business has had high voltage markets stitched up, the lower voltage end of the market has presented a problem. Not any more; enter IR with its GaN-on-silicon HEMTs for applications of 600 V and less.

"We started GaN research and development, but we haven't had a product on the market yet," says Tillmann Geneuss, manager of communications at Infineon. "It's no secret that, for GaN, companies such as International Rectifier and Transphorm are leading the competition."

Clearly, acquiring IR changes this. As Geneuss points out: "GaN has been a huge effort for IR, and it has generated a lot of intellectual property on the GaN-onsilicon epitaxy process."

And crucially the company has myriad very solid epitaxy-related patents for

depositing the buffer and GaN layers onto the silicon substrate. "There is sapphire, SiC and even bulk GaN, but silicon is the cheapest carrier solution," says Geneuss. "And that's why we think this has been a very valuable effort, because when it comes to the long-term and mass production, you have to look for the most cost-effective way to implement this."

Still Infineon isn't expecting instant gratification from IR's precious GaNon-silicon technology. According to Geneuss, the market is in its infancy and GaN revenues have been very small for IR and other players such as Transphorm.

"We already are seeing first revenues but expect it will take five years or more before we see really significant revenues," he says.

In the interim the company is firmly focusing on developing 'the best

solution' that will include IR's GaNon-silicon devices and Infineon's SiC products. "Customers require solutions, not individual products, and these new materials will not survive as standalone products," he says. "So we want to include the new technology with, say, our best IGBT, MOSFET or diode, in the best package to offer the best solution in terms of cost-performance-ratio and power density."

So where does Infineon's plans leave other GaN-on-silicon companies? Japan multinational, Panasonic, holds a hefty chunk of the market's GaN-on-silicon IP and is sampling 600 V GaN-on-silicon transistors. But what about the key, but much smaller players, such as Canadabased GaN Systems, EpiGaN, Belgium, Japan-based Transphorm and US-based EPC?

Media reports are already hinting at more acquisitions to come. And as

senior analyst from Yole Développement, Philippe Roussel, told *Compound Semiconductor:* "We anticipate more consolidations in the GaN area over the next two years and have several indications to who might be the next ones, but cannot disclose."

And if the GaN-on-silicon market develops slowly, the industry's startups could falter. Just less than two years ago, US-based SiC device manufacturer, SemiSouth, closed down. Despite investment from Silicon Valley manufacturer of devices for high voltage power conversion systems, Power Integrations, the up and coming business clearly couldn't generate cash flow in a rising market. Could the same happen to pure GaN players?

As Geneuss concludes: "Introducing components on these emerging wide band-gap materials is a marathon, not a sprint."

# CS International 2015 will provide timely, comprehensive coverage of every important sector within the compound semiconductor industry.

The 5th CS International conference will be held at the Sheraton Frankfurt Airport Hotel, in Germany on Wednesday 11th & Thursday 12th March 2015. The conference will build on the success of its predecessors, with industry-leading insiders delivering more than 30 presentations spanning six sectors.

Please visit **www.cs-international.net** for further information on this event.

# Book your place NOW

Please visit www.cs-international.net/register.php to secure your place

# TWO DAYS, SIX THEMES, OVER 30 INSPIRING PRESENTATIONS

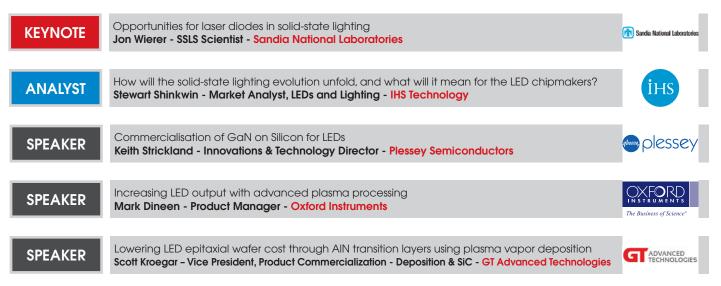

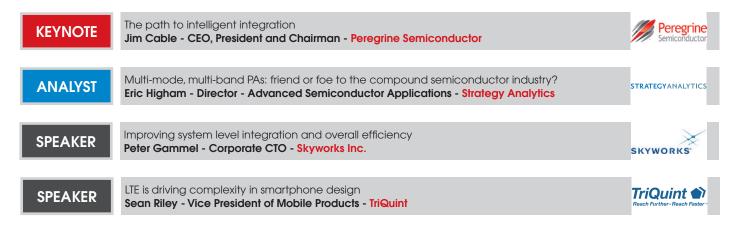

Six key themes lie at the heart of CS International 2015: solid-state lighting, power electronics, front-end mobiles, optoelectronics, III-V CMOS and RF electronics. Within each topic there is a key-note presentation from one of the most influential companies within this sector; one talk by a leading market analyst who will discuss trends within the industry and presentations by the leaders of firms developing cutting-edge technology in this field.

Connecting, informing and inspiring the compound semiconductor industry

All speakers and presentations are subject to change.

A selection of the 30+ presentations over two days covering six themes

#### **SOLID-STATE LIGHTING**

Soaring sales of LED bulbs are creating a great opportunity for chipmakers. But what do companies need to do to stand out from the crowd and win substantial orders while maintaining healthy margins?

#### **III-V CMOS**

By the end of this decade, it is said that silicon CMOS will have run out of steam. But what role will III-Vs have to play in the microprocessors of the future?

| KEYNOTE | Heterogeneous integration of III-V's and CMOS<br>Daniel Green - Program Manager - DARPA                                                                                  | DARPA           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| ANALYST | When will III-Vs make an impact in the silicon foundries? And will it last for long?<br>Mike Corbett - Managing Partner - Linx Consulting                                | LINX-Consulting |

| SPEAKER | III-V FETs for future logic applications<br>Jesus A del Alamo - Director of the Microsystems Technology Laboratories - MIT                                               |                 |

| SPEAKER | Opportunities and challenges of III-Vs in Si-based nanoelectronics industry<br>Matthias Passlack - Deputy Director - Taiwan Semiconductor Manufacturing Company (TSMC)   | tsme            |

| SPEAKER | Advanced in-situ metrology for III-V on silicon technology<br>Kolja Haberland - Chief Technology Officer - LayTec                                                        |                 |

| SPEAKER | Optimization of III-V R&D and manufacturing using advanced analytical methods<br>Temel Buyuklimani - Senior Director - Quadrupole SIMS Services - Evans Analytical Group |                 |

#### **POWER ELECTRONICS**

From a performance perspective, GaN and SiC are superior to silicon But high prices are holding them back from displacing the incumbent. How can this be addressed?

| KEYNOTE | Ditching the package to drive down GaN transistor costs<br>Alex Lidow - CEO and Co-founder - Efficient Power Conversion (EPC)                                         |               |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| ANALYST | When can WBG power electronics truly take off? Remaining technical and economic barriers to overcome<br>Philippe Roussel - Business Unit Manager - Yole Développement | Développement |

| SPEAKER | SiC technology in power electronics – a step change in value<br>Markus Behet - Global Market Segment Manager - Dow Corning Corporation                                | DOW CORNING   |

| SPEAKER | High performance GaN-on-Si power epiwafers employing rare earth oxide buffer layers<br>David Williams - VP of Business Development - Translucent                      | Translucent   |

| SPEAKER | Presentation TBC<br>Chris Horton - Director, Global Sales & Marketing - Cree Materials Business                                                                       | CREE          |

| SPEAKER | Presentation TBC<br>TBC - KLA-Tencor                                                                                                                                  | KIA Tencor    |

| SPEAKER | Developments in PVD technology for power electronics enabling roadmaps in compound semiconductor devices<br>Reinhard Benz - VP Sales and Marketing - Evatec           |               |

#### **FRONT-END MOBILES**

What's the biggest threat to revenues for GaAs power amplifiers? Is it the emergence of multi-band, multi-mode PAs built with this material, or the emergence of CMOS solutions?

Connecting, informing and inspiring the compound semiconductor industry

#### **OPTOELECTRONICS**

Does the growth of the datacom market signal a long-awaited return to better times for the makers of optical components? Is the CPV industry finally starting to gain a foothold in the solar industry?

| KEYNOTE | Presentation TBC<br>TBC - SOITEC                                                                                                                       | G Soitec |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| ANALYST | Where the CPV industry is heading, and what it needs to do to increase its market share?<br>Karl Melkonyan - Analyst - Solar Research - IHS Technology | İHS      |

| SPEAKER | Mid infrared light emitting diodes enable portable, battery powered gas sensing <b>Des Gibson - CEO - Gas Sensing Solution</b>                         |          |

| SPEAKER | Presentation TBC<br>The' Linh Nguyen, Senior Manager IC Development- Finisar                                                                           | Finisar  |

#### **RF-ELECTRONICS**

The potential of GaN in the RF arena has never been in doubt. But does it now satisfy all the requirements for deployment in the most taxing situations?

### A SELECTION OF THE COMPANIES ALSO PRESENTING INCLUDE:

Epigan **nano**metrics

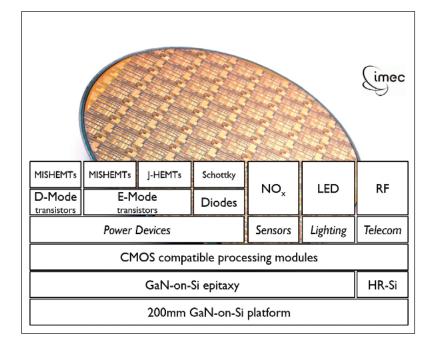

# Perfecting GaN-on-silicon **power electronics**

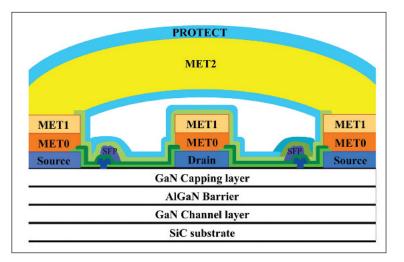

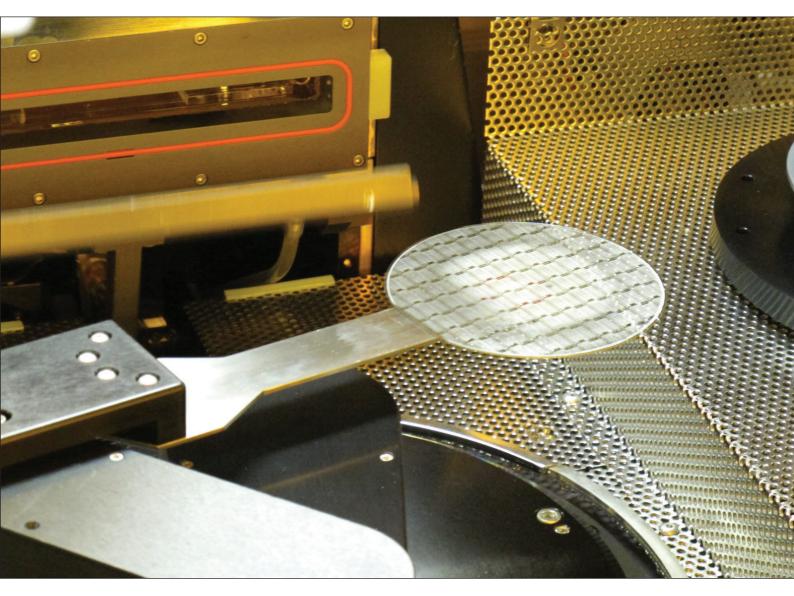

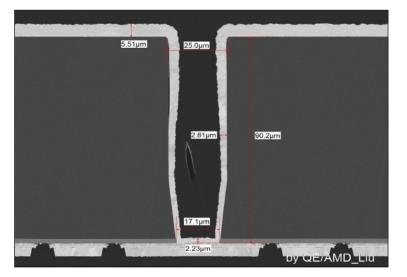

Inserting rare earth oxides increases material quality, trims wafer bow and boosts transistor performance BY DAVID WILLIAMS, ANDREW CLARK, F. ERDEM ARKUN AND RYTIS DARGIS FROM TRANSLUCENT

WITH ELECTRICITY NOW accounting for a staggering 43 percent of primary energy consumption, according to the International Energy Agency, the benefits of efficient energy conversion – from both an environmental and an economic perspective – are bigger than ever. And this pay-off is only going to grow as more electrical systems are manufactured for deployment in electric vehicles, computer power supplies, solar cell inverters and power converters for LED lighting.

One area where the use of electrical systems will grow fastest is in electrical vehicles. Speaking on behalf of Ford at CS International 2014, Power Semiconductor Research Engineer Ming Su revealed that 25 percent of the company's vehicles are expected to be electrified by 2020. Making the electrical conversion in these vehicles as efficient as possible will be high on the priority list of engineers based in the US, because this will help automobiles to satisfy a government mandate for 2025 that demands a fuel efficiency of at least 54.5 miles per gallon.

Thanks to its low cost, widespread availability and familiarity, silicon has been the semiconductor of choice for many years in electrical systems, where it is used to perform various roles, including voltage conversion. However, judged purely in terms of performance, this incumbent is inferior to wide bandgap semiconductors, such as SiC and GaN. Switch from silicon to GaN and it is possible to construct devices that combine a low on-resistance with a low parasitic capacitance, culminating in low power losses when the device is on and when it is switching between states.

These great attributes, which stem from the use of a high-mobility twodimensional electron gas at the interface between the GaN and AlGaN layers of a HEMT, make this class of transistor a promising device for incorporation into switched-mode power supplies serving many of the applications outlined above. According to the GaN power semiconductor manufacturer EPC of El Segundo, CA, 600 V devices account for a quarter of the overall power transistor market, with devices rated at 200 V or below pulling in three-quarters. Since GaN HEMTs are capable of covering all these voltages, there is good reason to believe that this wide bandgap semiconductor can be adopted in a broad range of power conversion applications.

#### Foundations for GaN

Ideally, manufacture of GaN HEMTs would involve growth on a native substrate. However, GaN substrates are prohibitively expensive and limited in size and availability, so different foundations must be used. The most common alternative, silicon, enables the fabrication of GaN HEMTs that are competitively priced compared to the incumbent. However, the penalty to pay for growth on silicon is that the production of these devices is far from easy. Engineers don't just have to contend with bow of the epiwafers, caused by differences in lattice constants and thermal expansion coefficients there are also challenges related to unwanted chemical reactions at the silicon surface.

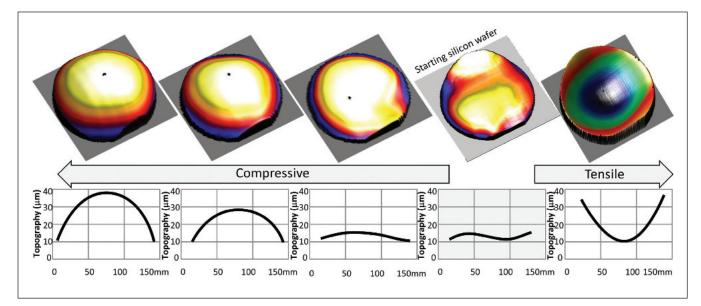

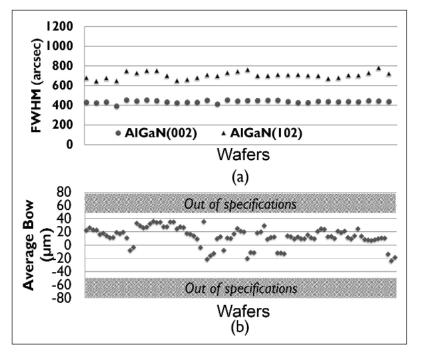

Figure 1. It is possible to control the bow using REO layers. The plot second from the right is a silicon wafer prior to any depositions. Bow measurements are taken using an FRT MicroProf 3D optical profilometer

One unwanted reaction is that of silicon with ammonia to create SiN. This resulting nitride can grow in an amorphous manner, destroying the crystal registration and with it the quality of the overlying GaN. Turning to a gallium wetting-layer is not a viable solution, because silicon is soluble in liquid gallium, so defects arise from the meltback of gallium. This doesn't occur with aluminium, the only alternative wetting material, but in this case the growth conditions have to be carefully controlled to minimise eutectic-driven diffusion of silicon into the upper GaN layers. And if there are any imperfections in the quality of AIN, such as pinholes, GaN can make contact with silicon, leading to meltback defects or silicon diffusion into GaN.

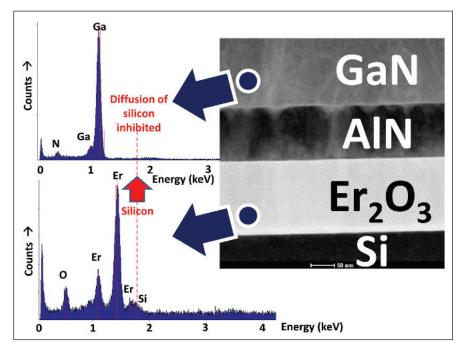

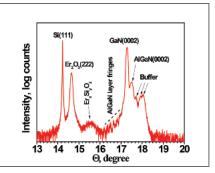

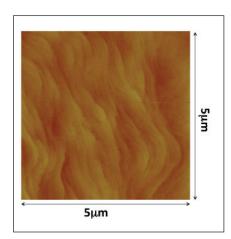

To avoid all of these issues, our team at Translucent of Palo Alto, CA, has

pioneered the development of an engineered buffer that aids the transition between silicon and GaN, and returns full design freedom to MOCVD process engineers. Our buffer is an insulating, single-crystal rare-earth-oxide (REO), with a composition carefully chosen to be lattice-matched to the silicon on its lower surface. Meanwhile, an upper surface is engineered so that defect growth is quite dissimilar to that associated with GaN on silicon – and more like that of GaN on sapphire – thanks to the GaN lattice being more closely matched to its foundation.

Benefits of the REO are not limited to lattice matching: this layer is also chemically inert, so it provides a physical barrier to silicon diffusion. Consequently, it is not possible for gallium to come into contact with silicon. What's more, epistructures grown with our engineered

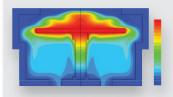

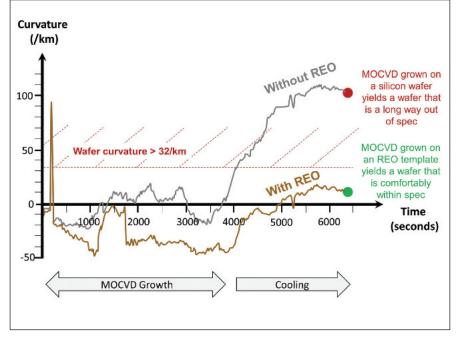

Figure 2. MOCVD bow during growth. This trace shows the curvature of two wafers on the same platen in a run. One was a bare silicon wafer and the other an REO template. In-situ monitoring of the entire process is via a LayTec EpiTT system that records the true wafer temperature, curvature, and reflectivity signals at 450 nm and 633 nm. These tools monitor the evolution of the GaN surface and the quality of the bulk GaN growth throughout the growth process. The start of the MOCVD run is at time = 0, and growth occurs up to 3800 s at which point the wafer begins to cool and tensile bowing starts. When unloaded after 6400 s, the two-dimensional electron gas on the silicon wafer has a curvature of 106/km, where as that grown on the REO template has a curvature of only 11/km. A curvature of 106/km corresponds to a bow of 133  $\mu$ m, which is out of spec, where as a curvature of 11/km corresponds to a bow of only 14  $\mu$ m, which is comfortably within spec for this sized wafer.

substrates can maintain a high degree of lattice registration, because the REO is lattice-matched to the silicon substrate. Note that the top interface between GaN and the REO is chosen to have a small mismatch, because this softens the interface and provides a degree of compliance.

#### Benefits of the oxide

Turning to an REO offers a new route to the production of epiwafers with a very low bow, which is a pre-requisite for processing in silicon lines. We can manage bow by pre-straining the wafer. Prior to MOCVD deposition of GaN, we make the wafer dome shaped. Without this, the MOCVD process would naturally result in wafers that are bowl-shaped – but thanks to the pre-straining, we are left with epiwafers that are very flat (see Figure 1, which shows a selection of wafers that have been measured, post REO growth, using a three-dimensional optical profilometer).

By adopting this approach, GaN epiwafers with an REO layer can be flat enough to be compatible with steppers used in microlithography. The requirements originate from the depth of field of the optical system in the stepper, and are defined in terms of maximum bow by SEMI. Wafers with a diameter of 100 mm, must have a bow below 40  $\mu$ m, while those that are 150 mm and 200 mm across must have bows of less than 60  $\mu$ m and 65  $\mu$ m, respectively.

Improvements in device performance also result from inclusion of an REO. This oxide is an insulator, so it increases the transistor's breakdown voltage. In addition, a common failure mechanism is addressed: devices often breakdown due to silicon diffusion, but this can't happen when an REO is involved, because this oxide provides an impenetrable barrier to silicon atoms.

To mitigate this diffusion process when producing conventional devices, thicker GaN layers are required. This adds to production costs, and must be weighed against the expense associated with deposition of a REO layer. Note that the insulating nature of this oxide means that it also reduces the thickness of GaN required to hit a particular blocking voltage. We anticipate that by preventing diffusion and aiding device robustness to high voltages, we may be able to trim the GaN thickness by at least 25 percent and also potentially remove all of the interlayers. These actions could result in a significant cost saving associated with device production.

A further benefit of our technology is that it is considerably different from other techniques for forming GaN-onsilicon, giving it an enviable position in terms of intellectual property. IP ownership is increasingly viewed as an important asset as the industry matures: Indeed the French market analyst, Yole Développement, recently produced a market report dedicated exclusively to GaN-on-silicon IP, underlining the importance of proper IP protection.

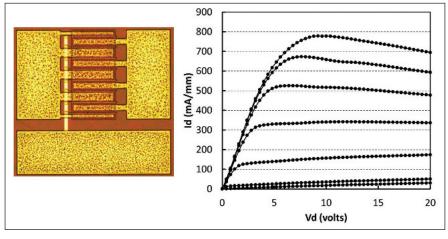

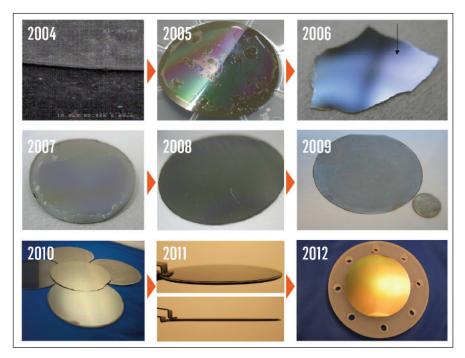

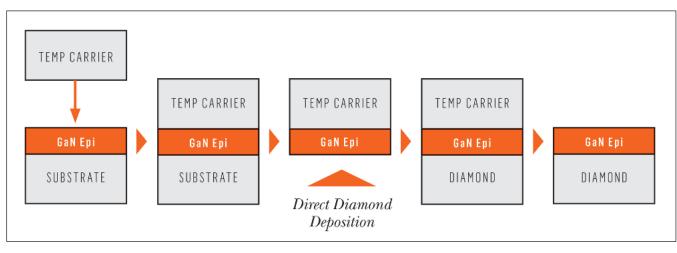

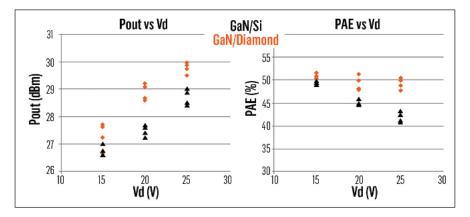

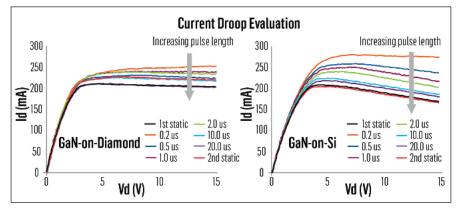

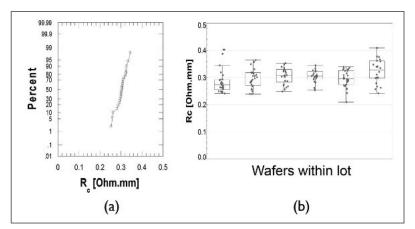

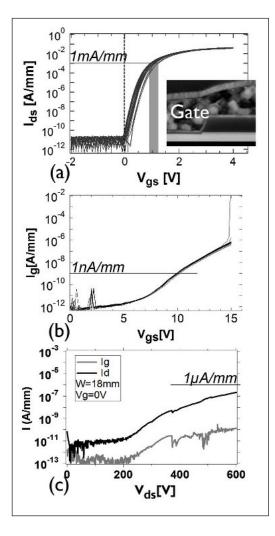

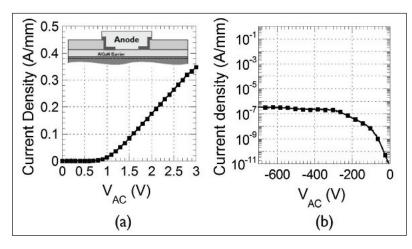

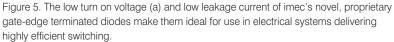

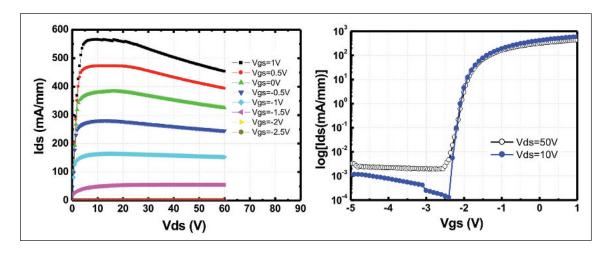

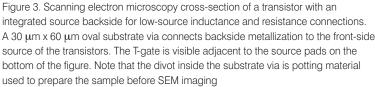

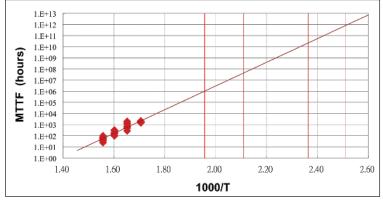

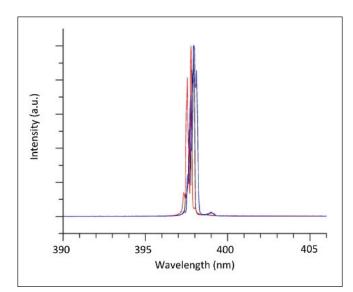

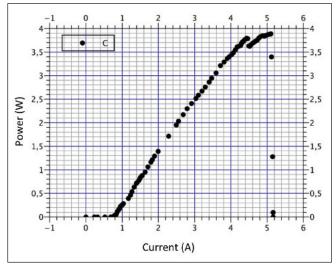

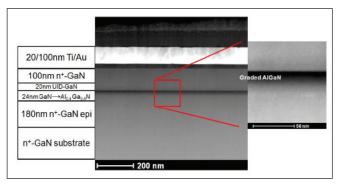

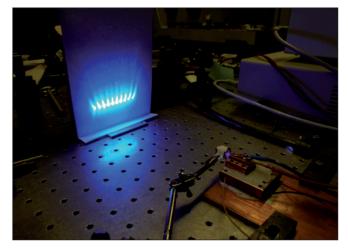

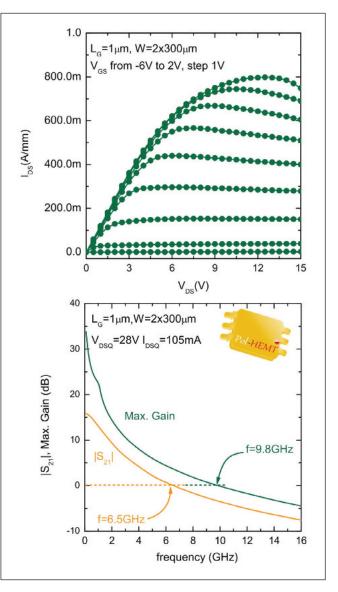

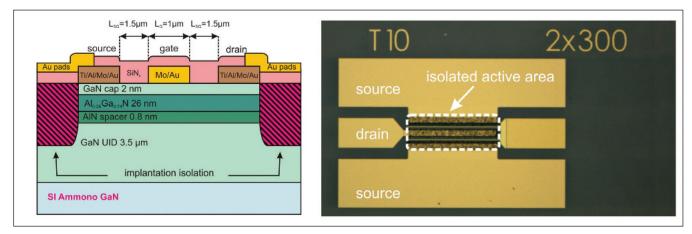

#### **Promising results**