# COMPOUND SEMICONDUCTOR

Connecting the Compound Semiconductor Community

Volume 21 Issue 1 2015

www.compoundsemiconductor.net

3C SiC promises cheaper MOSFETs

Handling heat with SiC circuits

IEDM: what future for the III-V FET?

YOU THINK,

# AIXTRON SYSTEMS SHOULD OFFER YOU THE BEST COST OF OWNERSHIP.

WE THINK THAT TOO.

THE NEW AIX R6.

#### DISCOVER THE NEW AIX R6.

Revolutionizing an industry is not about changing everything. It's about making the good even better. Introducing: The new AIX R6. It has everything you expect from the industry's technology leader plus better usability, better throughput and better cost of ownership.

AIXTRON SE  $\cdot$  info@aixtron.com  $\cdot$  www.aixtron.com

# editorialview

by Dr Richard Stevenson, Editor

### Silicon CMOS: Will III-Vs have a role to play?

WHEN AN ESTABLISHED, important technology runs out of steam, a quest begins for a modification that will inject a new lease of life. Potential refinements can initially generate a great deal of excitement, before greater scrutiny follows that exposes weaknesses associated with the successor.

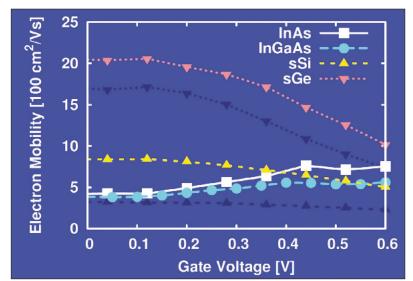

This scenario is playing out today in the world of silicon CMOS. Mobility in the silicon channel could hold back the performance of next-generation ICs, with the combination of InGaAs nFETs and germanium pFETs touted as a promising way forward.

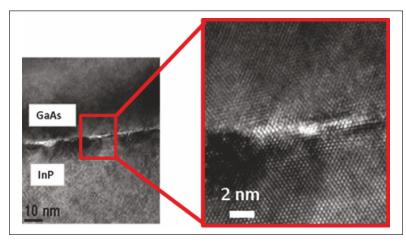

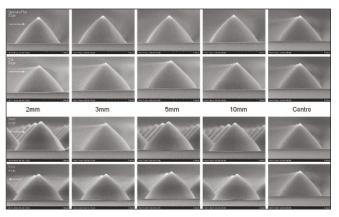

Within this magazine, we have highlighted many successes that will help to unlock the door to the production of nanoscale InGaAs FETs on silicon substrates. These triumphs include the realisation of high-quality III-V material on a silicon substrate, through approaches such as that pioneered by imec: Researchers at this insititute have learnt how to grow compound semiconductors in tiny V-shaped silicon trenches.

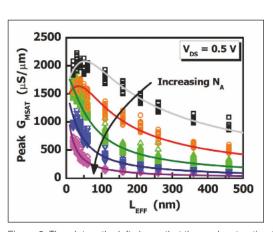

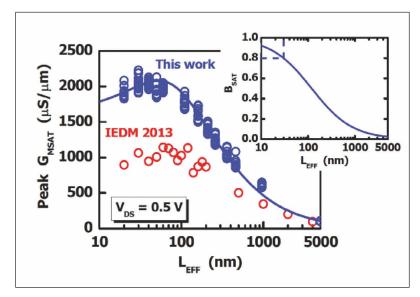

What has been lacking so far from the experimentalist camp is the fabrication of transistors that are small enough to make an impact at around the 10 nm node. Gate lengths of existing InGaAs FETs tend to be 20 nm or more, and it is not clear whether the performance advantages over silicon will be maintained with scaling.

Theorists have looked into this, with a team from Samsung Semiconductor suggesting that for a fine width of 6 nm, a switch to an InGaAs n-type finFET will fail to produce a hike in performance. These calculations, which were presented at the International Electron Devices Meeting (see page 66 for a report

of III-V MOSFET developments presented there), indicate that strained germanium offers a better way forward, so long as devices can be formed with a low contact resistance.

Meanwhile, calculations from a team from the University of Udine present a different picture, suggesting that for a device with a 11.7 nm gate - transistors with that dimension are expected to make their foundry debut in 2020 - a switch from silicon to InGaAs delivers a 30 percent gain in on-current.

Based on these papers, there is clearly some uncertainty over the role that InGaAs FETs could play in the future of CMOS. What is clear is that introducing these devices into foundries will not be easy, so unless the increase in performance is substantial, it is possible that a switch to III-V transistors will never happen.

Editor Richard Stevenson Contributing Editor Rebecca Pool News Editor Christine Evans-Pughe Publisher Jackie Cannon Senior Sales Executive Robin Halder Sales Manager Shehzad Munshi USA Representatives Tom Brun Brun Media Janice Jenkins

Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor Circulation Director Jan Smoothy

richardstevenson@angelbc.com +44 (0)1291 629640 editorial@rebeccapool.com chrise-p@dircon.co.uk +44 (0)1923 690205 jackie.cannon@angelbc.com robin.halder@angelbc.com +44 (0)2476 718109 +44 (0)1923 690215 shehzad.munshi@angelbc.com tbrun@brunmedia.com +001 724 539-2404 jjenkins@brunmedia.com +001 724-929-3550 sharon.cowley@angelbc.com +44 (0)1923 690200 mitch.gaynor@angelbc.com +44 (0)1923 690214 jan.smoothy@angelbc.com +44 (0)1923 690200

stephen.whitehurst@angelbc.com +44 (0)2476 718970 Chief Operating Officer Stephen Whitehurst Directors Bill Dunlop Uprichard - CEO, Stephen Whitehurst - COO, Jan Smoothy - CFO, Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal, Jason Holloway.

Published by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road Watford, Herts WD17 1JA, UK. T: +44 (0)1923 690200 F: +44 (0)1923 690201 E: ask@angelbc.com

Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/€158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2015. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV6 SSP UK. The 2015 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: Pensord Press. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2015.

### features

34 Optimising devices with wafer bonding

> Wafer bonding forms high-performance devices with insulating and conducting interfaces

41 Meeting the need for low-cost **MOSFETs**

MOSFETs made from SiC can plummet in price

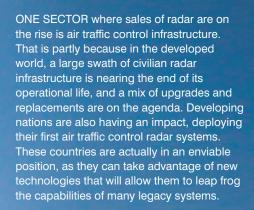

46 GaN gives power to L-band radar

> Increased efficiencies, superior power handling capabilities give GaN the upper hand

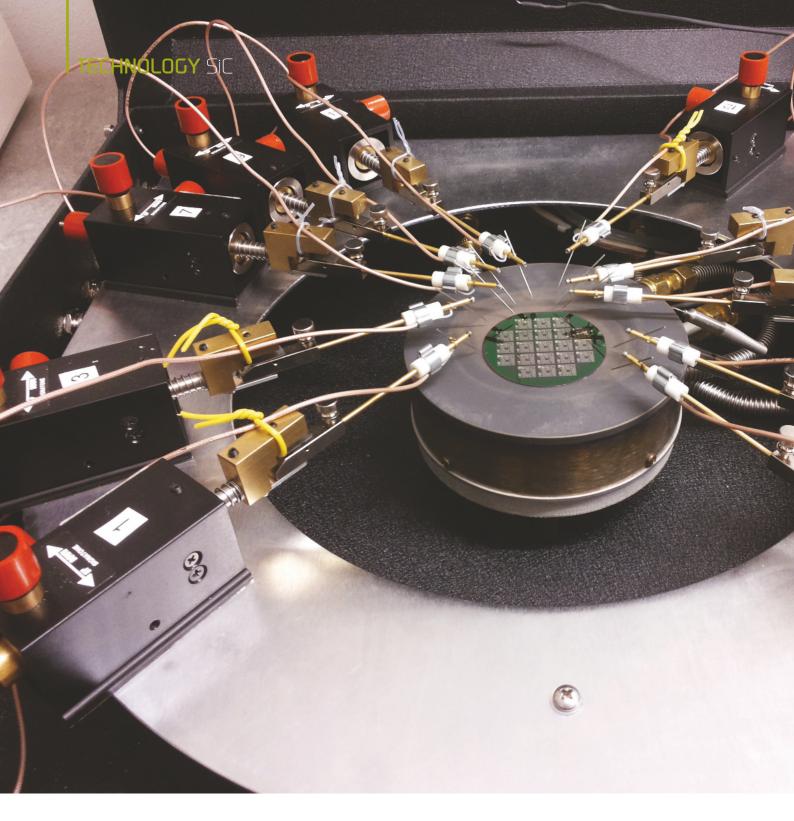

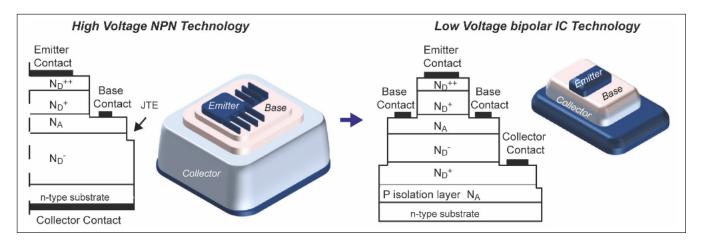

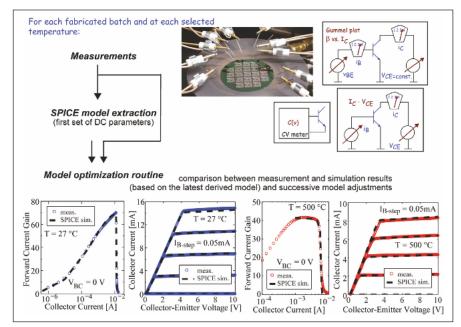

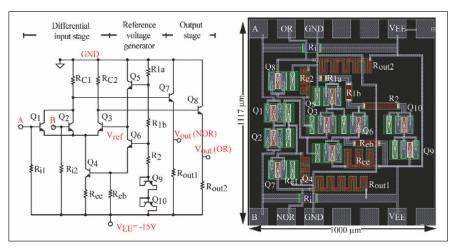

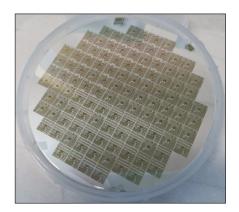

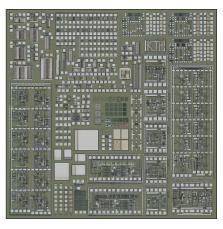

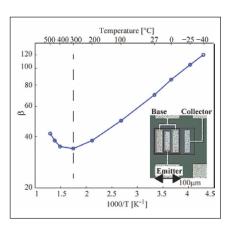

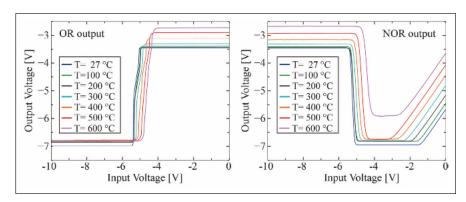

50 Turning to history for hightemperature integrated circuits The bipolar junction transistor is given a new of life in SiC circuits operating at 600°C

56 Increase the competitiveness

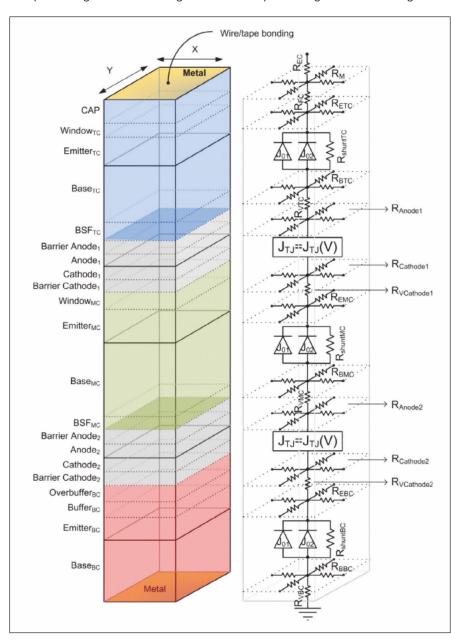

Slashing the cost of CPV will not come from just edging up efficiency

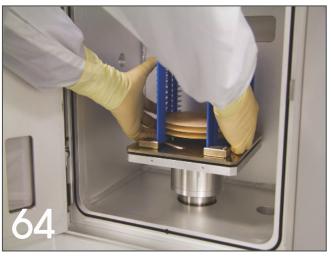

**62** Getting a grip on sapphire etching

> Novel clamping of sapphire looks to unleash brighter, cheaper LEDs

66 Will III-Vs make an impact in next-generation CMOS?

> Mixed messages emerge from IEDM, with experimental efforts highlighting the promise of III-V transistors and calculations unveiling some weaknesses

#### news

- 06 International team constructs first group IV semiconductor laser

- 08 Epistar to buy TSMC's LED subsidiary

- 09 International Rectifier is now part of Infineon

- 10 IQE financial end of year as expected

- 12 Sanan orders 50 MOCVD reactors

- 13 Cree launches extreme high power LEDs

- 14 NSF awards half million \$ to develop arrays of blue and green VCSELS

- 15 Allos Semiconductors to offer Azzurro patents and technology

- 22 Anvil sizes up LED markets

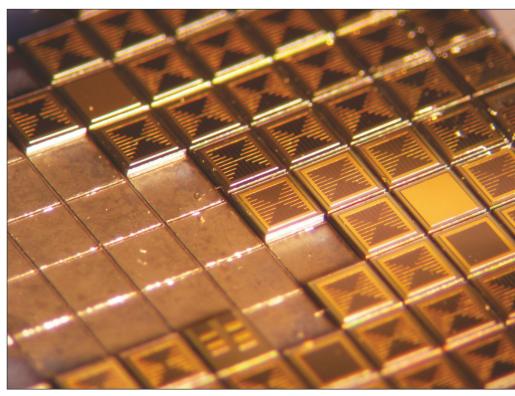

- 24 Terahertz triumph

- 26 GaN substrates fresh from China

- 28 M/A-COM: The future and beyond

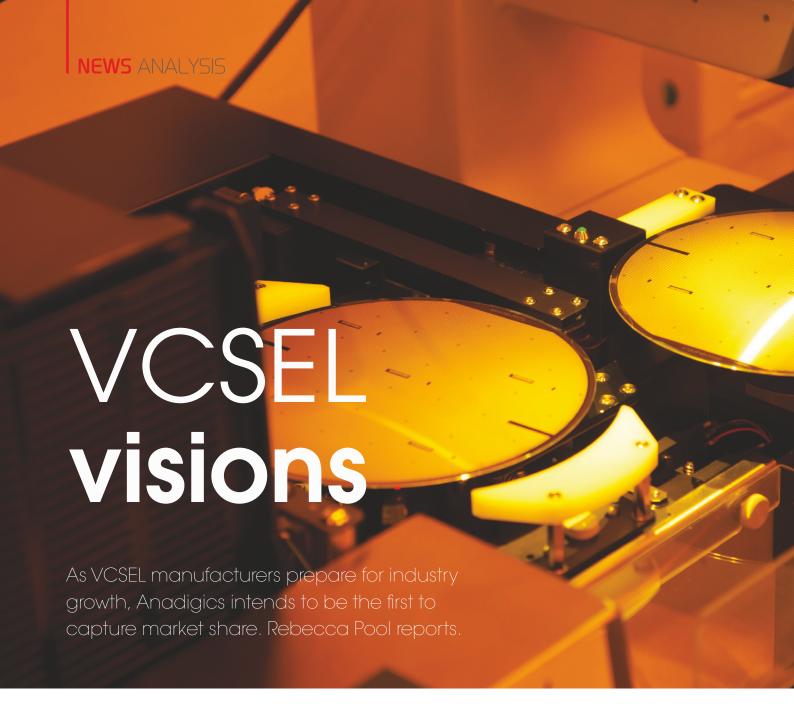

- 30 VCSEL visions

- 32 Executive View Q&A

#### research review

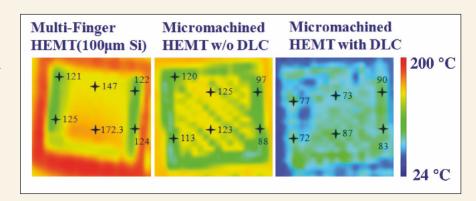

- 72 Diamond-like carbon enhances GaN HEMTs

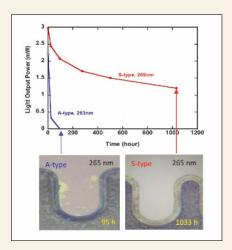

- 73 Polymer boosts deep-ultraviolet LED output

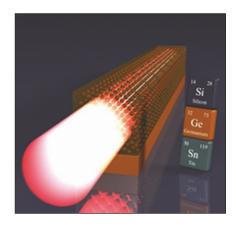

# International team constructs first group IV semiconductor laser

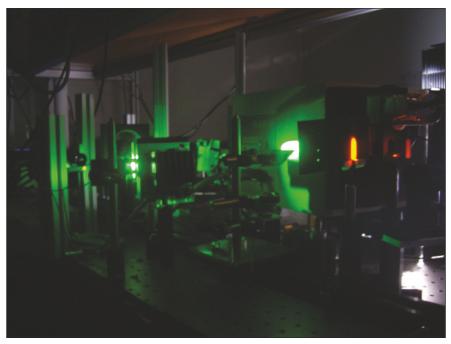

SCIENTISTS from Forschungszentrum Jülich and the Paul Scherrer Institute in Switzerland in cooperation with international partners have made the first GeSn semiconductor laser, which is also the first made solely of group IV elements.

The GeSn laser can be applied directly onto a silicon chip, creating a new basis for transmitting data on computer chips via light: this transfer is faster than is possible with copper wires and requires only a fraction of the energy. The results were published in the journal Nature Photonics.

"Signal transmission via copper wires limits the development of larger and faster computers due to the thermal load and the limited bandwidth of copper wires. The clock signal alone synchronising the circuits uses up to 30 percent of the energy - energy which can be saved through optical transmission," explains Detlev Grützmacher, director at Jülich's Peter Grünberg Institute.

Typical semiconductor lasers consist of elements from groups III or V and their crystal properties are such that they cannot be directly integrated onto silicon. In contrast, group IV semiconductors - to which both silicon and germanium belong - can be integrated into the manufacturing process without any major difficulties, according to the researchers.

However, neither element is very efficient as a light source. They are classed among the indirect semiconductors. In contrast to direct semiconductors, they emit mostly heat and only a little light when excited. That is why research groups all over the globe are intensively pursuing the objective of manipulating the material properties of germanium so that it would be able to amplify optical signals and thus make it a usable laser source.

The scientists at Jülich's Peter Grünberg Institute have now for the first time succeeded in creating a 'real' direct group IV semiconductor laser by combining germanium and tin. "The high tin content is decisive for the optical

properties. For the first time, we were able to introduce more than 10 percent tin into the crystal lattice without it losing its optical quality," reports PhD student Stephan Wirths.

"The functioning of the laser is so far limited to low temperatures of up to -183°C, however. This is mainly due to the fact that we worked with a test system that was not further optimised,"

adds Dan Buca. In cooperation with his colleagues from Siegfried Mantl's group at PGI-9, Stephan Wirths applied the laser directly onto a silicon wafer whose properties were subsequently measured at the Paul Scherrer Institute in Switzerland.

PhD student Richard Geiger fabricated the laser structures there. "That way, we were able to demonstrate that the GeSn compound can amplify optical signals, as well as generate laser light," reports Hans Sigg from the Laboratory for Micro and Nanotechnology.

The laser was excited optically for the demonstration. Currently, the scientists in Dan Buca's group at Jülich are working on linking optics and electronics even more closely. The next big step forward will be generating laser light with electricity instead, and without the need for cooling if possible. The aim is to create an electrically pumped laser that functions at room temperature.

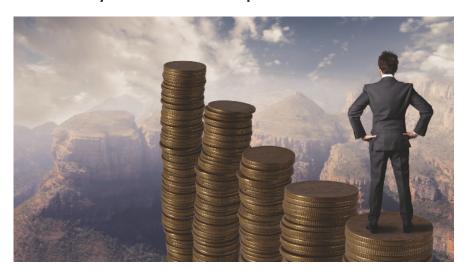

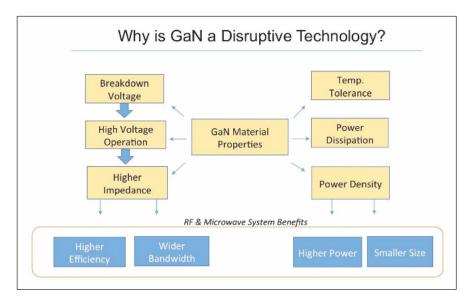

#### GaN Power conversion market to hit \$1.1 Billion in 2024

ACCORDING TO A REPORT by Lux Research, the market for GaN discrete components in 2024 will reach \$1.1Billion market. However, the substrate that the GaN device is built on - silicon, SiC, or GaN - makes a big difference in the cost and performance of the device. GaN-on-Si will dominate the GaN market for at least the next decade, growing to \$1 billion in 2024, a 90 percent share, says the report.

"Of the three GaN flavours, GaN-on-Si will be the cheapest, pushing adoption of GaN-on-SiC or GaN-on-GaN out into the future," said Pallavi Madakasira, Lux Research Analyst and the lead author of the report titled, 'Breaking Down the Gallium Nitride Power Electronics Market'. Even though both GaN-on-SiC and GaN-on-GaN offer performance improvements over silicon, high prices for SiC and GaN substrates will limit adoption," she added. Lux Research analysts evaluated the overall GaN market, besides evaluating the growth

prospects of the three GaN flavours. Among their findings are that transportation and renewables/grid are key markets. GaN-on-Si will be the runaway leaders in the renewables and grid markets, as well as transportation, attaining markets of about \$350 million and \$380 million, respectively, in 2024. Next in adoption will be IT and electronics.

GaN-on-SiC will grow the fastest. GaN-on-SiC will grow at a 46 percent CAGR from 2017 to 2024, reaching \$140 million. Driven by the SiC substrates' ability to function efficiently at high temperatures, it will gain the most adoption in transportation. GaN-on-GaN is a non-starter for now.

The lack of cheaper GaN substrates and a relative lack of developers mean GaNon-GaN will have little commercial role in the next decade. More R&D is needed on cost-saving innovations like hybrid manufacturing processes.

# EPITAXIAL GROWTH partner

# Enabling advanced technologies

- World leading technology

- Complete materials range

- MOCVD, MBE, CVD

- Advanced semiconductor wafer products

- Advanced R&D capabilities

- Multiple, manufacturing sites (Europe, Asia, USA)

www.iqep.com

### Epistar to buy TSMC's LED subsidiary

EPISTAR and TSMC have approved the sale of TSMC Solid State Lighting to Epistar for \$25.85 million.

After the transaction, Epistar will own 94 percent of the company, and TSMC will exit the LED business. The company will be operated by Epistar and TSMC SSL's current team. TSMC SSL has recently developed high-efficiency LED lighting products using an innovative Phosphoron-Die (PoD) chip-scale packaging technology. However, the company

has struggled to reach profitability due to oversupply following the massive expansion of the LED industry in the past few years.

As a late entrant, TSMC SSL has also faced difficulties overcoming patent obstacles and establishing sales channels. Epistar is the world's largest manufacturer of LED epitaxial wafers and dies, with patents recognised by the major industry players, cross-licensing with Philips and Toyoda Gosei, and a

wide network of sales channels covering customers across the globe.

Speaking on his hopes for collaboration, TSMC SSL chairman Steven Tso said: "I believe that we can reach a win-win scenario with TSMC SSL led by Epistar and SSL's present team. Epistar's operations can take off with redoubled strength, the development of the LED industry will accelerate, and consequently TSMC SSL's shareholders and employees will benefit as well."

LED lighting demand is expected to increase significantly between 2014 and 2017, with a rapid increase in penetration rate. Epistar successfully acquired Formosa Epitaxy at the end of 2014 with the goal of obtaining the capacity and talent needed to drive growth.

#### 8 benefits of sponsoring CS International 2015

- Senior management networking opportunities

- Increased company and brand awareness

- Access to the top strategists within the compound semiconductor industry

- Create, develop and support customer relationships

- Engage in debate, share insight and expertise on industry

- Gain visibility and recognition as an industry leader

- Leverage exposure in multiple industry media

- Demonstrate market innovation and leadership by launching new services, products and systems

#### www.cs-international.net

Call now +44 (0)24 76718970, email event@cs-international.net or view the online sponsorship pack at mediapack.cs-international.net

Connecting, informing and inspiring the compound semiconductor industry

#### Aixtron to continue restructuring

AIXTRON, the German maker of semiconductor deposition systems, has announced that as part of its continuing reorganisation, it plans to reduce around 60 of 800 jobs across the group.

Additionally, it will be continuing with other cost-cutting measures, and pursuing new market opportunities, for example with its new AIX R6 next generation MOCVD tool for LED manufacturing and in future business fields such as power and logic semiconductors as well as OLED.

"Letting employees go is never easy. As management, however, we have a responsibility for the whole company. Having reduced the executive board to two members in the middle of last year already should be viewed in the same light", said Martin Goetzeler, CEO.

"Customer needs are evolving. The focus is increasingly on process and useroriented solutions while we are executing our productivity programs in all areas of the company", commented Bernd Schulte, chief operating officer.

Aixtron will present its figures for the 2014 financial year and provide an outlook for the current year on February 24, 2015.

## International Rectifier now part of Infineon

INFINEON TECHNOLOGIES AG has announced the closing of the acquisition of International Rectifier. The El Segundo based company has become part of Infineon following the approval of all necessary regulatory authorities and International Rectifier's shareholders.

"The acquisition of International Rectifier is an important step for Infineon to foster our position as a global market leader in power semiconductors. We are sure that International Rectifier and its employees will make a great contribution to a joint successful future. Together both companies make a powerful combination", says Reinhard Ploss, CEO of Infineon. "We offer our customers an unparalleled product portfolio.

Our profound understanding of their needs enables us to provide the best possible and competitive solutions. The acquisition helps us to accelerate our strategic approach 'from product thinking to system understanding'."

The combined company is led by Reinhard Ploss, CEO, Arunjai Mittal, Member of the Management Board Regions, Sales, Marketing, Strategy Development and M&A, and Dominik Asam, CFO. President of International Rectifier and of Infineon North America is Robert LeFort.

International Rectifier is complementary to Infineon: the combined company gains greater scope in product portfolio and regions, especially with small

Infineon's board (L - R): Arunjai Mittal, Reinhard Ploss, and Dominik Asam

and medium enterprise customers in the US and Asia. The merger taps additional system know-how in power management. It expands the expertise in power semiconductors, also combining leading knowledge in compound semiconductors, namely GaN.

Furthermore, the acquisition will drive greater economies of scale in production, strengthening the competitiveness of the combined company.

The acquisition is expected to be accretive to pro-forma earnings per share (EPS) already in the current fiscal year. Synergies are expected to further drive significant accretion, building on International Rectifier's existing successful operational restructuring.

At the latest within fiscal year 2017, International Rectifier's margin contribution is expected to be at least in line with Infineon's target of 15 percent Segment Result margin over the cycle.

On August 20, 2014, Infineon had announced that it was to acquire International Rectifier in a deal worth approximately \$3 billion.

The Board of Directors of International Rectifier and Infineon's Supervisory Board unanimously supported the offer of Infineon to pay USD 40 per outstanding share. Subsequently, all regulatory authorities had approved the acquisition - as did the shareholders of International Rectifier with a majority of 99.5 percent of all votes cast.

#### SAMCO offer customer demos on new GaN-on Si MOCVD system

SAMCO, the Japanese semiconductor process equipment company, has announced MOCVD demonstration capability on a new GaN-on-Si system, the GaN-550, from Valence Process Equipment Inc (VPE) of Branchburg NJ, USA.

SAMCO sells and distributes the GaN-550, which is equipped with a 550 mm in diameter carrier for mass production of GaN power devices. The demo system will be available for customer demonstrations at SAMCO's R&D facility in early 2015. SAMCO is expanding its wide range of dry etching and plasmaenhanced chemical vapor deposition

(PECVD) systems for wide-bandgap semiconductor applications such as LEDs, laser diodes and RF devices. One of SAMCO's strengths is the process of nitride semiconductors, which play important role in green electronics.

VPE is a start-up company, providing MOCVD systems for GaN-based LEDs. VPE's GaN-500 MOCVD system employs a unique reaction chamber design and is highly-efficient at reducing gas consumption by up to 40 percent compared with other MOCVD systems. SAMCO has installed a new GaN-550 MOCVD system, which was developed

from GaN-500, and has low process gases consumption, high-speed gas switching, and superior temperature

The specially designed gas injector requires fewer reactor cleanings, which increases system availability and uptime.

The GaN-550 system can grow more than 5µm/hour GaN at the uniformity of less than 1 percent. While the carrier size of GaN-500 is 500 mm in diameter, the carrier size of GaN-550 is 550 mm in diameter for higher throughput, up to 2 inch x 72, 4 inch x 20, 6 inch x 7 or 8 inch x 4 per batch.

### IQE: Financial end of year as expected

IQE PLC, a supplier of advanced wafer products and services, has provided an unaudited trading update for the year ended 31 December 2014.

The group's revenue for the year is expected to be approximately £112m, with second half revenues of around £60 million. Other headline trading figures are also expected to match expectations. EBITDA is projected to be up by around 8 percent year on year at approximately £27m, following a second half EBITDA of approximately £16 million. Adjusted, fully diluted EPS for the year is expected to be up around 20 percent at approximately 2.4p.

The company also says that net debt at 31 December 2014 will be around £31 million, down from £34.4 million a year earlier. This progress has been made after approximately £5 million of cash restructuring costs (now complete) and after approximately £8 million of contingent deferred consideration (payments of which will end in 2016).

The company says that the wireless business is enjoying an improved outlook, the photonics business continuing to show strong double digit growth, and the group's new technologies, including the development of the GaN, progressing well.

Drew Nelson, CEO and president of IQE plc, said: "We are excited by the market developments that are leading to the increasing deployment of compound semiconductor solutions across a range of applications, and that consequently offer potential for IQE to deliver continued steady growth as a result of the Group's unique position in the compound semiconductor materials marketplace.

He added: "We are confident about the progress that we expect to make during 2015. I look forward to updating shareholders on the how we are performing when we announce our final results in March."

The compound semiconductor materials that IQE makes are used in a diverse range of end markets including wireless communications, a broad range of consumer and industrial applications using advanced photonic lasers and

sensors, high resolution infrared systems, advanced solar power (CPV), high efficiency LED lighting, and efficient power switching.

IQE is working with silicon chip companies and on a number of major government-funded programmes to develop next generation technology which will combine the scale and maturity of the silicon industry with the advanced properties of compound semiconductors.

Historically, approximately 80 percent of IQE's sales have been into the wireless communications market.

This market continues to enjoy significant and sustainable long term growth, driven by the proliferation of increasingly complex wireless communication devices and systems such as LTE/4G, dual band WiFi, and GPS location devices, which require increasingly complex compound semiconductor solutions.

#### Soraa completes line of LED lamps

SORAA has extended its line of PAR and AR111 lamps to offer a full range of halogen replacement lamps from 50W to 120W halogen equivalent. The newly launched 12.5W line features a lower wattage addition to its award-winning, full visible spectrum PAR30 and AR111 LED lamps, while maintaining the high Centre Beam Candle Power (CBCP) characteristic of Soraa's lamps. Featuring Soraa's third generation GaN on GaN LED, the company's new 12.5W PAR30 lamps are for 75W to 120W equivalent lighting applications in retail, hospitality and museum environments; while the 12.5W AR111 lamps offer an efficient choice for retail applications.

"The market is awash in low performance, poor light quality PAR30 and AR111 LED lamps, so when we introduced our full visible spectrum large LED lamp portfolio earlier this year, the reception was outstanding. And I'm pleased to announce that today, we made those lamps better," explained George Stringer, senior VP Americas sales and marketing at Soraa.

# ISS EUROPE 2015

### IoT — A New Era of Innovation for Europe

The industry is now entering the space of the "Internet of Things" that means both more advanced and low-end devices. Gathering data everywhere needs high connectivity, larger bandwidth, local storage, and big data in the cloud that will drive technology and device manufacturing costs. New manufacturing solutions based on plastic/flexible/printed electronics, advanced sensors, and actuators will be required to cost-effectively enable everything to connect. Powerful computing will analyze big data, making them useful for better and sustainable organizing of our businesses and individual needs. How will all this change our industry?

ISS Europe 2015 is ready to address all the critical issues surrounding the IoT future including the impact of a further consolidation of the semiconductor industry. Don't miss it!

#### **KEYNOTES**

The INTERNET of everyTHING: connecting the unconnected powers economic growth in Europe Luc Van den hove, President & CEO, imec

**Business Model Innovation – The power of recombining** Karolin Frankenberger, Assistant Professor of Business Administration, University of St. Gallen

IoT – a driver for European industrial competiveness Pierre-Damien Berger, Director Business Development and Communication, CEA-Leti

#### Sponsored by

Logo Sponsors

APPLIED.

**ASM**

22-24 February

Amsterdam.

The Netherlands

www.semi.org/isseurope

### Sanan orders 50 GaN MOCVD reactors

VEECO INSTRUMENTS has won an order from Sanan Optoelectronics, the largest LED manufacturer in China, for 50 TurboDisc EPIK700 GaN MOCVD reactors for the production of LEDs.

"Sanan chose the EPIK700 due to its industry leading cost of ownership model and excellent footprint efficiency," said Zhiqiang Lin, Vice Chairman and CEO of Sanan. "Our beta testing of EPIK700 proved its production-worthiness, and we are confident in its capabilities and

value to our Xiamen business expansion plans. Veeco has been a great partner for Sanan as we have solidified our position as the top LED manufacturer in China and increased our business outside of China as well."

Based on Veeco's TurboDisc technology, the EPIK700 MOCVD system should enable customers to achieve a cost per wafer savings of up to 20 percent compared to previous generation MOCVD systems through improved wafer

uniformity, reduced operating expenses and increased productivity. "This large order from Sanan, the largest single purchase order Veeco has received since 2009, speaks volumes about the EPIK700's production readiness and the recovery in the MOCVD market," said John Peeler, Veeco's Chairman and CEO.

"We are in a great position to continue to serve our LED customers with the best MOCVD technology and customer support, and remain the industry leader."

#### Raytheon GaN chips approved for space

RAYTHEON has successfully validated its GaN Monolithic Microwave Integrated Circuit (MMIC) technology for use in space-bound equipment.

Raytheon GaN MMICs, fabricated at its Andover, Massachusetts foundry, demonstrated the radiation hardness required for space through Single Event Burn-out (SEB) and Total Ionising Dose (TID) testing.

The results showed the devices are not susceptible to catastrophic failure caused by heavy ions. Further testing showed no loss of performance at exposure levels up to 1Mrad, significantly more than is needed for typical space applications.

"Raytheon's GaN technology is mature, robust, and already integrated into a number of defense systems for land, sea and air," said Paul Ferraro, Raytheon's vice president of Integrated Defense Systems' Advanced Technologies Programs. "Now that our GaN is validated for space, Raytheon customers can use this game-changing technology in a wide variety of space-based applications."

# Cree launches extreme high power LEDs

CREE has announced the commercial availability of XLamp Extreme High Power (XHP) LEDs, a new class of LEDs that enable a system cost reduction of up to 40 percent for lighting applications.

The first LEDs powered by Cree's SC5 Technology Platform, XLamp XHP50 and XHP70 LEDs provide twice the lumen output and improved reliability compared to previous LEDs of the same size. The technology of the new XHP LEDs will help drive the next major innovations in lighting system design.

"Cree's new technology is gamechanging compared to the incremental advances of other LED suppliers. The breakthrough performance of XHP LEDs enables both new design possibilities and dramatically lower system costs for LED lighting," said Nate Heiking, advanced lighting Product Manager, Kenall Lighting. "We're excited that Cree's new class of Extreme High Power LEDs will accelerate customer adoption of LED lighting."

XHP LEDs allow lighting manufacturers to reduce the size and cost of their lighting system design by using fewer, more reliable LEDs to achieve the same brightness. XHP LEDs enable new lighting designs that require fewer optics, a smaller printed circuit board, a smaller housing and less handling. XHP LEDs also achieve longer lifetimes even at higher operating temperatures and currents than previous LED technology, allowing lighting manufacturers to reduce heat sink size and cost without impacting the rated lifetime.

In addition, XHP LEDs enable other cost reductions at the system level not possible with other LED solutions. For example, in roadway and outdoor area lighting, on top of the luminaire cost savings, XHP LEDs can produce a radically smaller and lighter luminaire that requires a less expensive pole. Similar dramatic cost savings over existing solutions may be achieved in a wide variety of lighting applications, including track, stadium and high bay.

"Cree's new Extreme High Power LEDs demonstrate our belief that high-

power LEDs are what will drive the industry towards the next generation of lighting system designs," said Dave Emerson, Vice President and general manager for Cree LEDs. "Leveraging our groundbreaking SC5 Technology Platform, Cree's new XHP LEDs deliver not only exceptional performance, but also enable up to 40 percent system level cost reductions."

As the first LEDs to incorporate the SC5 Technology Platform, the new XHP LEDs are said to introduce significant advancements in light output, colour consistency and design flexibility.

XLamp XHP50 and XHP70 LEDs shatter the industry's perceived limit of LED lumen density by delivering up to 2546 lumens at 19 watts from a 5.0 x 5.0 mm package and up to 4022 lumens at 32 watts from a 7.0 x 7.0 mm package, respectively.

Through improvements in the light conversion process, Cree has reduced LED-to-LED color variations and, among other options, offers XHP LEDs in 2-step and 3-step EasyWhite bins for 3500K through 2700K in 80 and 90 CRI. The XHP LEDs introduce a new, innovative package that allows manufacturers to choose either 6 V or 12 V configurations from the same LED through the solder pad design on the circuit board.

Samples of both XLamp XHP50 and XHP70 are available now, and production quantities are available with standard lead times.

#### Emcore closes sale of tunable lasers and transceivers to NeoPhotonics

EMCORE, a provider of compound semiconductor-based components, subsystems, and systems, has completed the previously announced sale of its tunable laser and transceiver product lines for \$17.5 million to NeoPhotonics.

With the closing of the transaction, Emcore received \$1.5 million in cash and a promissory note from NeoPhotonics in the principal amount of \$16 million.

The promissory note will mature two years from the closing date of the transaction, subject to repayments under certain circumstances, and is secured by certain of the assets sold to NeoPhotonics in the transaction. The purchase price is subject to certain post-closing adjustments for inventory, net accounts receivable and pre-closing revenue levels, which will increase or decrease the principal amount of the promissory note as applicable.

NeoPhotonics, based in San Jose, California, is a designer and manufacturer of photonic integrated circuit, or PIC, based optoelectronic modules and subsystems for bandwidth-intensive, high-speed communications networks. The sale includes Emcore's External Cavity Laser (ECL)-based Integrable Tunable Laser Assembly (ITLA), micro-ITLA, Tunable XFP transceiver and Integrated Coherent Transmitter (ICT) products for 10, 40, 100 and 400 Gbps telecoms networks.

Emcore retains its broadband fibre optics products including CATV transmitters and modules, Fibre-to-the-Premise transceivers, InP-based lasers, photodiodes and modulators, RF over fibre satellite communications products, video transport equipment, and microwave and speciality photonics products.

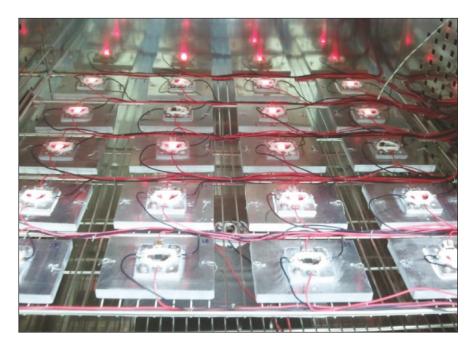

# NSF awards half million dollars to develop arrays of blue and green VCSELS

THE US NATIONAL SCIENCE FOUNDATION (NSF) has awarded a \$500,000 Faculty Early Career Development award to Daniel Feezell at the University of New Mexico to study VCELS. The 'Short-Wavelength Vertical-Cavity Surface-Emitting Laser Arrays Using Nonpolar and Semipolar GaN' project begins in March and continues through February 2020.

The goal is to develop arrays of blue and green VCSELs with stable polarisation of the light emission by using novel orientations of the GaN. Applications of this technology, according to Feezzell, could include improved high-density optical data storage and high-resolution printing, improved mobile displays and projectors, and advancements in chemical/biological sensing and atomic clocks.

One example of a possible practical application would be the addition of projection capabilities on smartphones. Feezell said such a projector could be included on the back of the phone, right next to the camera.

"This would allow your phone to become a display projector, so you could view movies, pictures, or PowerPoint slides on the wall or on a screen instead of directly on your phone," Feezell said. "You could basically have a projector in your pocket."

He said the vertical geometry of VCSELs has several advantages over conventional edge-emitting lasers, including high beam quality, small form factor, the ability to form densely-packed arrays, and lower power consumption. Feezell's work will focus on adding stable polarisation and increasing the output power using arrays.

Feezell said he will also be researching how to create a green VCSEL, which has not yet been developed. Red and blue VCSELs have been developed, and adding a green VCSEL would complete the RGB (red, green, blue) spectrum, allowing for the creation of white light,

which makes possible technologies such as display screens or LED light bulbs for room lighting and other uses.

Much of the work on the project will be done at UNM's Center for High-Technology Materials, and some will be done in collaboration with the Center for Integrated Nanotechnologies at Sandia National Laboratories.

Feezell said he believes that GaN-based VCSELs hold untapped potential. "I love this particular topic of GaN-based VCSELs," he said. "It's still an immature field and many of the applications are still not developed or known."

The NSF CAREER program is geared toward helping early-career faculty get strong starts on their academic careers.

The award is NSF's most prestigious award in support of junior faculty who exemplify the role of teacher-scholars through outstanding research, excellent education, and the integration of education and research within the community. Such activities should build a firm foundation for a lifetime of leadership in integrating education and research.

#### VI C Photonics expand optical integration services

AS PART of its optical integration services, VLC Photonics is offering a new Multi-Project Wafer (MPW) Standard Design service for custom photonic integrated circuits (PIC) with fixed service costs for each manufacturer and cell size. The MPW shuttle runs are available on different generic technology manufacturing platforms such as Silicon-on-Insulator, PLC, TriPleX

"After several years in market, by serving customers and performing our own R&D using all the MPW manufacturers around the globe, we are ready to offer a frozen price, independent of the chip functionality", Pascual Muñoz, VLC Founder explained. "This is the equivalent to generic manufacturing, where costs are fixed by chip area independently of its content and end functionality, but at a design level" he added.

"The wide range of integration technologies and fabrication platforms makes selecting the best manufacturing approach for each application and device quite difficult for our customers," adds Iñigo Artundo, CEO of the company. "We learned our customers value an easy and straight-forward solution that allows to directly choose the most suited way to prototype their PICs". Artundo assures that any company with some basic experience on photonic integration will be able to navigate all the MPW design and manufacturing options currently offered by VLC Photonics.

"Customers will also be able to get approximate costs and manufacturing times to configure their own projects immediately. Furthermore, they will directly interface our engineers one click after, to clear out any hurdles they may find when facing any integration project".

# Allos Semiconductors to offer Azzurro patents and technology

ALLOS SEMICONDUCTORS GMBH, formed in mid-2014 in Dresden, to focus on GaN-on-Si technologies and markets, has acquired the exclusive ownership of the technology, knowhow, and IP of former Azzurro Semiconductors.

Azzurro, a spin-off from the University of Magdeburg in Germany, specialising in GaN-on-silicon epi-wafers and products, filed for bankruptcy earlier this year.

The driving force behind Allos Semiconductors' foundation in June was the growing demand for technology to

grow GaN on silicon substrates. An increasing number of LED and power semiconductor companies want to master the technology to grow 150 and 200mm GaN-on-Si wafers successfully themselves to supply cost-effective high-quality GaN devices processed in standard silicon fabs.

According to Allos, there are tremendous technological challenges to make GaNon-Si happen.

For Allos' customers, it says, the opportunity is to reduce not only cost and time-to-market but also the development risk by building their effort on Allos' proven GaN-on-Si platform and know-how. Now with the acquisition of Azzurro's IP, in addition to its existing offering, Allos will make the proven Azzurro technology platform available through technology transfer, licencing and customised development

Allos says that this will complement its service offering advice on business and technology strategies and supporting setting up GaN-on-Si operations all the way from establishing an epitaxial wafer fab to market entry.

#### EPC introduces 60V and 80V monolithic GaN half bridges

EPC has announced the EPC2102, 60V and the EPC2103, 80V enhancementmode monolithic GaN transistor half bridges.

For applications requiring a symmetric device ratio, the devices provide monolithic half-bridge eGaN ICs with two equal-sized die. By integrating two eGaN power FETs into a single device, interconnect inductances and the interstitial space needed on the PCB are eliminated. This increases both efficiency (especially at higher frequencies) and

power density, while reducing assembly costs, says EPC.

Using an EPC2103 in a typical buck converter, system efficiency is greater than 97 percent at 20 A, when switching at 500 kHz and converting from 48V to 12V.

The second device, the EPC2102 60 V half bridge, achieves 98 percent system efficiency at 18 A, when switching at 500 kHz and converting from 42 V to 14 V. In addition to the single-chip half

bridges, two development boards are being announced. The EPC9038 and the EPC9039 boards contain one EPC2102 or EPC2103 integrated half-bridge component, respectively, along with a Texas Instruments LM5113 gate driver and all necessary supply and bypass capacitors.

The board has been laid out for optimal switching performance and there are various probe points to facilitate simple waveform measurement and efficiency calculation.

CS International 2015 will provide timely, comprehensive coverage of every important sector within the compound semiconductor industry.

The 5th CS International conference will be held at the Sheraton Frankfurt Airport Hotel, in Germany on Wednesday 11<sup>th</sup> & Thursday 12<sup>th</sup> March 2015. The conference will build on the success of its predecessors, with industry-leading insiders delivering more than 35 presentations spanning six sectors.

Please visit www.cs-international.net for further information on this event.

#### **Book your place NOW**

Please visit www.cs-international.net/register.php to secure your place

#### TWO DAYS, SIX THEMES, OVER 35 INSPIRING PRESENTATIONS

Six key themes lie at the heart of CS International 2015: solid-state lighting, power electronics, front-end mobiles, optoelectronics, III-V CMOS and RF electronics. Within each topic there is a key-note presentation from one of the most influential companies within each sector; one talk by a leading market analyst who will discuss trends within the industry and presentations by the leaders of firms developing cutting-edge technology in each field.

Connecting, informing and inspiring the compound semiconductor industry

#### 35+ presentations over two days covering six themes

#### **SOLID-STATE LIGHTING**

Soaring sales of LED bulbs are creating a great opportunity for chipmakers. But what do companies need to do to stand out from the crowd and win substantial orders while maintaining healthy margins?

Opportunities for laser diodes in solid-state lighting

Jon Wierer - SSLS Scientist - Sandia National Laboratories

Will Rhodes - Research Manager - IHS Technology

**ANALYST**

How will the solid-state lighting evolution unfold, and what will it mean for the LED chipmakers?

SPEAKER

Commercialisation of GaN-on-silicon for LEDs

Keith Strickland - Innovations & Technology Director - Plessey Semiconductors

**SPEAKER**

Increasing LED output with advanced plasma processing Mark Dineen - Product Manager - Oxford Instruments Plc

Torsten Stoll - Product & Marketing Manager - Nanometrics Inc.

**SPEAKER**

Yield optimisation of compound semiconductor processes through an effective metrology strategy

nanometrics

SPEAKER

Plasma dicing for III/V and thin wafers

Reinhard Windemuth - Sales Director ME Europe - Panasonic Factory Solutions

Panasonic

#### **OPTOELECTRONICS**

Does the growth of the datacom market signal a long-awaited return to better times for the makers of optical components? Is CPV technology finally starting to gain a foothold in the solar industry?

KEYNOTE

Highest CPV cell and module efficiencies and CPV power plants Rainer Krause - Director Smart Cell Development - Soitec

**ANALYST**

Where is the CPV industry heading, and what needs to happen to increase its market share?

Karl Melkonyan - Analyst Solar Research - IHS Technology

**SPEAKER**

Mid infrared LEDs enable portable, battery powered gas sensing **Des Gibson - CEO - Gas Sensing Solutions Ltd**

**SPEAKER**

IC design for very high-speed optical communications – a holistic approach

The' Linh Nguyen - Senior Manager IC Development- Finisar Corporation

**SPEAKER**

UV LED - We are just scratching the surface of the technology's true potential Pars Mukish - LED & Sapphire Activities Leader - Yole Développement

**SPEAKER**

Unlocking opportunities for compound semiconductors with micro assembly Chris Bower - CTO - X-Celeprint Ltd

Delegate registration: www.cs-international.net/register.php

#### **III-V CMOS**

By the end of this decade, it is said that silicon CMOS will have run out of steam. But what role will III-Vs have to play in the microprocessors of the future?

Heterogeneous integration of III-Vs and CMOS

Daniel Green - Program Manager - Defence Advanced Research Projects Agency

ANALYST

When will III-Vs make an impact in the silicon foundries? And will it last for long? **Mike Corbett - Managing Partner - Linx Consulting**

LINX-Consulting

**SPEAKER**

III-V FETs for future logic applications

Jesús A. del Alamo - Director of the Microsystems Technology Laboratories - MIT

SPEAKER

Opportunities and challenges of III-Vs in Si-based nanoelectronics industry Matthias Passlack - R&D Deputy Director Europe - Taiwan Semiconductor Manufacturing Company

**SPEAKER**

Advanced in-situ metrology for III-V on silicon technology Kolja Haberland - CTO - LayTec AG

**SPEAKER**

Eliminating material borders for heterogeneous integration through new wafer bonding processes

Thomas Uhrmann - Head of Business Development - EV Group

#### **FRONT-END MOBILES**

What's the biggest threat to revenues for GaAs power amplifiers? Is it the emergence of multi-band, multi-mode PAs built with this material, or the emergence of CMOS solutions?

KEYNOTE

The path to intelligent integration

Jim Cable - CEO, President and Chairman - Peregrine Semiconductor Corporation

**ANALYST**

Multi-mode, multi-band PAs: friend or foe to the compound semiconductor industry?

Eric Higham - Director - Advanced Semiconductor Applications - Strategy Analytics

**SPEAKER**

Improving system level integration and overall efficiency Ed Anthony - VP Engineering - Skyworks Inc.

**SPEAKER**

LTE is driving complexity in smartphone design Sean Riley - VP of Mobile Products - Qorvo

Connecting, informing and inspiring the compound semiconductor industry

Delegate registration: www.cs-international.net/register.php

#### **POWER ELECTRONICS**

From a performance perspective, GaN and SiC are superior to silicon, but high prices are holding the materials back from displacing the incumbent silicon. How can this be addressed?

KEYNOTE

Ditching the package to drive down GaN transistor costs

Alex Lidow - CEO and Co-Founder - Efficient Power Conversion Corporation

**ANALYST**

When can WBG power electronics truly take off?

Pierric Gueguan- Senior Power Electronics Market Analyst - Yole Développement

**SPEAKER**

SiC technology in Power Electronics – A step change in value

Tang Yong Ang - VP Compound Semiconductors - Dow Corning Corporation

**SPEAKER**

High performance GaN-on-Si power epiwafers employing rare earth oxide buffer layers **Andrew Clark - VP Engineering - Translucent Inc.**

**SPEAKER**

Automated defect monitoring strategy for surface and photoluminescence yield impacting defects

Brian Crawford - Director of Business Development - KLA-Tencor

**SPEAKER**

Driving down costs for next-generation PVD processes

Reinhard Benz - VP Sales and Marketing - Evatec Ltd

SPEAKER

Gallium nitride epitaxy on large area silicon substrates for power applications Yoga Saripalli- Principle Engineer - GaN Epitaxy Group - imec

**SPEAKER**

Optimisation of III-V R&D and manufacturing using advanced analytical methods

Temel Buyuklimani - Senior Director, Quadrupole SIMS Services - Evans Analytical Group

**SPEAKER**

Accelerating GaN power electronics devices using MOCVD technology Sudhakar Raman - VP Marketing - Veeco Instruments

**SPEAKER**

Measurement solutions for high power WBG semiconductor materials and devices. How to optimise and minimise power conversion switching loss Stewart Wilson - European Business Manager - Keysight Technologies

**SPEAKER**

Cutting conversion losses with cost-efficient GaN-on-silicon Marianne Germain- CEO - EPIGAN nv

#### **RF-ELECTRONICS**

The potential of GaN in the RF arena has never been in doubt. But does it now satisfy all the requirements for deployment in the most taxing situations?

KEYNOTE

GaN for radar applications

Takahisa Kawai - General Manager - Sumitomo Electric Device Innovations, Inc.

SUMITOWO ELECTRIC DEVICE INVOVATIONS

ANALYST

The future for GaN, SiC, InP and GaAs in defence/military applications

Asif Anwar - Director - Strategy Analytics

STRATEGY ANALYTICS

**SPEAKER**

GaN for commercial RF applications enabled by the pure-play foundry model Walter Wohlmuth - Associate VP Technology - WIN Semiconductors Corporation

#### **Event Sponsors**

#### **Platinum**

#### Gold

#### Exhibition

Pen/USB Sponsor

Theme Sponsor

Delegate bag

Supported by

Delegate registration: www.cs-international.net

# Powered by ideas. Strengthened by collaboration.

Discover a higher industry standard for silicon carbide (SiC) crystal quality with Dow Corning's Prime Grade portfolio of 100 mm and 150 mm 4H n+ wafers. Three tiers of manufacturing-quality substrates offer unique solutions to achieve your power electronics design goals at an optimal price point.

#### **Dow Corning offers:**

- Industry-leading SiC crystal quality

- A highly reliable global supply of 100 mm and 150 mm SiC wafers

- Customized epitaxy product solutions for 600 V to >10 kV power electronics applications

Dow Corning's advanced SiC technology and expertise are redefining the boundaries of power electronics design and performance. Learn more at **dowcorning.com/SiC**.

# Anvil sizes up LED markets

WHILE ANVIL SEMICONDUCTORS has carved a name for itself developing SiC power semiconductor switches based on its novel, low pressure CVD growth process, the UK-based Warwick University spin-off is now eyeing LED markets. Joining forces with the Cambridge Centre for GaN at the University of Cambridge, the organisation has grown cubic GaN on cubic SiC-on-silicon, or 3C-SiC-on-silicon, wafers via MOCVD. Sample LEDs are next.

"We've been talking about growing cubic GaN on cubic SiC for around a year, as this potentially opens up the LED market for our 3C-SiC on silicon material," explains Jill Shaw, chief executive at Anvil Semiconductors.

"Growing cubic GaN is very difficult and nobody has successfully done it using a commercialisable process before, partly because they haven't grown it on the (100) face of a reasonably lattice matched substrate such as cubic SiC," she adds.

As Shaw highlights, the company's intellectual property lies in growing cubic SiC-on-silicon for power device applications. Prior to SiC growth, a mask is placed over the silicon wafer to define structures in the scribe lines of the wafer.

Anvil researchers then deposit a 1.5 µm-thick layer of heavily doped, dislocated material onto this silicon seed wafer to relieve stresses from lattice mismatches during SiC growth.

An Anvil wafer: researchers have grown cubic GaN layers on the cubic SiC-on-silicon wafers

Monocrystalline 3C-SiC is then grown in the die area between the scribe lines – where future devices will be fabricated – with polycrystalline SiC forming in the lines to soak up the thermal expansion differential stresses across the entire wafer.

Having fabricated 650 V Schottky diodes, MOSFETs and more, the process clearly works for power semiconductors, but can it stretch to LEDs?

While researchers worldwide have already grown conventional hexagonal GaN on sapphire, SiC, bulk GaN and silicon wafers, via MOCVD, cubic GaN is a different matter. Compared to hexagonal GaN, the cubic polymorph has no internal electric fields, a narrower bandgap and faster transport properties, paving the way to better performing green LEDs. However, the cubic phase of GaN is metastable, so from a thermodynamic perspective, the crystal structure of the semiconductor tends to revert to the lower energy hexagonal polymorph.

But, by modifying MOCVD parameters such as gas flow and temperature, the Cambridge Centre for GaN team managed to grow cubic GaN on quadrants from Anvil's 100 mm diameter 3C-SiC-on-silicon wafer.

"The Cambridge researchers actually said they didn't think the cubic GaN phase would be stable and growth would be difficult," says Shaw. "But by carefully selecting MOCVD parameters they successfully grew single phase cubic GaN straightforwardly and at a similar growth rate to hexagonal

With success in hand, the researchers are also growing multiquantum well structures onto the material, the next step to proving the material can be used to make LEDs.

Indeed, as Shaw puts it: "So far all we have done is demonstrate that you can produce cubic GaN on cubic SiC; we've still got to be able to develop LEDs."

But having applied for a government-funded Innovate UK award designed for developing innovative engineering ideas – Shaw and colleagues are hopeful a demonstration LED could be developed within a six month programme.

290

# Terahertz triumph

As Northrop Grumman and DARPA smash electronics speed records, project leaders reveal this is only the beginning. Rebecca Pool reports.

270

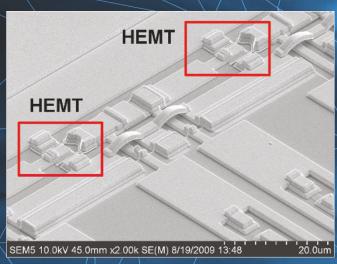

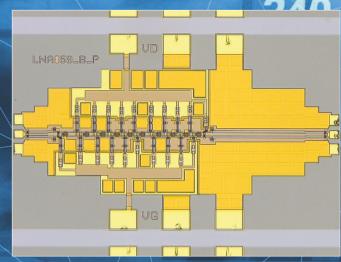

In late 2014, Northrop Grumman and DARPA set a world record with a breathtakingly fast terahertz integrated circuit amplifier, opening the door to extra-sensitive spectrometers, incredibly high resolution imaging and high capacity data networks.

The amplifier uses ten, 25 nm InP HEMTs in series to produce an overall gain of 10 dB at 1 THz, and 9 dB at 1.03 THz. These power gain figures massively outstrip those in state-of-the-art ICs, and according to the Northrop

Grumman-DARPA team, this is only the beginning.

"The team has made an amazing breakthrough by demonstrating an amplifier at 1 THz," says Dev Palmer, program manager of DARPA's THz Electronics program. "The theoretical maximum operating frequency of this technology is somewhere between 2 and 3 THz, so there's plenty of room at the top."

Terahertz is the slice of the electro-

magnetic spectrum that lies between infrared light and radio waves, from 300 GHz to 3 THz. Called the sub-millimetre wave frequency band, the wavelengths here are shorter than 1mm and able to penetrate many materials without using ionising radiation.

The chief aim of the Terahertz Electronics programme has been to fabricate all the components, from the subcomponents of an exciter to the parts for a receiver, needed to make a terahertz radio. To date, Northrup

DARPA's terahertz monolithic integrated circuit is the first solid-state amplifier demonstrating gain above 1 THz (1012 GHz).

Grumman, has achieved just this at 700 GHz and 850 GHz and is set to repeat history at a terahertz.

"A decade ago, there was no consensus in the scientific community whether an integrated circuit operating at one terahertz was technologically possible," says Bill Deal, program manager of Terahertz Electronics at Northrop Grumman "But, as an interdisciplinary team of scientists and engineers, [we have] worked together in scaling all facets of MMIC technology to enable this result."

The next crucial step is to increase the gain of the amplifier IC from 10 dB to more than 15 dB. As Deal explains: "We want to increase the gain to a level where it makes sense to package the component, and then it becomes a very easy-to-use laboratory component."

"To do this we need to get our gain above 15 dB, and we hope to achieve this in a matter of months," he adds.

And of course, scaling the electronics to boost gain and speed is as important as ever. Using MBE, Deal and colleagues grow the InP-based transistor's epitaxial layers, then using electron beam lithography to fabricate a T-gate to form the transistor. Scaling the gate length

is really critical," says Deal. "It reduces the capacitances and increases the maximum frequency of oscillation of the transistor, allowing the device to have gain at higher frequencies."

And while the gate length of a III-V device to 25 nm is small — today's standard CMOS processes have only just hit 14 nm — future gate sizes could shrink further yet.

"We do have some experiments aimed at shrinking the gate to as low as 20 nm," says Deal. "But a lot of this is very experimental and and other parts of the device have to be scaled at the same time to improve performance."

DARPA's Palmer has no qualms about the project's success, highlighting: "Northrop Grumman has demonstrated all components at 700 and 850 GHz, so I think it's well within their capability to build the same at 1 THz."

In the meantime, the team is also working on fabrication. In Deal's words, 'it's a very sophisticated process', but the researchers have fabricated the amplifier IC across several runs, each comprising batches of typically six wafers. Statistical analyses are underway as transistor performances

are monitored and improved.

Deal reckons the early adopters of the technology will be other researchers. "I actually see scientists using it first for applications such as atmospheric sensing and radio astronomy," he says. "These researchers are pushing the limits on the types of measurements they can do."

The project has also received interest from businesses looking to establish large bandwidth, short range data connections between data farms using radio links instead of fibre optics cable. However, the key applications are high resolution radar imaging and spectroscopy. "For high resolution imaging, image resolution increases as wavelength shrinks," explains Palmer. "And we have many molecules, including industrial chemicals, with distinct signatures in this frequency band for rotational spectroscopy."

And the breakthrough also brings good news for high data rate communications. "Even very small fractional bandwidths at terahertz frequencies are many gigahertz wide," adds Palmer. "So you can get high data rates without resorting to complex modulation schemes."

# GaN substrates

### fresh from China

A China-based manufacturer of GaN materials is ready to rival western players; Rebecca Pool talks to Wang Jianfeng of Nanowin to find out more.

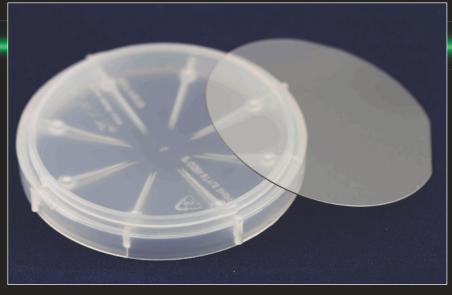

IN LATE OCTOBER, China-based semiconductor business, Nanowin, revealed plans to mass-produce high quality 2-inch GaN substrates with industry-low dislocation densities.

Targeting blue and green laser diode markets, the company claims to have demonstrated high-performance devices and is now intent on becoming a worldleading nitride semiconductor material provider.

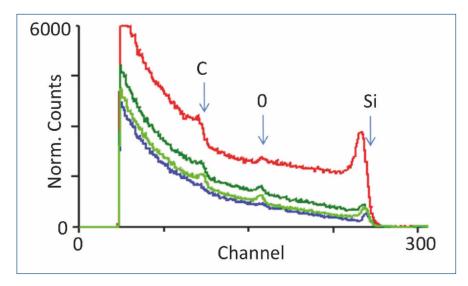

As Nanowin chief technology officer, Wang Jianfeng, points out, HVPE-grown GaN substrates, with a thickness of less than 1 mm, typically have a dislocation density of around 1 x 105 cm-2. However, the dislocation density of his company's substrates comes in at a much lower 1 x 10<sup>4</sup> cm<sup>-2</sup>.

The key to the company's impressive results lies in clever nanostructure etching at the initial GaN film surface and carefully controlled growth conditions. Using electrodeless photoelectrochemical etching, Jianfeng and colleagues etch arrays of nanopyramids into GaN films, grown on sapphire substrates, to relieve compressive stress within the film.

"We do some interface engineering at the GaN surface, fabricating nanostructures and then optimising initial growth conditions to reduce the dislocation

density," explains Jianfeng. "From the high quality GaN nanostructure layer, we then grow a very high quality GaN nanolayer."

The GaN substrate is grown via HVPE on a 'home-made' system that, according to Jianfeng, incorporates an in-situ optical monitoring system. During GaN growth, Jianfeng and colleagues can closely monitor myriad characteristics including wafer curvature, refraction and reflections, adjusting parameters accordingly to ensure uniform growth.

Clearly fabrication requires skilled intervention, but the company claims to currently be churning out around 200 substrates a month and according to Jianfeng, can produce up to 700 substrates a month.

"Our yield is around 75 percent," adds Jianfeng. "And in three years time we will be manufacturing more than 1000 pieces a month with a dislocation density of only 1 x 10<sup>4</sup> cm<sup>-2</sup>. These substrates will be for laser diode manufacturers."

Indeed, working with the Suzhou Institute of Nanotech and Nanobionics, Nanowin has already manufactured blue laser diodes with low threshold current density, low operation voltage and long lifetimes as well as green laser diode structures with, as Nanowin puts it 'excellent luminescence homogeneity'.

And the company also claims to have fabricated LEDs, based on its GaN

China-based Nanowin is ramping up manufacture of its two inch GaN substrates

wafers, with injection current densities larger than those reported by US-based Soraa and more than 30 times greater than typical GaN-on-sapphire LEDs.

Nanowin has yet to secure any firm contracts with laser diode manufacturers, although as Jianfeng is keen to point out: "We are keeping close contacts with Osram, Nichia, Sony, Panasonic, Soraa for example, as well as new start-up companies in China."

And without a doubt, the company's wafer costs have appeal. Today's two inch GaN wafer, with a dislocation density of between 1 x 10<sup>6</sup> cm<sup>-2</sup> and 1 x 10<sup>7</sup> cm<sup>-2</sup> would set you back some US\$1500 while the cost of a wafer with a lower dislocation density of around 1 x 10<sup>5</sup> cm<sup>-2</sup> rises to around US\$3000.

But as Jianfeng highlights, a Nanowin wafer will cost between US\$1500 to US\$1800, and as he adds: "I think the cost will rapidly reduce with volume production."

Contracts and costs aside, if the company is to makes waves in the worldwide GaN wafer marketplace and rival the likes of Hitachi Cable, Mitsubishi Electric, Sumitomo, Kyma and many, many, more, it will need a water-tight intellectual property portfolio. Jianfeng isn't fazed.

"We already have forty patents in China," he says. "And right now we have several patents pending in the US, Europe and Japan."

**NEWS** ANALYSIS

# M/A-COM

# the future and beyond

Late last year, M/A-COM added BinOptics to its ever-growing line of industry acquisitions. Where next for the high performance semiconductor supplier?

Given its recent BinOptics deal, no matter how you look at it, M/A-COM has set itself up for the future. This, the latest in a steady stream of acquisitions, secures the company a rock solid foothold in a network market, slated for growth, growth and more growth.

Globally, Cisco has predicted that mobile data traffic will grow 11-fold from 2013 to 2018, representing an annual compound growth rate of 61 percent. More data traffic will drive demand for data storage and networks across the board, an opportunity that M/A-COM is set to capitalise on.

"M/A-COM has been a provider of high performance analogue, RF, microwave, millimetre-wave solutions and now we have added photonics as well," says Vivek Rajgarhia, director of strategy. "Our strategy has been to create a portfolio of different semiconductor technologies -CMOS, GaN, SiGe, InP, GaAs and now silicon photonics - so we can pick and choose the right technology for the right application, market and performance parameter."

The first key addition came in 2010, when the then predominantly GaAs semiconductor developer, M/A-COM, acquired high-frequency point-to-point GaAs chipset maker, Mimix Broadband, to bolster its high performance semiconductor offering. Then, in 2011, the company bought Optomai, adding

GaAs and InP-based ICs and modules for 40G and 100G fibre optic networks to its CATV/broadcast and point-topoint/infrastructure businesses.

Following this entry point into the 100G optical space, the company snapped up Mindspeed in 2013, adding more weight to its 100G optical networking products and gaining a firm foothold in SiGe markets. GaN RF semiconductor developer, Nitronex, followed in early 2014, extending M/A-COM's product reach from pulsed avionics to continuous wave applications. And then silicon photonics design company, Photonics Controls, and microelectronics prototyping business, IKE Micro, were scooped up soon afterwards.

The latest acquisition of BinOptics positions M/A-COM strongly as a merchant supplier of InP-based laser diodes in optical communications markets. But, crucially, as Rajgarhia highlights: "This is a transformative acquisition, moving us from purely optoelectronics and into photonics."

With BinOptics, M-A/COM can now flood data centre, mobile backhaul, silicon photonics and access network markets with InP lasers. And factoring in all acquisitions, the company has the key the building blocks to provide 100G and 400G transceivers for high speed datacomms.

"We have been, for example, supplying TIAs, CDRs and modulators, but with BinOptics, we now have the laser chip as well," highlights Rajgarhia. "Photonics Controls provides us with silicon photonics so now we have both transmit and receive functions, and all the key building blocks to enable a 100G transceiver."

"We have essentially consolidated all the high speed semiconductor content in 100G and 400G transceivers and are well positioned from the data centre to the longhaul optical segments," he adds.

#### Business as usual

So what now for BinOptics? Rajgarhia confirms that for the company, it is business as usual. "Their photonics products are completely complementary to our capability and we are expanding capacity."

Indeed, in M-A/COM's recent earnings call, chief executive John Croteau highlighted capacity constraints in data access markets. Given this, he said the company intends to double BinOptics's capacity in six months, quadruple output in a year, and as he added: "[There] is exponential growth potential, and ... revenues could scale accordingly."

Rajgarhia also expects significant demand from silicon photonics markets. "Silicon photonics is the

upcoming field especially in data centres, and we are designing silicon photonics chipsets for 100G and beyond applications."

However, the strategy director doesn't expect the technology to become mainstream in 100G equipment modules for at least two years. "For data centre markets overall we could use silicon photonics, InP or directly modulated lasers," he adds. "And while data centres are definitely a big growth segment, metro and longhaul markets will also see significant growth."

But BinOptics doesn't just boost M-A/COMs photonics offering, it also provides the company with a well established customer base across Asia Pacific. Industry reports claim nearly all of BinOptics's revenue comes from this region, and without a doubt, M-A/COM

MACOM Driver & CDR Photonic Controls **BinOptics** Tx PIC Laser

100G transceiver: With its acquisitions, M-A/COM now offers a one-stop shop for all the key components for their customers to build next generation transceivers.

will, again, capitalise on this fact.

"BinOptics is strong in Asia and we can expect to expand here, as well as into Europe and North America," says Rajgarhia, who will not be drawn on any future acquisitions for M-A/COM:

"We do not want to get into the same space as the Broadcoms. We are in the high perfomance, not the commoditised space, and in plain words I describe our strategy; 'if the product is difficult to make and difficult to sell, then that's the business we are in."

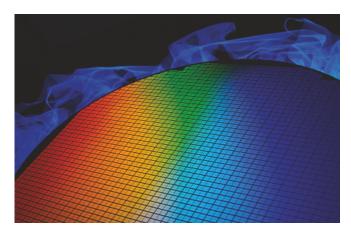

WITH THE VCSEL market poised for rapid growth, semiconductor manufacturers worldwide are ready for action. In March 2014, a pan-European consortium including IQE, Philips and ST Microelectronics unveiled bold plans to get VCSEL fabrication ready for volume production in just three years.

Eight months on, Anadigics has joined the VCSEL race offering VCSEL foundry services and having developed the industry's first 6-inch VCSEL wafer fabrication process. But with production volumes slated for next year, the US-based developer of GaAs semiconductors looks set to lead the pack.

"We have adapted the six inch facility that we've used for our RF processes," says David Cheskis, director of optical

products at Anadigics. "We've produced a lot of VCSEL wafers here, customers are sampling products based on these and we believe we will transition to production volumes in the second half of 2015."

As Cheskis points out, the 6-inch VCSEL line is not a world away from the company's 6-inch analogue GaAs wafer fab that opened fifteen years ago.

"We work off the same baseline processes with etch tools, position tools and metallisations, and many of the processes have been ported over or adapted from our RF process," he explains. "But we have also needed to implement several different processes that are unique to the VCSEL flow."

"For example, an oxidation furnace has been acquired that was not part of the RF process, and we've developed other rather unique proprietary steps that enable us to fabricate the VCSEL on a six inch [line] using the same basic tool set,"

In addition, Cheskis's team has devised a metal contact process, adapted from that used for RF products and also developed unique 6-inch VCSEL on-wafer test capabilities.

The Anadigics director is certain manufacturing VCSELs on 6-inch wafers is going to be crucial to the technology's success. For starters, fabricating VCSELs on the larger GaAs wafers will bring far greater economies of scale than those manufactured within today's three and four inch fabs; cost per square millimetre is lower with more die made per wafer.

And while VCSELs are generally fabricated in a way that may resemble

Left: VCSEL ambition: six inch wafers at Anadigics' manufacturing facility in New Jersey, US.

been very aggressive in implementing a VCSEL process on our six-inch GaAs facility."

What's more, Cheskis is also convinced that his company already achieves better process control in its 6-inch facility compared to a 3- or 4-inch fab.

"The same tools as the six inch toolset are used in eight and twelve inch facilities, so we've got a lot of advanced techniques that we can use to control the processes across the wafer," he says. "We've seen very good yields across the wafer for our process and we're getting these again and again."

And while Cheskis won't be drawn on actual yield or device performance figures, he adds: "Just about any VCSEL that can be made on GaAs is something that we have done here."

#### The right applications

So which mainstream application will VCSELs find first? Faster datacoms, gesture recognition in smartphones and heat sources in industrial processes are just a few of several up and coming applications that will demand the GaAs VCSEL.

Cheskis believes myriad opportunities are out there with VCSEL manufacturers already busy fulfilling orders for optical communications. He also reckons that if VCSELs fabricated on 6-inch wafers can hit a similar cost structure to LEDs, then a VCSEL's better performance will drive significant volumes for the technology in, for example, mobile applications.

However, he is also closely watching gesture recognition in mobile phones and reckons this high volume market will really fuel the move from 3- and 4-inch to 6-inch wafers for VCSELs.

"There are many millions of devices for a mobile application that will consume a lot of wafer realty, and I don't think there is enough capacity in the world with existing VCSEL manufacturers [to fulfil demand for mobile applications]," he says. "But because of the time and investment we've made so far, we're ahead of the game and this is an opportunity for us to capitalise on our core competencies in six inch manufacturing."

"We think VCSELs are going to be big and we're very excited about it," he adds.

LED or CMOS processing, manufacturing is still relatively slow, and at best, takes place on 4-inch wafers where process control can be limited and some production steps are still manual.

As the Anadigics director puts it: "The fabs that people use to make three and four inch wafers are very much like laboratories, but our state-of-the-art GaAs facility runs 24 hours a day, seven days a week with the latest operating systems and tools."

"One thing we've learned along the way is that it's really hard to make this transition from three and four inch to six inch," he adds "But we have a lot of experience with this transition, and we've

Right: A technician tests six inch VCSELs at the Anadigics test facility in New Jersey.

#### **EXECUTIVE VIEW**

# **3**&/-

# Tang Yong Aug

Vice President, Compound Semiconductors, Dow Corning

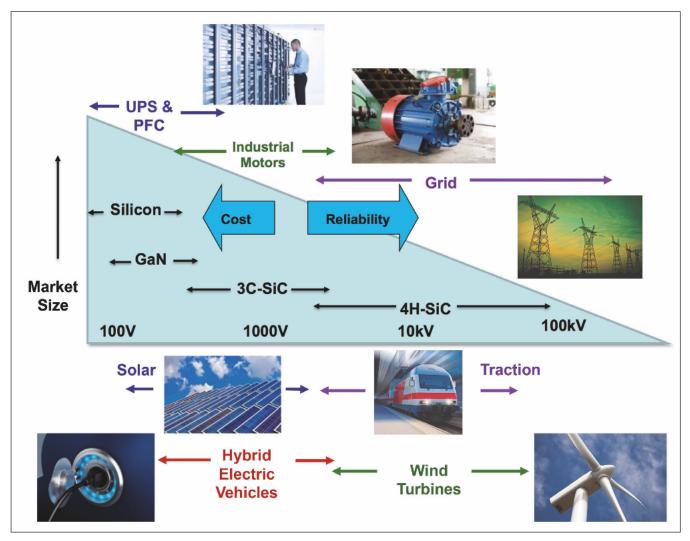

SiC devices have many great attributes, such as high efficiencies, high operating temperatures and the ability to handle high current densities. Why is it, then, that the penetration into a silicondominated market is not that fast?

A The SiC market has steadily grown over the years, but the biggest impediments to this growth are price and reliability. Only lately has the market started to get into MOSFETs, which are the transistors. I believe that this is the next phase of the growth of SiC: More people will get diodes and transistors in their modules, and you will see the price eroding to a price that is more competitive compared to a silicon counterpart.

One of the world's leading SiC substrates makers, Cree, is vertically integrated, and ships SiC devices and modules. Do you think that gives Cree an edge in today's industry?

A I believe that it gives them a big edge. That's not only in economies of scale - I also believe that they have the advantage of device knowledge, to validate the competitiveness as well as the differentiation of silicon carbide. which substrates makers like ourselves and a few of our other competitors may not have.

That is also one of the key reasons why Dow Corning, even though it has done fantastically in 2014, believes that the path going forward for SiC will be through partnership.

Dow Corning is looking for a partner to work with. Can you explain this vision, and why a partner is more than just a valued customer?

The way we look at partnerships is firstly to increase the adoption of SiC in the market. We are definitely not looking for partners who are just start-up companies and who do not have the financial capability. We are looking for partners either to help us be more competitive and complement our skills and competencies in SiC; or we are looking at partnerships in the downstream supply chain who enhance the value of SiC at the product level.

SiC substrates have come a long way, and are no longer riddled with device-killing micro-pipe defects. So why would a device maker consider partnering with you, rather than just buying substrates off the shelf and producing devices in secret?

A I believe that a device maker or product maker who wants differentiation as well as more assurance of their supply chain would want more integration in order to ensure that they are wellpositioned to supply a growing market for SiC devices.

So are you suggesting that there are concerns over SiC substrate shortages in the industry?

Yes, there are two concerns. One concern is in the 6-inch supply. As the market migrates from 4-inch to 6-inch supply to get cost and price competitiveness, I believe that there will

be the need for more 6-inch supply in the market.

The second reason for vertical integration through a partnership is that the current supply from SiC vendors is not an ideal situation. We have in Cree a very big supplier of SiC, and the rest of the suppliers, including Dow Corning, are not as big. And because they are not as big, there are no economies of scale. People who want to really increase the adoption of SiC at the product level want some form of assurance of the supply chain.

Have you started talking to device makers about this partnering opportunity?

A We have been talking to various people, but I think it's early days.

What will happen if you don't get a partner, or you get two or three good offers?

I think a partnership can take many forms. It doesn't just have to be partnerships - it can even be licensing. Obviously, when it comes to licensing, we can have many partners. And a partnership can be in various forms, depending on what stage of the supply chain we are talking about. We could partner with the growers of a crystal, and we could partner in the production of epilayers for SiC. We will see what makes the most sense for Dow Corning, customers and the industry.

With regards to what happens if we don't find a partner, I seriously do not believe that there will be no partners. It's a matter of timing.

# LED Taiwan 2015

Co-located Event

TAIWAN INT'L LIGHTING SHOW

March 25 - 28,2015

TWTC Nangang Exhibition Hall, Taipei, Taiwan

Showcasing LED manufacturing equipment and materials, epi wafers, chips, packaging, modules, and related technologies and solutions

#### **Theme Pavilions:**

- Sapphire & PSS Pavilion

- HB LED Technology Pavilion

- OLED Manufacturing Pavilion

#### **Diverse Activities:**

- LED Executive Summit

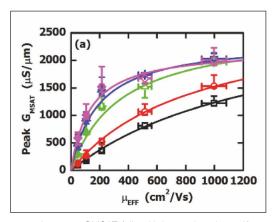

- TechXPOT