Connecting the Compound Semiconductor Community

Volume 22 Issue 6 August/ September 2016

www.compoundsemiconductor.net

**GaN HEMTs** expose pollutants

Optimising the warm-white LED

Getting to grips with thermal droop

Hefty funds for SiC power devices

YOU THINK,

# Gan Power Device Manufacturing Requires hvm solutions.

WE THINK THAT TOO.

THE NEW AIX G5+ C

# DISCOVER THE NEW AIX G5+ C.

Introducing the G5+ C: built on Award Winning Planetary technology for best Single Wafer performance with Batch Reactor benefits – now coming with Cassette to Cassette wafer loading, In-Situ Reactor Cleaning and pre-qualified device processes.

Enabling full automation of your processes and a seamless integration into your Silicon line.

# editorial View

by Dr Richard Stevenson, Editor

# **Droop:** Are we missing the point?

FOR MORE THAN A DECADE the GaN LED community has been ensnared in a debate concerning the origin of droop (it is the mysterious malady that leads to reduction in the efficiency of an LED as the current that passes through this device is cranked up).

To get to the bottom of the cause of droop – and ultimately find a way to make more efficient LEDs that trim the cost of solid-state lighting - many groups have been running carefully designed experiments on these devices. To eliminate the effects of heating, they often involve pulsed measurements, which are carried out on just the blue-emitting chips that pump phosphors to create white-light sources.

The approach of all these researchers is admirable. After all, the scientific method involves understanding how variations in one measurable influence another, so it is beneficial to eradicate

But – and it's a big but – if too much is stripped away, the results will overlook some important issues. That's the case with the LED, with measurements on the blue chip failing to consider two significant contributions to droop in white-light sources.

At Philips Lumileds they have measured droop in various phosphors, finding it to be particularly strong in europiumdoped red nitrides that are preferred for making sources with a high colour-rendering index (see p26).

While droop cannot be eliminated in the phosphor, it can be minimised. Switching to a ceramic form helps, as does the introduction of LED architectures that reduce the light intensity in the phosphor, by distributing it over a larger area.

It might appear that a better way forward is to avoid using phosphors all together, and instead generate white light by colour mixing red, green and blue LEDs. But even with this approach there are two contributions to droop - the well-known efficiency droop, which is particularly severe in green LEDs; and the lesser-known thermal droop.

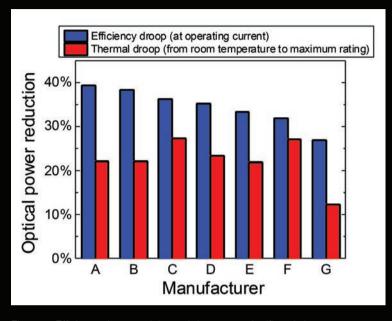

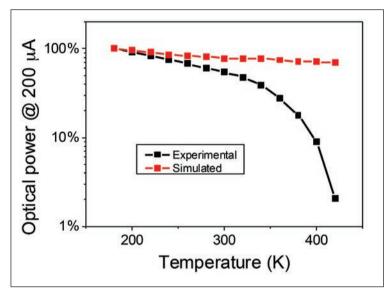

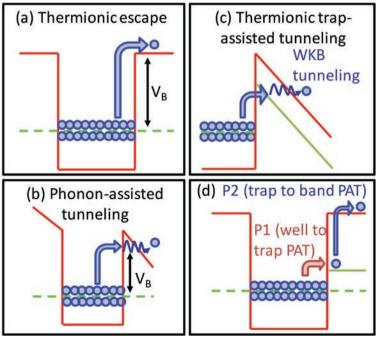

At the University of Padova, in Italy, a team has been studying the latter. A survey has shown its prevalence in green LEDs made by all the major manufacturers, with the reduction in efficiency produced by thermal droop always topping 10 percent. Modelling by these researchers has revealed that this form of droop is due to defect-enhanced carrier escape. which increases with temperature (see p52).

So, droop in real light sources is complex, with contributions coming from the chip, the phosphor and the temperature of the light source.

Editor Richard Stevenson Contributing Editor Rebecca Pool News Editor Christine Evans-Pughe Publisher Jackie Cannon Senior Sales Executive Robin Halder Sales Manager Shehzad Munshi USA Representatives Tom Brun Brun Media

Amy Rogers Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor richardstevenson@angelbc.com +44 (0)1291 629640 editorial@rebeccapool.com chrise-p@dircon.co.uk jackie.cannon@angelbc.com +44 (0)1923 690205

robin.halder@angelbc.com +44 (0)2476 718979 +44 (0)1923 690215 shehzad.munshi@angelbc.com +001 724 539-2404 tbrun@brunmedia.com ijenkins@brunmedia.com +001 724-929-3550 +001 678-714-6775 arogers@brunmedia.com sharon.cowley@angelbc.com +44 (0)1923 690200

mitch.gaynor@angelbc.com

Circulation Director Jan Smoothy jan.smoothy@angelbc.com +44 (0)1923 690200 Chief Operating Officer Stephen Whitehurst stephen.whitehurst@angelbc.com +44 (0)2476 718970 Directors Bill Dunlop Uprichard - CEO, Stephen Whitehurst - COO, Jan Smoothy - CFO, Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal, Jason Holloway.

Published by Angel Business Communications Ltd. Hannay House, 39 Clarendon Road. Watford, Herts WD17 1JA, UK. T: +44 (0)1923 690200 F: +44 (0)1923 690201 E: ask@angelbc.com

Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/€158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2016. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. The 2016 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2016.

+44 (0)1923 690214

# features

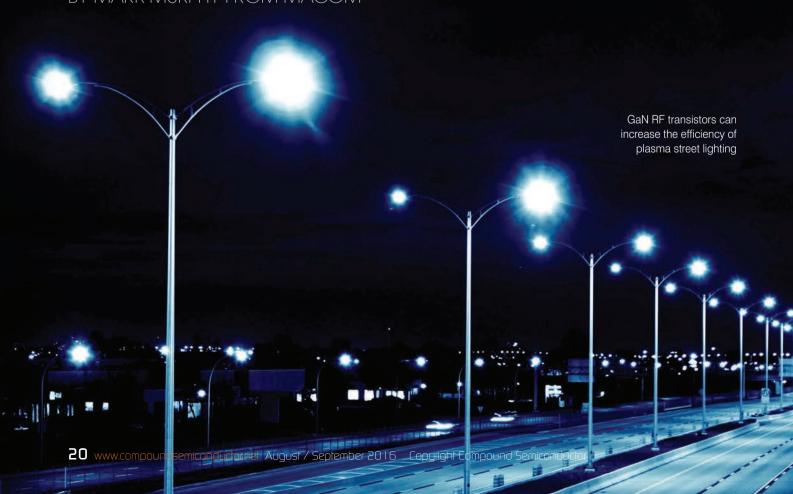

# 20 GaN gets set for mainstream adoption into RF energy markets

Products made from GaAs and LDMOS will be superseded by GaN variants that will penetrate new markets such as heating systems for microwave ovens, power sources for plasma lighting and automotive ignition

# 26 LED droop: The role of the phosphor

Phosphors contribute to droop, but their energy-sapping impact can be minimised through LED design, or by casting them in a ceramic form

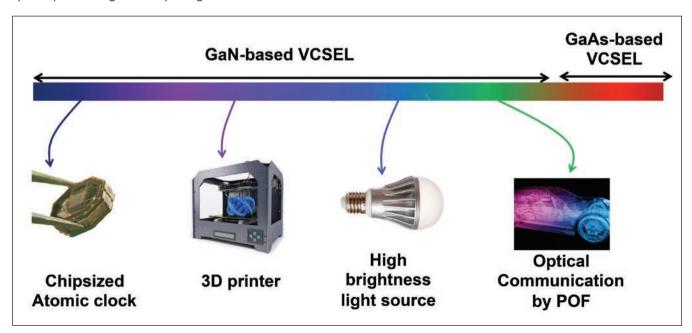

# 30 Getting the GaN VCSEL to market

The output power of the GaN VCSEL hits a new high with the introduction of epitaxial lateral overgrowth

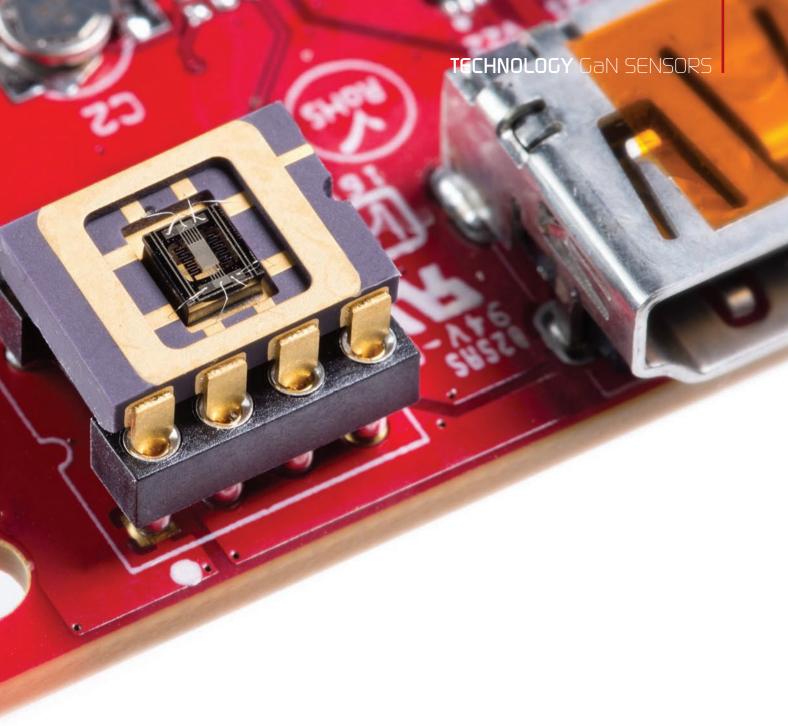

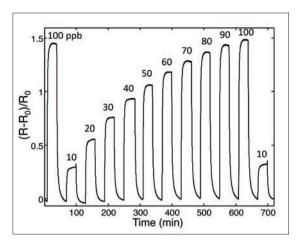

# 36 Exposing pollutants with GaN **HEMTs**

The freestanding GaN HEMT holds the key to an affordable, highly sensitive nitrogen dioxide sensor

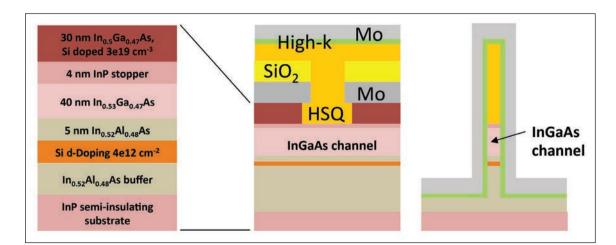

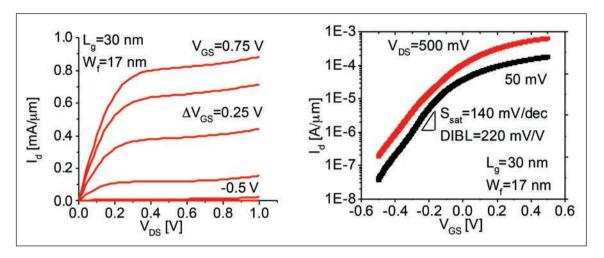

# **42** InGaAs finFETs for future CMOS

Can the InGaAs finFET maintain the march of Moore's Law?

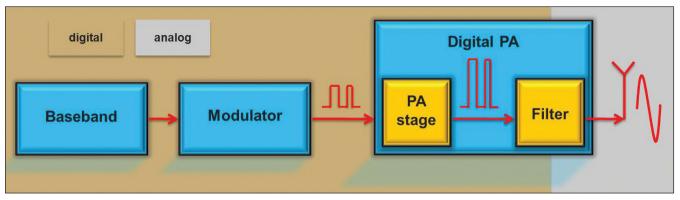

# 48 Advancing wireless with the digital GaN PA

Digital GaN-based power amplifiers can deliver a revolution in wireless communication infrastructure

# 52 Uncovering the origin of thermal droop

At high temperatures LED losses increase due to a rise in defect-enhanced carrier escape

# news

- 06 NSF Awards \$2 million to build SiC-based quantum photonic processors

- 07 POET takes next step towards optoelectronic integration

- 08 Infineon and Wolfspeed who next?

- 09 University of Glasgow joins forces with China to promote optoelectronics

- 11 Consumer-grade LED bulbs used for Comms Links

- 13 Imec sets up Florida branch

# news analysis

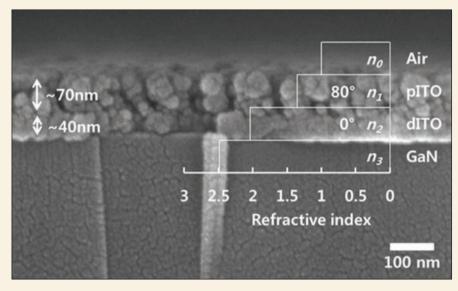

- 14 Ascatron: Hefty funds for high voltage diodes

- 16 Infineon with Wolfspeed: the future

- 18 Metrology: making the most of market growth

# research review

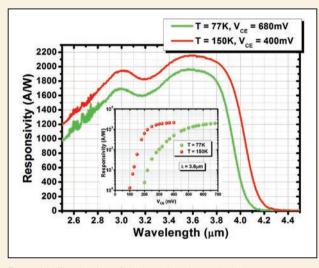

- 56 Phototransistor targets free-space communication

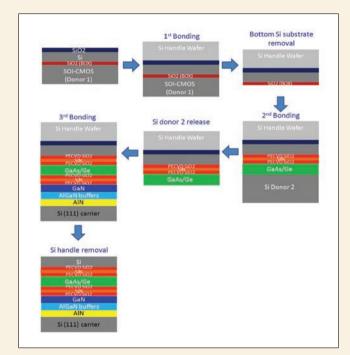

- 57 Integrating nitrides and arsenides with silicon CMOS

- 58 Dual layer ITO boosts LED brightness

# POET takes next step towards optoelectronic integration

POET TECHNOLOGIES, a developer of opto-electronics fabrication processes, says it has taken a significant step toward its goal of developing a fully integrated commercial optoelectronic technology platform.

The step is the first demonstration of functional HFETs down to 250 nm effective gate lengths on the same proprietary epitaxy and using the same integrated process sequence that was previously used to demonstrate high-performance detectors. This milestone is the latest in POET's initiative to integrate a detector, HFET and laser together into a single chip, the three key components of an active optical cable, a current market target for POET.

"Two of the three critical individual pieces of an integrated opto-electronic product are now in place and undergoing their respective optimization cycles," said Subhash Deshmukh, POET's COO. "As reported earlier, we have encountered delays in completing the VCSEL milestone."

According to Deshmukh, the VCSEL continues to be the focus for POET, while the company simultaneously make progress on other aspects of the technology.

"The characterisation that has been done to date on the VCSEL points to required optimisation of a few layers in a very complex and unique epitaxial stack and fine tuning of the resonant cavity mode," said Deshmukh. The new and optimised epitaxial structure is expected to be delivered to the foundry for processing over the next couple of months."

"We have not uncovered any fundamental showstoppers,"added Deshmukh. "We are charting new territory here and as pointed out at the recent town hall meeting and at the annual meeting of shareholders, technical issues are commonly encountered throughout the R&D process and we are systematically understanding and addressing these issues."

POET has already demonstrated electrical functionality of the VCSEL with desired thyristor characteristics and demonstrated lasing modes through optical pumping of the VCSEL cavity (in other words light emission was detected on the epitaxial wafer

However, in order to enable electrical pumping of the VCSEL, the team has had to redesign some aspects of the epitaxial stack. VCSEL functionality was previously verified in a lab setting and the functionality of that original laser has been retested and reconfirmed.

POET's current IP portfolio includes more than 34 patents and 9 pending. Core principles of the company's technology have been in development by Chief Scientist Geoff Taylor and his team at the University of Connecticut for more than 20 years, and are claimed to be now nearing readiness for commercialization opportunities.

# Skyworks introduces IoT switches

SKYWORKS has introduced two new RF switches for the Internet of Things (IoT) applications including the connected

In addition to the connected home, the SKY13587-378LF, which is a pHEMT GaAs SPDT switch, can be used for transmit and receive switching in industrial, lighting and smart energy applications, as well as 802.11a/b/g/n WLAN networks that operate at 2.4 GHz and 5.8 GHz.

The SKY13588-460LF is a CMOS siliconon-insulator SP3T switch made for antenna selection in Wi-Fi applications in IoT systems.

These switches feature an operating temperature range up to 105 °C, making them ideal for applications that require extended temperature. They also have high isolation and low insertion loss which is best for low-power transmit/ receive applications, according to

the company. Their positive voltage control provides low current and optimal efficiency for battery-operated IoT applications and their broadband frequency ranges from 20 MHz to

6.0 GHz (SKY13587-378LF) to 0.1 GHz to 6.0 GHz (SKY13588-460LF).

The devices are available in compact MLPD/QFN packages (6-or 12-pin).

# NSF Awards \$2 million to build SiC-based quantum photonic processors

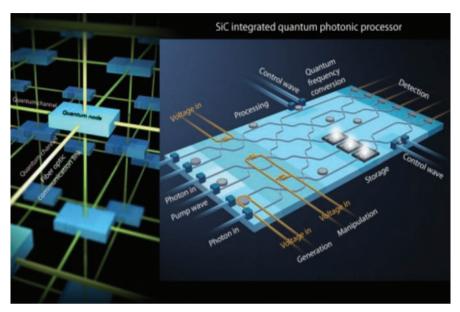

UNDER a four-year, \$2 million US National Science Foundation grant, Rochester University will lead a photonics system integration research project to reduce the complexity and increase the capacity of quantum information processing for secure communication, metrology, sensing, and advanced computing.

"Our team will build chip-scale integrated SiC quantum photonic processors for high-fidelity and energy-efficient quantum information processing, which interface seamlessly with fibre-optic links for secure communication and distribution of quantum information," said Lin, principal investigator of the project and director of the University's Laboratory for Quantum, Nonlinear and Mechanical Photonics.

"We have a very strong, multidisciplinary, multi-university team of experts for this project, coming together in a shared vision," said Lin.

Co-principal investigators are John Howell, professor of physics and optics, David Awschalom of the University of Chicago, Case Western Reserve University's Philip Feng, and MIT's Jurgen Michel - all experts in chipscale integrated SiC quantum photonic processors. Members of the National Institute of Standards and Technology.

Artist's conception of a quantum node lattice with a detailed inset of the SiC integrated photonic processor within one of the quantum nodes

Thomas Gerrits, Sae Woo Nam, and Richard Mirin, are also collaborating on this project.

The research is expected to result in a new class of device technologies with previously inaccessible attributes and merits that may eventually have profound commercial impact on the industrial sectors. SiC combines excellent linear optical, nonlinear optical, point defect. electrical, mechanical, and thermal

characteristics into a single material with mature wafer processing and device fabrication capability, thus representing a promising material system for integrated quantum photonics.

Research such as this also feeds into the work of the AIM Photonics (American Institute for Manufacturing Photonics) consortium of the US Department of Defense, of which the University of Rochester is a partner.

# Infineon and Wolfspeed - who next?

INFINEON TECHNOLOGIES' recent acquisition of Wolfspeed for \$850 million has caused a stir in the compound semiconductor industry.

With very recent mergers of International Rectifier and Infineon Technologies, Fairchild Semiconductor and ON Semiconductor, Wolfspeed and APEI, the power industry is evolving fast. So who will be next?

"At Yole, we see this acquisition as the beginning of a series of impressive collaborations within the SiC power business in the coming years," says Pierric Gueguen, business unit manager at the market research company Yole Développement." And this industry trend is likely to continue and to further increase in the future."

This latest acquisition comes in a power electronics industry where SiC technology benefits are well-known and where business opportunities have been clearly identified by industrial companies. Both Wolfspeed and Infineon Technologies are market leaders and this pact reinforces their dominant market position, according to Yole. The deal also includes the related SiC wafer substrate business for power electronics and RF power electronics.

According Hong Lin, analyst at Yole Développement, Infineon Technologies

market share should increase more than 50 percent if the full acquisition is confirmed.

"Wolfspeed and Infineon Technologies are leaders in the SiC power devices industry. The combination of both players will clearly strengthen the leading position of Infineon Technologies in the SiC power business," explains Lin, Technology and Market Analyst at Yole. "This is a win-win acquisition."

Lin argues that Infineon and Wolfspeed are both established SiC diode players. with the latter having developed a powerful SiC MOSFET solution that is clearly more advanced than that from Infineon. Wolfspeed's Gen 3 has already been commercially available for two years, and it has a good reputation. From its side, Infineon Technologies just released its MOSFET component in May 2016. Within a SiC MOSFET market that

is just taking off, Infineon's acquisition of Wolfspeed ensures its development in this market seament.

In parallel, as number one in the incumbent silicon power business, Infineon Technologies has a wellestablished client portfolio. The German company has a strong understanding of the market's needs, its players, and the technical specifications related to power electronics applications.

The company also has significant experience in power packaging for semiconductors, which is considered the main SiC business bottleneck for power electronics today. Last year, Cree's division, Wolfspeed, acquired APEI to reinforce their packaging capability. Today, with the support from Infineon Technologies, Wolfspeed can further accelerate their product development and reaffirm the leadership of its technology approach.

Finally. Infineon's investment and largescale production capability could support Wolfspeed in ramping up production and

This acquisition includes more than just Wolfspeed's SiC devices for power electronics applications. It also includes the company's activities focused on GaN on SiC for RF applications.

# HexaTech demos high-performance ultraviolet LEDs

HEXATECH has demonstrated its first generation UVSure UV-C LED, based on the company's proprietary AIN substrate

The 263 nm wavelength device achieves 6 mW in a 0.15 mm² active area die. When scaled to its second generation larger footprint, the die is expected to produce approximately 24 mW, which is twice the radiant flux of competitive products. Further, when driven in pulse mode to 300 mA, the same 0.15 mm<sup>2</sup> active area die is able to reach 19 mW, or approximately 76 mW in the large die format.

"This demonstration is a milestone in our business, and is the direct result of intense device R&D coupled with the use of our exclusive high-quality AIN substrate material," stated HexaTech CEO John Goehrke.

He added, "This capability allows us to engage the UV-C LED market at the right moment, linking together incredibly strong interest with cutting-edge performance. It also clearly

demonstrates our continued assertion that the best substrate material yields the best device performance, and this first generation result is just the beginning."

"We are truly excited to be in a position to support the rapidly expanding UV-C LED customer interest seen over the last several years," remarked Gregory Mills, HexaTech's director of business development. "With point-of-use sterilization applications alone representing a \$400 milion plus opportunity in the coming years, we anticipate significant corporate expansion and strategic customer engagement," he noted.

Joseph Smart, director of LED development commented: "HexaTech's world-leading, high-quality bulk AIN substrates are the essential foundation for attaining these results, enabling near perfect epitaxial growth quality throughout the active region of the device, essential to produce both high internal quantum efficiency and long component lifetimes. This is something that competing sapphire substrate technology simply cannot sustain at these wavelengths."

# University of Glasgow joins forces with China to promote optoelectronics

THE UNIVERSITY OF GLASGOW has signed a partnership agreement with a Chinese state-owned enterprise company to develop an international optoelectronics industry base in the Lingang area of Shanghai.

A Memorandum of Understanding was signed earlier this year by the University and senior representatives of the Shanghai Lingang Science and Technology Innovation City Economic Development Co. Ltd - a subsidiary of the Lingang Group which specialises in industrial park development - and the Shanghai Shunmao Information Technology Co., a private company established to manage and commercialise some of the technology which will be developed by this exciting new initiative.

John Marsh, professor of optoelectronic systems and dean of the University of Glasgow-University of Electronic Science and Technology of China Partnership, attended an inaugural event at Lingang representing the University of Glasgow.

The agreement has led to the establishment of the Shanghai Lingang International Photonic Integrated Circuit Joint Laboratory (PIC Lab) which will foster collaboration between the University of Glasgow and its partners in Lingang.

PIC Lab aims to accelerate the development and commercialisation of optoelectronic integrated chip technology, integrating multiple optical components on a single chip and packaging the chips with high-speed electronics, to address the demand for high-speed network connections for the next generation of the Internet. Marsh said: "The University of Glasgow is delighted to be working with our new partners to strengthen international links relating to optoelectronic devices and the development and integration of an optoelectronic integration platform and industry incubation base in Lingang.

We shall also be working to create a Scottish platform. This is international recognition of Glasgow's long term commitment to optical research."

A spokesman for the Shanghai Lingang Science and Technology Innovation City Economic Development Company said the new PIC Lab would capitalise on the combination of domestic and foreign skills and resources to develop "an effective concentration of high-end technical and commercial talent in the field of photonics to deliver a worldleading, cutting-edge technology and industrial capital".

The partnership would also give clear leadership to the global PIC industry and offer a strong impetus to optoelectronic integrated chip technology research and development and attract further domestic and foreign optoelectronic talent technology, added the spokesman.

The Chinese partners plan to visit the University of Glasgow later this year to promote and cement the project.

# Mobile phone LED market to decline between 2015 and 2021

ACCORDING to the latest information from IHS Markit Mobile Phones in Packaged LED Market Brief, the market for LEDs used in mobile phones - including backlighting behind the display, keypad illumination, and camera flash - will decline at a compound annual growth rate (CAGR) of 2.6 percent from 2015 to 2021. Increased penetration of organic LED (OLED) is a primary reason for this decline.

The OLED panel penetration rate for mobile phone displays is forecast to grow from 13 percent in 2015 to 34 percent in 2021, due to strong demand from Chinese brands. LED revenue for backlighting in mobile phones was estimated at \$686 million in 2015, but will decline to \$455 million in 2021.

Nearly all mobile phones shipped in 2015 had at least one camera - and 86 percent also had a secondary camera - although not every camera was equipped with a flash. IHS expects the mobile phone flash LED market to decline slightly in 2016, due to fewer mobile phone shipments.

However, the market will begin to grow again from 2017 to 2020, thanks to increased penetration of colour LEDs and secondary camera flash applications. LEDs used in mobile phone keypads will also decline, but they comprise only a very small part of the market.

Connecting, informing and inspiring the compound semiconductor industry.

# 7<sup>th</sup> CS International Conference SPEAKERS ANNOUNCED!

CS International 2017 will provide timely, comprehensive coverage of every important sector within the compound semiconductor industry.

The 7th CS International conference will be held at the Sheraton Brussels Airport Hotel, in Belgium on Tuesday 7 & Wednesday 8th March 2017.

CS International will build on the success of its predecessors, including the leaders of the world's biggest chipmakers and the most promising start-ups providing 30 presentations spanning 5 key themes.

Together, these talks will detail breakthroughs in device technology; offer insights into the current status and the evolution of compound semiconductor devices; and provide details of advances in tools and processes that will help to drive up fab yields and throughputs. Attendees at this two-day conference will gain an up-to-date overview of the status of the CS industry, and have many opportunities to meet many other key players within this community.

# **Early bird discount**

Book your place before 30.11.2016 and receive a €100 discount.

# FIVE KEY THEMES LIE AT THE HEART OF CS INTERNATIONAL 2017

### Five key themes:

- Refining handset architectures for the 2020's

- Perfecting Power Electronics

- Optimising Light Emitters

- Revolutionising RF Chips

- Exploiting Heterogenous Integration

Within each topic there is a key-note presentation from one of the most influential companies within this sector; one talk by a leading market analyst who will discuss trends within the industry and presentations by the leaders of firms developing cutting-edge technology in this field.

# **Book your place NOW!**

www.cs-international.net/register to secure your place

PLATINUM SPONSORS

**DELEGATE BAG SPONSOR**

PORTFOLIO SPONSOR

**EXHIBITION SPONSOR**

# This two day event covers five themes

## **Refining Handset Architectures for the 2020's**

Will handsets be crammed with ever more III-V content? And could GaN appear in the front-end in the coming years?

### **KEYNOTE**

Stephen Kovacic: Skyworks Solutions

Taking the front-end into the 2020's

## **ANALYST**

Eric Higham: Strategy Analytics

The foundry of the 2020's

### **SPEAKERS**

O Bert Schmitz: Qorvo

David Danzilio: WIN Semiconductors

Meeting customer demands in the 2020s

## **Perfecting Power Electronics**

Can the best devices stem from the ultra-wide bandgap of gallium oxide? Or will they emerge from foundries processing GaN and SiC on silicon?

### **KEYNOTE**

Toshimi Hitora: FLOSFIA

Unleashing the potential of gallium oxide

## **SPEAKERS**

Tamara Baksht: VisIC Technologies

Making the best GaN transistors for power electronics

Frédéric Dupont: Exagan

Driving the GaN Power Device roadmap for large scale adoption

Isik Kizilyalli: US. Department of the Energy Advanced Research Project Agency

Vertical GaN devices for better power supplies

Sujit Banerjee: Monolith Semiconductor

Slashing chip costs with SiC-on-silicon

Anthony Sagneri: FINsix Corporation

Wide bandgap devices: the key to the world's smallest laptop charger

EpiGaN TBC

## **Optimising Light Emitters**

# Sponsored by JSC Technology Park Pulsar

Are colossal LED fabs revolutionising chip manufacture? And what are the big opportunities for visible lasers?

KEYNOTE

Hsu Chen K: Sanan Optoelectronics

Creating the biggest and best LED chipmaker in China

## **ANALYST**

Swapna Prakash

Lighting-up India with LEDs

### **SPEAKERS**

Oleg Shchekin: Philips Lumileds Lighting Co

Non-linear processes in LEDs and engineering for efficiency at high power densities

Martin Behringer: OSRAM Opto Semiconductors

LED - more than just a light emitting cube

Tatsushi Hamaguchi: Sony Corporation Fulfilling the promise of the GaN VCSEL

## **Revolutionising RF Chips**

Will GaN RF deliver the best bang per buck by increases transistor voltages, or making these devices on silicon? And what are the best options for really high frequencies?

### **KEYNOTE**

O John Palmour: Wolfspeed

GaN-on-SiC RF: Poised for Rapid Adoption

### ANALYST

Speaker: Yole Développement

### **SPEAKERS**

Zach Griffith: Teledyne

InP HBTs for high-power 70 to 500 GHz amplification: its status today and where it is going

Rocco Giofrè: University of Rome Tor Vergata

GaN Doherty amplifiers for backhaul radio links

• Michael Ziehl: MACOM

The virtues of GaN-on-silicon

Bernd Heinz: Evatec

TBC

# **Exploiting Heterogenous Integration**

What are the fruits of a marriage between silicon and the III-Vs? And can higher mobility materials improve microprocessors and memory?

### **KEYNOTE**

Daniel Green: Defense Advanced Research Projects Agency – US Agency of Defence

Advancing technology with heterogeneous integration

Soon-Fatt Yoon: Nanyang Technological University

Heterogeneous integration of III-V devices on Silicon with

ultra-thin buffer utilising interfacial misfit dislocations

### **SPEAKERS**

Jesus A Del Alamo: MIT Refining the III-V finFET

Nadine Collaert: imec

Looking for the ultimate low-power switch: the promise of tunnel FETs

Jean Fompeyrine: IBM Advancing SRAM by adding III-Vs (COMPOSE project)

Shengkai Wang: Institute of Microelectronics of Chinese Academy of Sciences

III-Vs and germanium for future logic

Arnaud Furnemont: imec

3D NAND scaling: an opportunity for alternative channel material

# Consumer-grade LED bulbs used for Comms Links

RESEARCHERS at Disney Research and ETH Zurich have demonstrated that consumer-grade LED bulbs can, with some modifications, do double duty both illuminating a room and providing a communications link for devices in that room

This visible light communication (VLC) system would be suitable for connecting the many devices, such as appliances. wearable devices, sensors, toys and utilities, that could comprise the Internet of Things, or IoT, said Stefan Schmid, a researcher at Disney Research and ETH Zurich.

By having individual LEDs alternate between sending modulated light signals and serving as receivers of signals, it is possible to create a network of bulbs that can send messages to each other and connect to devices, while having no discernible effect on room lighting. Schmid and his colleagues shared details of the system they designed, called EnLighting, at the IEEE International Conference on Sensing, Communication and Networking (SECON) 2016 in London.

"Interconnecting appliances, sensors and a wide variety of devices into the Internet of Things has many potential benefits, but using radio links to do so threatens to make the radio spectrum an even scarcer resource," said Markus Gross, vice president at Disney Research. "Visible light communication networks conserve the radio spectrum, while also making it difficult to eavesdrop for anyone out of line of sight of the network."

"LED light bulbs mounted on the ceiling or in free-standing floor lamps easily cover a room, serving as illumination while at the same time creating a roomarea network that allows data exchange between light-emitting devices," he said. Even if the bulb is not needed for lighting and is switched off, it can still serve as a receiver of signals from those devices, he added.

"We used commercially available, offthe-shelf LED light bulbs as our starting point," Schmid said. "They are readily available at low cost and can be used in any lamp with standard sockets. This leads to an easy-to-setup and flexible testbed that can be readily duplicated."

The bulbs were modified, however. A System-on-a-Chip, or SoC, running an embedded version of Linux was added to each bulb, as well as photodiodes to enhance sensing of incoming signals and an additional power supply for the added electronics.

The researchers deployed four such bulbs for their proof-of-concept system. They showed that their system architecture and protocols enabled the bulbs to create stable networks that could support the low bandwidth applications typical of most IoT devices.

They also showed it was possible to use the system to estimate the position of devices in the room, an example of the additional applications that the system could support.

# Cree expands into new high bay applications

CREE has introduced the HXB Series LED High Bay Luminaire, said to be the first of its kind to operate in extreme ambient temperatures spanning -40 °C to +65 °C and delivering 70,000 lumens at up to 140 lm/W.

The luminaire can be mounted at heights of 30 feet and higher, and comes with optical options including flood and aisle distributions. The HXB High Bay Series brings Cree technology to new applications such as cold-storage spaces with sub-zero temperatures and high-heat climates like warehouses and airplane hangars.

«Cree continues to provide better light experiences by delivering on the true potential of LED technology,» said David Elien, Cree senior vice president, lighting. "The HXB Series redefines the high-bay category with extraordinary rated lifetimes and industry-leading lumens per watt even in extreme operating temperatures that are found in distribution centres, gymnasiums and field house applications."

The HXB Series withstands freezing cold and severe heat, all at less than half

the weight and double the warranty of competing LED high-bay fixtures. It is engineered for performance today and for 100,000 hours of use, with a virtually maintenance-free design, zero restrike time and lightweight construction, says

An aluminium bonded zipper fin heat sink provides thermal management for long lifetime and exceptional efficacy in extreme operating temperatures. With less material than cast aluminum heat sinks, the HXB Series is said to be half the weight of competing luminaires, for easier installation.

The series is available with 35,000 lm and 70,000 lm output options of exceptional illumination performance, offering onefor-one replacement of 500 W and 1000W HID luminaires at colour temps of 3500K, 4000K or 5000K at up to and beyond 80 CRI.

# Imec sets up Florida branch

IMEC, the Belgian research centre, will be opening Imec Florida, a new entity focusing on photonics and high-speed electronics IC design based in Osceola, Florida.

Imec Florida kicked off with the signing of a collaboration agreement with the University of Central Florida (UCF), Osceola County and the International Consortium for Advanced Manufacturing Research (ICAMR), that is setting up fab facilities for the development and production of innovative III-V-onsilicon solutions for a broad range of applications including sensors, highspeed electronics and photonics.

Imec Florida will be established as a design centre facilitating the collaboration between Imec's headquarters, based in Leuven, Belgium, and US-based semiconductor and system companies, universities, and research institutes. Imec Florida's initial focus will be the R&D of high speed electronics and photonics solutions, starting with an offering of IC design research for a broad set of semiconductor-based solutions such as THz and LIDAR sensors. imagers, and a broad range of sensors. It will also provide IC design needs that will be driving the ICAMR manufacturing research.

Through Imec Florida, Imec's design, prototyping and low-volume production service - also named Imec IC-link - will provide the US market low-cost access to advanced foundry services, helping entrepreneurs to (industry and academia) design innovative products and get them to market.

Funding for Imec Florida will come from Osceola County, and the University of Central Florida. The aim is for the new centre to attract top talent through future strategic partnerships, with the aim to employ about ten scientists and engineers by the end of the year and increase to 100 researchers in the next five years. Heading up the facility as general manager will be Imec's VP Bert Gyselinckx who previously served as general manager at Imec in Eindhoven. the Netherlands and helped to coinvent many technologies deployed by innovative semiconductor and consumer electronics companies.

"As the US semiconductor market continues to strengthen with semiconductor manufacturing, equipment, materials and system innovation, we are extremely pleased to collaborate with partner organisations in Florida and see Osceola County in the Orlando region as an interesting location to drive the next phase of Imec's growth and innovation," stated Luc Van den hove, president and CEO of Imec. "Together with industrial and academic partners, we want to develop sustainable solutions and technology to accelerate innovation and stimulate economic growth within Osceola County and the State of Florida."

"Imec's international prestige gives us the opportunity to leverage its standing in a field that is growing exponentially in order

to recruit more partners and funding for our work at the new Design Centre and the Florida Advanced Manufacturing Research Centre," said Osceola County Commission Chairwoman Viviana Janer.

"The relationships and people that Imec brings to our operation are tangible ways that Osceola County's 5-year, \$15 million investment will be more than re-paid. It's important to realise that the new Design Centre is going to capture the attention of everyone in this field, thereby ensuring maximum utilisation and value of the FAMRC."

"The Imec Design Center is the funnel that will fill ICAMR with high-value manufacturing opportunities and we will work closely with them to make sure our capabilities tightly align with their technology direction, said ICAMR CEO Chester Kennedy.

"This partnership is poised to shine the global high-tech spotlight on Central Florida."

# **Advanced Compound Semiconductor Foundry Services**

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and defense industries.

MasimoSemiconductor.com | 603-595-8900

# ASCATRON:

# HEFTY FUNDS FOR HIGH VOLTAGE DIODES

Following a €4 million investment, SiC power device developer Ascatron intends to deliver very high voltage diodes to market in a year. Chief executive, Christian Vieider, reveals plans to Rebecca Pool.

EARLIER THIS SUMMER, Sweden-based SiC power semiconductor developer Ascatron revealed that it had raised a hefty €4 million in financing from investors in Italy and China, as well as reactor supplier, LPE, Italy.

Now intending to complete development of its initial SiC devices - the first of which will be a high voltage SiC diode the company will split funds between materials production and product development.

As Ascatron chief technology officer, Adolf Schöner, said at the time: "Forty percent of the market for power electronic components is in China and we see a lot of interest in SiC for energy saving."

"We've already started to implement our advanced material technology in production equipment for SiC epitaxy," he adds. "The next step is to optimise device design and outsource the remaining manufacture of the chip to a foundry with capacity for volume production."

### **Burying** issues

From the late 1990s, researchers at Swedish research institute, Acreo, had been developing SiC epitaxy, spinning out Ascatron in 2011. During this time, Acreo had offered SiC epitaxy as a service, providing multi-layer structures and re-growth on nonplanar surfaces.

At the same time, development of SiC device concepts, including a normally-off SiC JFET rated to 1.2 kV and 50 A, was well underway. And collaborations with HOYA, Japan, had led to a 3C-SiC process for power MOSFETs.

Fast-forward to today and progress has clearly continued. Ascatron has developed many processes for manufacturing SiC semiconductors for power electronics, including substrate buffers, SiC epitaxy, deep trench etching and more.

At the heart of these breakthroughs lies so-called 3D-SiC technology, based on embedded epitaxial growth methods that replace the conventional process of doping with ion implantation during SiC device fabrication. When fabricating SiC devices, doping via ion implantation can bring problems. Ion

diffusion is slow, preventing healing of defects, and inhibiting current density and high-voltage performance. And in a separate issue, electric fields at Schottky contacts and MOS interfaces also stymy device performance.

To side-step these issues, Ascatron epitaxially grows doped material within etched 3D structures, such as trenches, producing high-performance, high-voltage SiC devices. For example, when fabricating a Schottky diode, a p-type grid is first fabricated on the substrate surface, via trench etching.

Epitaxial re-growth and planarisation is then applied to fill up the trenches with p-type material. And, in a final step, the grid is buried by another re-growth step of a thin *n*-layer.

Crucially electric fields at field-sensitive areas of the device are reduced. high electric fields are shifted into the SiC bulk and ion doping implantation damage simply doesn't exist.

As Ascatron's managing director, Christian Vieider says: "We've been working on this technology to make very efficient doping structures which replace ion implantation with epitaxy."

Right: Ascatron is heading for high-voltage markets with its epitaxy expertise.

"Losses are much lower in our devices and we can design [structures] to handle very high voltages in an efficient way," he adds.

So with the process honed and cash in hand. Ascatron is currently working with pilot customers and intends to deliver its first device - a high-voltage, buried-grid SiC Schottky diode for industrial process markets - in a year.

"We're targeting high-voltage applications - 10 kV devices - for industrial processing as we see some specific needs that we think we can fulfill," says Vieider. "We've identified that IGBT [modules] are available up to 6.5 kV, but above this there are no real switching power devices, so we think this is a good place to start our product range."

But how exactly will Ascatron compete with the likes of Infineon. Cree. ST Microelectronics and Rohm? Vieider reckons his company's technology can provide advantages at the higher voltages that competitors' devices haven't yet reached.

"We already have a customer that is looking for high-voltage devices, but just can't find a device," he adds. "Silicon devices can be coupled together in series perhaps, but right now there is really nothing on the market, so this is where we are starting."

And with higher-voltage devices in place, the company will then look to broadening applications to lower voltages. Indeed, Ascatron recently bought shares in Italy-based start-up, PileGrowth Technology, to develop MOSFETs based on cubic SiC grown on silicon.

The move could open up markets for 300 V to 600 V applications and also allow Ascatron to compete with rival technologies, including GaNon-silicon.

> "We had a choice and could have targeted lower voltages from the beginning, but there are already competitors in this market," says Vieider. "So once our technology has been adopted at the higher voltages, then we will move to lower voltage applications."

> > To kick-start its journey to commercial devices, the

company recently bought a single-wafer, 6-inch production reactor system. manufactured by investor LPE. Past development has centred around several reactor systems, including two prototype 4-inch Aixtron hot-wall CVD reactors, initially pioneered by Sweden-based SiC CVD reactor supplier, Epigress.

According to Vieider, the systems were flexible and produced good material quality, but turnaround times weren't fast enough, so a production upgrade was critical. "We're now ready to scale up our fabrication processes for production." he says. "Our latest reactor has load lock, a good turnaround time and very short cooling times".

"We need to do very thick epitaxy - from 0.1 micron to 100 micron - and have an epitaxy process for advanced grid doping," he adds. "This system produces [structures] with good doping, uniformity and performance."

Past company plans had included the purchase of a multi-wafer reactor system, but Vieider reckons his team will get better material quality with a single-wafer system.

"In principle you can buy three single-wafer reactors for one multi-wafer reactor," he explains. "So, as our needs arise we can add more reactors to production."

The company currently buys in substrates from commercial suppliers, and going forward, will keep fundamental epitaxy processes in-house while outsourcing remaining production to a commercial foundry.

"In two years we will have a product on the market and will target more and more applications from higher to lower voltages, addressing broader and broader markets," says Vieider, "Beyond this, our target is to be a supplier of SiC power devices for broad applications."

# INFINEON WITH WOLFSPEED: THE FUTURE

What does a stronger Infineon mean for power and RF markets, asks Rebecca pool

IN A MOVE to raise resources and become a more focused LED lighting company, Cree has sold its power and RF arm, Wolfspeed, to Infineon for \$850 million in cash.

In the words of Cree chief executive, Chuck Swoboda: "This [decision] unlocks value, increases management focus and supports our mission to build a more valuable LED lighting technology company." But for Infineon, the move could mean so much more.

While the Germany-based semiconductor vendor is already the power market leader, acquiring Wolfspeed's SiCbased product portfolio, strengthens its dominance even further.

For years, the company has focused on high performance SiC JFETs, only delivering its first SiC MOSFET earlier this year following customer demand. But acquiring Wolfspeed provides instant access to MOSFET production that can be introduced to company fabs around the world.

As Richard Eden, senior analyst of power semiconductors at IHS Technology, highlights: "It's taken Infineon a few years to realise that end users are more comfortable with MOSFETs, but this acquisition speeds up the introduction of Infineon SiC MOSFETs."

"The SiC MOSFET market has been dominated by Cree/Wolfspeed and Rohm, so Rohm will be feeling the pressure by now," he adds. Meanwhile, the acquisition also strengthens Infineon's RF power presence. The company already has a strong silicon-LDMOS offering and is developing GaN-on-silicon products. But now it also has access to Wolfspeed's GaN-on-SiC products.

Each technology is critical to nextgeneration cellular communications, from high-end LTE and 4.5G to 5G, but GaN-on-SiC will now allow Infineon to deliver products for 80 GHz frequency, 5G applications of 2020 and beyond.

Indeed, Infineon chief executive, Reinhard Ploss, has said that Wolfspeed will help his company's target of leading the entire RF market. However, the latest deal will also extend Infineon's reach into high growth sectors, including IoT infrastructure, renewable generation and electric vehicles.

"For example, electric vehicle and charging station development is massive

Below: Reinhard Ploss, CEO of Infineon Technologies, and Chuck Swoboda, Cree Chairman and CEO (right).

in China with DC-to-DC conversion of battery charging and plug-in station markets moving rapidly," highlights Eden. "This is a big growth sector for SiC due to its efficiency benefits over silicon, and Infineon would now like to use Wolfspeed products to build the strength and position of its sales network across China."

But MOSFETs and RF markets aside, the latest deal provides one final, over-riding advantage; Infineon now owns Cree's SiC wafer substrate business for power and RF applications.

Wolfspeed had been a leading market supplier of wafers on which to manufacture SiC devices. But as Eden points out: "Infineon is now vertically integrated and can offer everything in house. It can make the wafers, process the wafers in its own fabs, and make the modules from the devices that have been formed on its wafers."

Infineon's Ploss has stated that Wolfspeed will continue to supply wafers to third parties in, say, mobile network base station markets. But in-house wafer production will likely lead to Infineon's device prices falling.

"This applies to MOSFETs but Infineon's existing range of diodes could also probably become cheaper as the company will get wafers at cost rather than sourcing them from a commercial third party supplier," says Eden.

Cost aside, Infineon's vertical integration could also have ramifications on power and RF markets around the world. According to Eden, silicon vendors have developed SiC and GaN power devices to defend market positions, while companies such as GaN Systems, Cree, EPC and Transphorm have delivered devices to disrupt the silicon supply chain.

"By buying Wolfspeed, Infineon is firmly positioning itself for the future," says Eden. "It's not just defending sales, its looking forward to expanding GaN and SiC sales; to try and push the market ahead like this is a very forward view."

So, with the acquisition scheduled for completion by the end of this financial year, what next?

For power markets, better quality devices could be on the cards. Eden's sources tell him that SiC MOSFETs from General Electric are more reliable and can switch at higher currents than offerings from Wolfspeed and Rohm. "Infineon will know what to do to enhance these MOSFETs from the Wolfspeed acquisition," he says.

And eventually, industry can expect Wolfspeed to be fully integrated to Infineon. The company acquired International Rectifier in early 2015, and has since maintained the company's established brand. But for the shorterlived Wolfspeed, integration is expected to be cheaper and easier. Ploss has been reluctant to provide detail on the acquisition process, but has publicly stated the company is aiming for complete integration in the long-term.

"I hadn't seen this acquisition coming, but when you think about it, it's not surprising," concludes Eden. "Infineon has the money, it's now removed the competition from the market and it's strengthened its product range, so why not?

# **METROLOGY:**

# MAKING THE MOST OF MARKET GROWTH

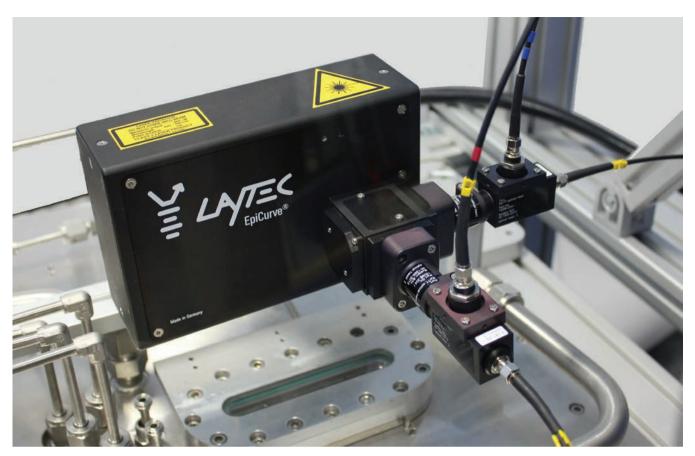

As III-V markets gather momentum, LayTec is chasing the opportunities, reports Rebecca Pool.

IN LATE JUNE Berlin-based instrumentation supplier, LayTec, announced its first order for its in-situ metrology tool, EpiTT/VCSEL.

Designed for VCSEL applications, the tool measures wafer temperature and growth rate of epitaxy layers during MOCVD, but also monitors the spectral reflectance of the evolving distributed Bragg reflectors and cavity structures. As chief technology officer, Kolja Haberland, highlights: "We look at the spectroscopic position of the stop-band and see if there is any mis-matching between the cavity and Bragg reflectors."

"Mirrors, for example, have to reflect at the same wavelength and even with a mismatch of only a couple of nanometres, device performance will suffer," he adds. "We are trying to bring new tools into the market that serve customer needs, and we see great growth potential in the VCSEL market."

The company's first in-situ product, so-called EpiRAS, monitored epitaxial growth of cubic semiconductors. Primarily a research tool, the system is still used by many academic organisations to provide data on wafer temperature, growth rate, composition, doping levels and more. But while it has infiltrated myriad research organisations, the leap to industry didn't quite happen.

"This is a very valuable tool and measures so many parameters on the wafer surface, but it has been just too

complex," says Haberland. "Also it only works with cubic materials, such as arsenides and phosphides, so for example, we can't access the nitride market with this tool."

Given this, the last few years have been a hive of activity for LayTec, with the company developing tools, largely for use with Aixtron reactors, to take advantange of growing III-V markets.

For example, EpiTT described as the 'workhorse of mass production', has predominantly targeted industry production of GaAs and InP laser diodes. edge-emitting lasers and VCSELs. The tool measures temperature and reflectance at three wavelengths and can be supplemented with 'EpiCurve' to detect wafer bow.

Meanwhile, the company, also keen to glean business from GaN LED and laser diode markets, developed 'Pyro400' to measure surface temperature during the epitaxial growth of GaN on sapphire or SiC.

As Haberland highlights, such tools have proven crucial to manufacturers in these markets as well as developers of InP and GaAs RF devices, but in October 2015, LayTec upped its game by introducing a new generation of these tools. Described as being more customisable, crucially, the latest 'Gen3' tools can be used beyond Aixtron reactors.

"These standalone products fit into

virtually any brand of MOCVD system," says Haberland. "So we're not just talking about the Aixtron R6 and Aixtron Planetary, these can also be used with the Veeco K 700 and Taiyo Nippon Sanso UR 25K, in smaller research systems or retrofits from, say, SMI and Agnitron, as well as in a variety of plasma-based etching and deposition systems."

The move follows the integration of LayTec's OEM metrology tools to Aixtron's systems just over a year ago. Then, in June this year, Aixtron qualified LayTec's Gen 3 software so users can also access the latest metrology tools on its MOCVD platform.

But be it integrated or standalone, the growing demand for in-situ metrology is all good news for LayTec, and as Haberland says: "These developments are bringing us deeper into more markets."

# Market developments

Clearly, LayTec is intent on capturing business as III-V markets grow. The recent delivery of the VCSEL-specific metrology tool follows customer demand to monitor progress of VCSEL growth during the many hours of deposition of the III-V materials.

As Haberland says: "If in-situ data indicates that growth isn't on track, the user can implement a control loop to bring growth back on track and optimise yield and throughput."

And as VCSEL markets grow, LayTec has

As III-V markets grow, LayTec is delivering more in-situ metrology tools

also spotted a second market to focus efforts on; the UV-LED market.

"Again we see good growth here," says Haberland. "UV-LEDs are grown on different materials. AIN. AIN buffers or AlGaN buffers with a high aluminium content, so straightforward temperature measurement will not work. We are bringing a specialised version of the tool, as we did with the EpiTT VCSEL, for UV-LEDs to the market."

Looking to the future, LayTec is expecting growing demand from Taiwan and China as, for example, LED manufacturers turn to the latest generation of Pyro400 to monitor epitaxial growth. Global LED players have already adopted the tool but according to Haberland: "[Asia-based manufacturers] are catching up and will integrate these tools to their control loops to bring more value to mass production."

The company also recently revealed that epiwafer manufacturer, IQE, has equipped its fab with LayTec Gen3 metrology systems for MOCVD process

monitoring. The move is just one of several partnerships that LayTec has forged with foundries, which Haberland sees as all being crucial to the company's future.

"These foundries run on many tools and have a huge variety of growth processes for different customers, products wafer sizes and materials," he says. "Calibration is so important here, so in-situ metrology makes sense."

Still, for LayTec, there is much more

beyond MOCVD. "Our market studies look at the number of MOCVD tools sold in different markets and there is a lot of growth predicted for UV LEDs, GaN-onsilicon power devices, with GaAs and InP markets remaining steady," says Haberland.

"But we see ourselves also reaching broader markets, and these will include plasma-enhanced CVD, ALD and MBE of lots of materials from pure silicon and SiGe to III-V-on-silicon and CMOS integration." he adds.

# **VENDOR VIEW** GaN RF

A NARROW SUBSET of semiconductor technologies has always serviced the RF and microwave domain. This approach allows the most appropriate technology to meet the unique requirements of a host of complex applications, ranging from consumer wireless handsets to military radar infrastructure.

As with any technology, different candidates must be assessed in terms of performance, reliability and cost. Do this, and it is clear that there is an absence of a one-size-fits-all solution for adequately addressing the needs of every RF application. Instead, a spectrum of semiconductor solutions has evolved for meeting specific technology challenges while fulfilling cost requirements.

Two of the most established technologies for serving

many commercial applications are GaAs and silicon LDMOS. But they are now under threat from a new challenger, GaN, that is poised to deliver a ground-breaking transformation. Products based on this wide bandgap semiconductor are now commercially available from several companies, including ourselves – MACOM of Lowell, MA.

To fully appreciate this wide bandgap technology, and its supply chain dynamics that are propelling its industrial uptake, it is helpful to consider the evolution of GaAs from an esoteric technology to high-volume market mainstay – a trajectory that parallels what we are seeing with GaN.

And in addition, it is worthwhile to consider the role that LDMOS has played in the evolving RF market.

# GaN gets set for mainstream adoption into RF energy markets

Products made from GaAs and LDMOS will be superseded by GaN variants that will penetrate new markets such as heating systems for microwave ovens, power sources for plasma lighting and automotive ignition

BY MARK MURPHY FROM MACOM

# **VENDOR VIEW GAN RE**

Back in the 1990s, GaAs was in a formative stage, similar to where GaN has been positioned in recent times. It was an emerging technology, underpinned by strong government funding and targeting applications that could pay a premium for high performance.

This state of affairs turned on its head with an explosion in demand for wireless handsets. GaAs had found its 'killer application', and economies of scale were soon at play. Compound semiconductor companies drove the industry towards establishing robust, reliable and scalable GaAs supply chains, through investment of hundreds of millions of dollars in large-scale GaAs fabs. Thanks to this, GaAs chip manufacture shifted from boutique production to highvolume production in just a few years.

Now. GaAs is under threat from silicon-based technologies such as CMOS and SOI, which are both gaining market share in handsets. Several leading silicon industry vendors have announced initiatives to supplant most GaAs production, leveraging economies of scale that dwarf even the largest GaAs factories.

Like GaAs, LDMOS has undergone incremental growth and multi-decade longevity in the RF market, particularly in wireless infrastructure. Thanks to the maturity of the LDMOS supply chain and attendant manufacturing efficiencies, costs have been kept relatively low.

Up until very recently, the performance of GaAs and LDMOS products - evaluated in terms of power, efficiency, bandwidth and thermal stability - have been sufficient for their target applications. But both technologies have their flaws. GaAs is limited to a power output below 50 W, while LDMOS is incapable of operating above 3 GHz.

GaN compares extremely favourably to both incumbents, combining high output powers with a very wide frequency range. It also offers several other attractive attributes, but despite all its virtues, it has been held back by high prices. Devices can be as much as ten times more expensive than products based on GaAs or LDMOS.

## GaN at the tipping point

Today, the performance advantages of GaN are well known to everyone involved in the RF and microwave industry. This wide bandgap semiconductor delivers a raw power density that is considerably higher than that of GaAs and LDMOS, and devices can be scaled to high frequency. Armed with these attributes, device designers can realise broad bandwidths while maintaining high efficiency.

Our team at MACOM has been developing and commercialising GaN technologies and devices for several years. Our latest technology, fourth generation GaN-on-silicon (Gen4 GaN), can be used to manufacture products that combine a peak efficiency in excess of 70 percent with a gain of 19 dB, for modulated 2.7 GHz signals. This level of efficiency exceeds that of LDMOS by more than 10 percentage

The high power densities and great efficiencies of GaN make it a great source for RF basestation transmitters.

points, and if properly exploited, it can have a tremendous impact at the system level in military, commercial and industrial applications.

Historically, the sticking point for GaN has been its high price. But this should change, given the very high power densities and scalability to 8-inch substrates. With our Gen4 GaN, we are planning to produce GaN-based devices in volume production levels that undercut the cost per watt of comparable LDMOS products, and are significantly less than that of GaN-on-SiC variants, which are far more expensive. Working with partners, we are leaders of 6-inch silicon wafer production, and we intend to move to 8-inch production in 2017. The growing capacities, allied to lower cost structures, should break barriers to widespread GaN adoption in mainstream commercial markets.

Delivering GaN performance at a cost that's far closer to that of silicon will drive innovation within the RF domain and ultimately open massive market opportunities. Chief among them will be RF energy applications. Here, controlled electromagnetic radiation will heat items and drive all kinds of processes. Today, magnetron tubes tend to generate this energy, but they are set to be displaced by an all solid-state RF semiconductor chain.

There are several compelling reasons behind a switch to solid-state RF energy. They include a low-voltage drive, semiconductor-type reliability, a smaller form factor, and an 'all-solid-state electronics' footprint. But perhaps the greatest attributes are fast frequency, phase and power-agility, and hyper-precision. Taken

# **VENDOR VIEW** GaN RF

Benefits of switching the RF source in a microwave oven from a magnetron to a GaN RF unit include a longer system life, a constant output power and zone controllable heating.

together, these strengths result in an unprecedented process control range, even energy distribution, and fast adaption to changing load conditions.

# Microwaves and lighting

One common consumer product that will be transformed by the arrival of Gen4 GaN is the microwave oven. Prototype magnetron replacements have already been produced using LDMOS technology, but they fall significantly short of the minimum performance level. Our GaN devices bridge that gap, providing an additional 10 percent efficiency. HEMTs can deliver 70 percent efficiency at 2.45 GHz, and do so at a cost that is competitive with a tubebased legacy technology that launched in the 1940s and has undergone manufacturing optimization over many decades. The strengths of GaN ensure a longer system life, constant output power and zonecontrollable heating.

Another sector that will be transformed by the arrival of affordable, high-performance GaN products is plasma lighting. It is slowly making inroads in the

overall lighting market, with the greatest success coming in grow lighting applications. Here it makes an ideal lighting source, thanks to a colour-rendering index that provides a very close match to that of natural sunlight.

Today, LDMOS technology is widely used to provide RF power excitation at frequencies of hundreds of megahertz. However, developments are underway to increase the frequencies of RF excitation towards 6 GHz. This must be accompanied by efficiencies in excess of 70 percent – requirements that are very tough to meet with LDMOS technology, but a given for GaN. Turning to this wide bandgap technology also enables a trimming of transistor dimensions. This helps the vendors of plasma lighting produce competitive products that will battle with LED lighting for the indoor light bulb replacement market.

Further opportunities for GaN exist in automotive ignition, heating and drying, and industrial, scientific and medical markets. In all these, the strengths of GaN make it a highly compelling alternative to LDMOS. In conventional vehicles, RF-based ignition systems are poised to replace spark plug technology. Channelling RF energy into a vehicle's combustion chamber provides a more even ignition distribution. and in turn produces a considerable boost in fuel efficiency and a cut in carbon dioxide emissions. When it comes to heating and drving, using RF energy enables uniform heating and drying of materials. Undesirable temperature gradients resulting from conventional approaches are then avoided - these can be particularly severe in materials with poor heat transfer characteristics. Benefits that follow include accelerated production processes for manufacturing applications, improved medical procedures and processes that involve blood and/or organ warming, and enhanced chemical processing techniques in scientific applications.

# Massive markets

The total addressable market for RF energy applications is enormous. Just consider the microwave oven market, where annual sales exceed 70 million units, each of which requires a transmit power ranging from 0.6-1.5 kW. That equates to a

Today, LDMOS technology is widely used to provide RF power excitation at frequencies of hundreds of megahertz. However, developments are underway to increase the frequencies of RF excitation towards 6 GHz. This must be accompanied by efficiencies in excess of 70 percent - requirements that are very tough to meet with LDMOS technology, but a given for GaN

# **Advancing** Materials Characterization

Lake Shore offers precision platforms for research into a wide variety of materials

# THz Material Characterization System

Ideal for: ZnO & other semiconductor materials • thin films • superconducting metamaterials • 2D materials • complex oxide systems

# Hall Effect Measurement Systems

Ideal for: III-V, II-VI, & elemental semiconductors • metal oxides • complex oxide systems • ZnO & other transparent conducting oxides

# **Cryogenic Probe Stations**

**Ideal for:** GaN & other wide-bandgap devices • MEMS • transition metal dichalcogenide & 2D material transistors • CNT & nanowire devices • piezo & ferroelectric materials

# **VENDOR VIEW** GaN RF

MACOM's MAGe-102425-300 total power demand of can deliver a 300 W 42 GW to 105 GW. At current mainstream output at 70 percent efficiency. semiconductor Wycow price structures. that is a market opportunity of \$10 billion to \$25 billion.

4 cents per watt.

balance between performance, power efficiency, small size and reliability - and they must do this at a price point that promotes mainstream commercial adoption. Championing the full potential of GaN for RF energy is a nonprofit technical association, the RF Energy Alliance. It anticipates that the market can take off with the introduction of 300 W power amplifier modules that combine 70 percent efficiency with a price of just

The RF devices

underpinning these

systems have to strike an optimal

We are addressing this challenge with our recently released MAGe-102425-300. This is a rugged 300 W, GaN-on-silicon power transistor housed in a cost-effective plastic package optimized for use in commercial-scale solid-state RF energy applications. Incorporating Gen4 GaN technology, our MAGe-102425-300 delivers a performance that defies the inherent power efficiency and density limitations of LDMOS, while retailing at an equivalent price profile at scaled volume production levels. The MAGe-102425-300, which provides a 300 W output power at 2.45GHz, at an efficiency of 70 percent. leads the industry in meeting the core technical requirements for next-generation power amplifiers proposed by the RF Energy Alliance.

As a member of the Alliance, we are committed to advancing the organization's charter to standardize solid-state RF energy technology and its associated components and sub-module roadmaps - an effort that will reduce complexity, cost, and the development time associated with bringing related products to market. The mainstream adoption of solid-state RF energy hinges in part on the cooperation and collaboration of Alliance member companies and the industry at large.

Advances in the technology of GaN and its supply chain have taken us to a position where we can deliver breakthroughs in manufacturing scale and cost structures. This will spur the mass market adoption of this technology. Its great performance at a competitive price will open up many new markets, ranging from heaters for microwave ovens and large-scale drving to new units for automotive ignition systems and horticultural lighting. There is no doubt that GaN-onsilicon RF transistors have a bright future ahead of

# EPITAXIAL GROWTH partner

# Enabling advanced technologies

- World leading technology

- Complete materials range

- MOCVD, MBE, CVD

- Advanced semiconductor wafer products

- Advanced R&D capabilities

- Multiple, manufacturing sites (Europe, Asia, USA)

www.iqep.com

DURING THE LAST DECADE, there has been a widespread, on-going debate over the origin of droop. Attempts to uncover the cause of droop have focused on the blue-emitting chip, which overlooks one of the key processes in the solid-state light bulb. As white light is produced by mixing the blue emission from the chip with that generated by an optically pumped phosphor, it is crucial to consider whether the phosphor is also prone to droop.

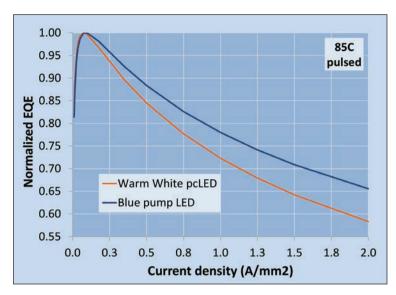

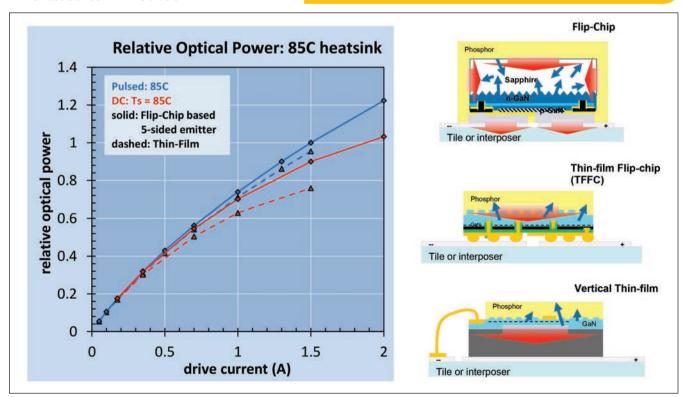

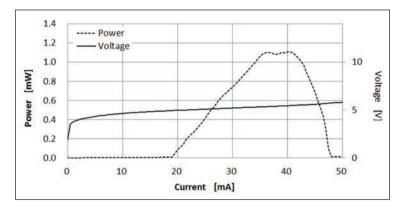

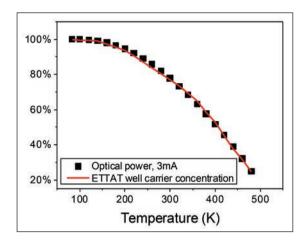

One way to illustrate that droop in white LEDs can be appreciably higher than that produced by the blue pump LED alone is to compare the normalized external quantum efficiency of a warm-white, 1mm<sup>2</sup> thin-film-flip-chip LED and its constituent blue pump LED at a range of drive currents (see Figure 1). Pulsed driving conditions distinguish between the impact of drive current density and thermal effects, and reveal that droop is significantly more severe in a white LED than a blue-emitting chip.

These measurements have led our team at Lumileds to scrutinise Europium-doped red nitride phosphors, which are commonly used in state-of-the-art LEDs to provide emission at longer wavelengths. This investigation involved measurements of quantum conversion efficiency for the LED phosphor at different temperatures and different intensities of blue light irradiance. To distinguish between the influence of temperature and irradiance, we employed pulsed excitation. Laser pulses were long enough to account for phosphor luminescence rise and fall times, and heating was avoided with a 1 kHz duty cycle.

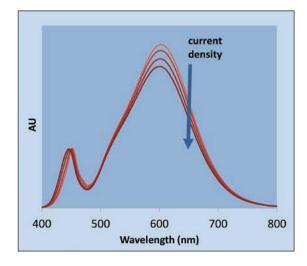

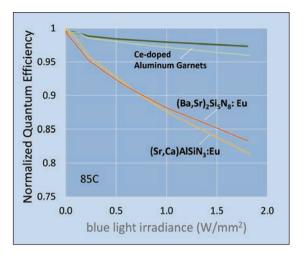

Our study has not been limited to the europiumdoped nitride red phosphors, and includes the commonly used cerium-doped aluminium garnets. Both phosphors suffer from droop, but this is more pronounced in the europium-doped nitride reds here phosphor photo-quenching is severe enough to contribute between 20 percent and 25 percent of the droop in warm-white LEDs. Compounding matters, the phosphor-related droop produces a shift in spectral output towards higher colour-correlated temperatures.

As cerium-doped aluminium garnet is less prone to droop than europium-doped nitride red phosphors, at first glance it would appear that the solution is to use this in white-emitting LEDs. But such an approach is not practical, because the spectral output of this phosphor is not suitable for realising a high colourrendering index. A better way forward is to understand the limitations of europium-doped nitride red phosphors and devise approaches to minimising the droop associated with them.

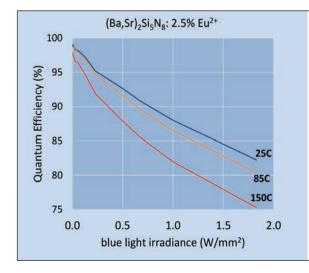

To gain greater insight into the underlying physics of europium-doped nitride reds, and the impact of photo quenching on LED performance, we prepared (Ba,Sr)<sub>2</sub>Si<sub>5</sub>N<sub>8</sub>: Eu<sup>2+</sup> powders with varying europium concentration. Our quantum efficiency

measurements revealed that the rate of quenching in (Ba,Sr),Si,N,:Eu2+ increases with temperature and europium concentration (see Figure 4). These findings can guide phosphor material and LED architecture design, and lead to a better understanding of the physics of the quenching mechanism.

Figure 1. Efficiency droop is more severe in white LFDs than it is in blueemitting chips.

We have fitted the experimental rate of phosphor quenching in our samples with a model for radiative and non-radiative recombination processes. This gives a close fit when using a term that is close to the quadratic of the concentration of excited Europium activators. This model replicates results for different concentrations and thicknesses, so long as the nonlinear, non-radiative coefficient is kept constant.

These insights suggest that of the two most probable candidates for the non-radiative processes - Foerster/ Dexter cross relaxation and excited state absorption - it is the latter that is the likely culprit in phosphor quenching. As excited state absorption is excitation dependent, it is similar to the very familiar non-linear process of droop in InGaN quantum wells. This intrinsic loss mechanism for the phosphor cannot be

Figure 2: The droop in efficiency is accompanied by the shift in white LED spectra, which gives insights into the process of photoquenching in phosphors.

# **INDUSTRY** LEDS

Figure 3: The drop in quantum efficiency with excitation varies with the phosphors used in state of the art LEDs.

eliminated, but it is possible to minimise its impact via engineering at the material and device level.

Our experiments point to an approach for reducing phosphor droop – cutting the activator concentration. The downside is that to realise a desired colour point, there must be a longer optical path for pump light through the phosphor. In practice, this means thicker or heavier-loaded converting layers, which lead to excessive scattering and heating and ultimately lower LED efficiency.

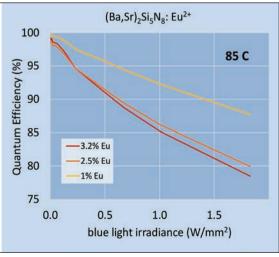

One way to mitigate these unwanted consequences is to turn to ceramic phosphor materials. Their attributes include excellent thermal properties and greatly reduced optical scattering, which allows for thicker converting layers without efficiency penalties. This is a solution that we have adopted in a number of products that feature our Lumiramic phosphor technology (see Figure 5).

LED devices can also be designed to minimise the quenching and its increase with temperature (the effect revealed in our measurements (see Figure 4)). The key is to reduce blue light irradiance and to draw the heat out of the phosphor layer as effectively as possible, while maintaining a low overall temperature. An illustration of this mitigation of photo-thermal

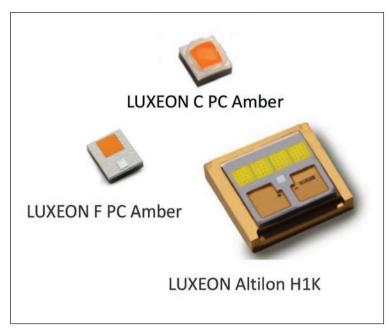

quenching through LED design is provided by a comparison of two die-on-ceramic LED packages one is a thin-film flip-chip, and the other a flip-chip architecture. With the thin-film flip-chip design - and any thin-film LED architecture for that matter - blue light is extracted through one side of the die. So, due to this, phosphor particles are positioned near the emitting surface of the die, in a thin layer of silicone.

In contrast, with a flip-chip architecture, the phosphorfilled converting layer can be placed on all five sides of the transparent sapphire substrate. This means that the blue light emitted by the active region of the pump LED can be distributed over a larger area than it would be with a thin-film design. What's more, with a flip-chip, the heat of down-conversion is conducted through a larger contact area.

The superiority of the flip-chip architecture over the thin-film flip-chip design is proven in our measurements of normalized optical power output (see Figure 6). As expected, the reduction in the intensity of the pump light on the phosphor, as well as better phosphor heat-sinking in the flip-chip LED, enables this type of design to be less afflicted by droop than its thin-film flip-chip cousin.

For both designs, droop is more prevalent when the device is driven continuously, rather than in pulsed operation. That's because the device driven continuously runs at a higher temperature, and photothermal quenching of the europium-doped nitride phosphors is more prevalent.

It is worth noting that at 1.5 A, which is a typical maximum operating current for a 1 mm<sup>2</sup> active-area high-power LED, although the junction temperatures of both classes of devices are within 5°C of the estimated 125 °C, the difference in phosphor temperatures is significantly higher. This contributes to the difference in light output and efficiency between the two architectures, which is more than 15 percent.

The merits of a lower phosphor temperature and a lower irradiance of phosphor are very welcome,

Figure 4: Photoquenching in Eu2+ red nitrides shows strong dependence on temperature and activator concentration.

because they enable the flip-chip design to maintain high efficiency into even higher current densities. The flip-chip design is not the only architecture for reducing photo-quenching. There are also the remotephosphor configurations that are often seen in lighting modules, and mid-power LED or chip-on-board-type emitters. In these architectures, blue light is distributed over a large phosphor volume, which helps to maximize efficiency. The downside is a compromise in source brightness, limiting emitter usability.

For high brightness applications - such as automotive LEDs, laser-based sources, and forms of architectural lighting that require narrow, collimated beams - photo-thermal quenching of phosphors is a basic limitation. In these applications there is a need for sources with the lowest etendue possible, which means minimizing the emitting area and the angle of the source.

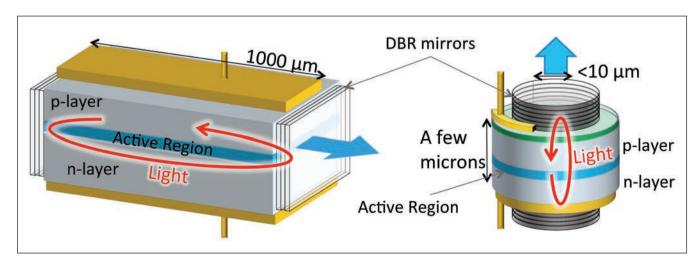

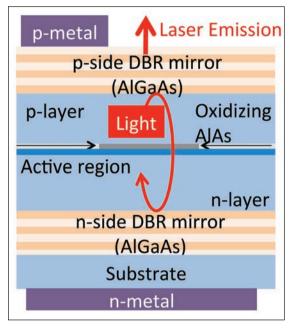

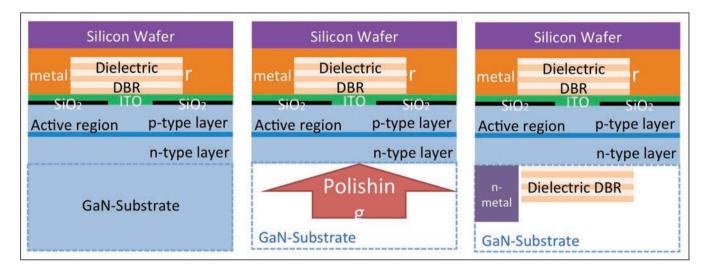

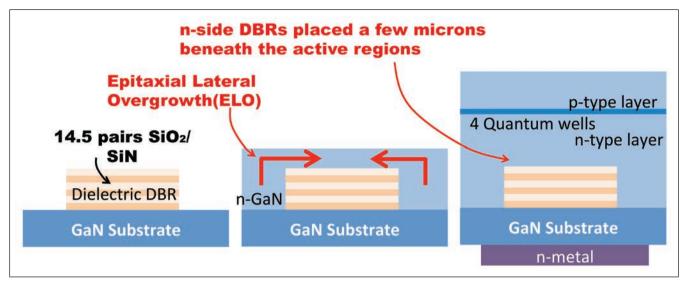

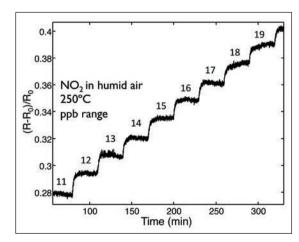

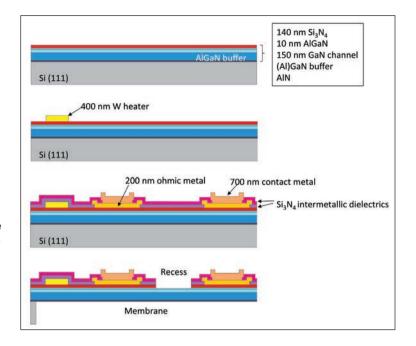

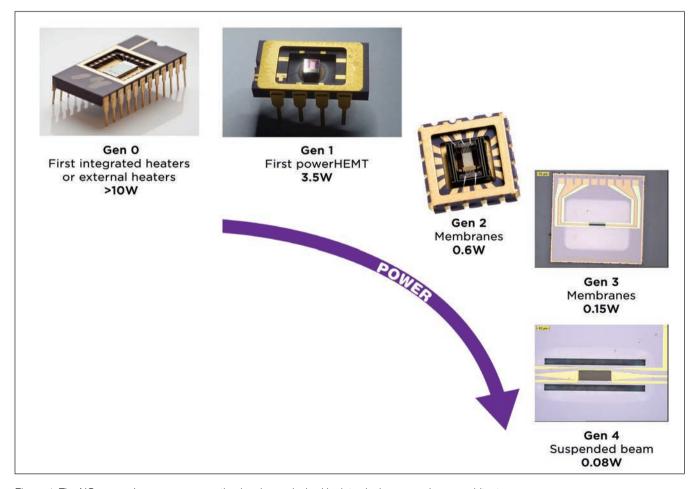

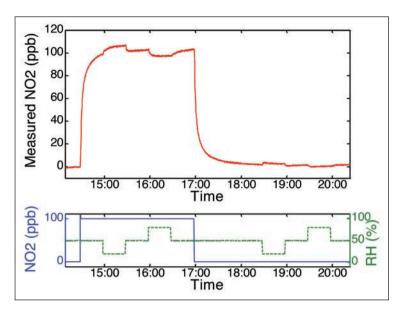

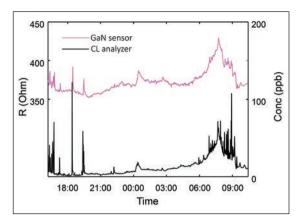

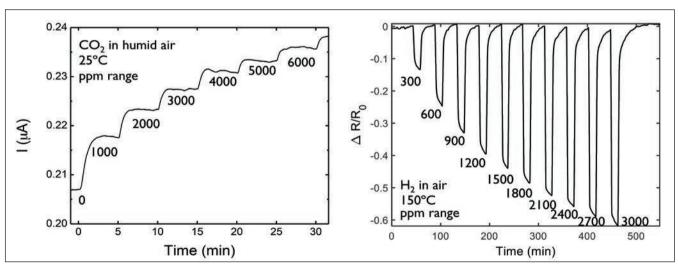

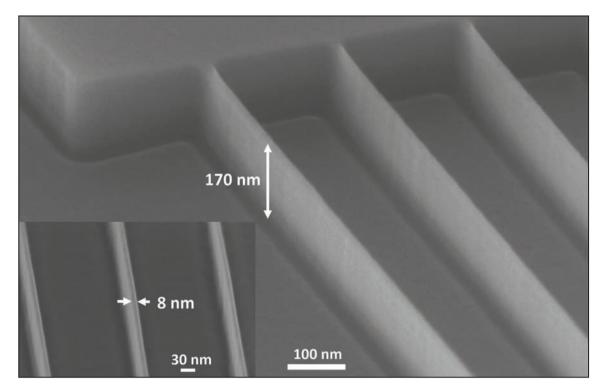

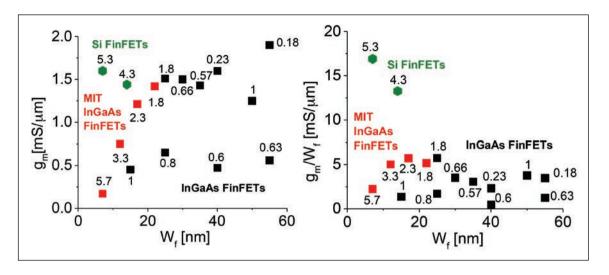

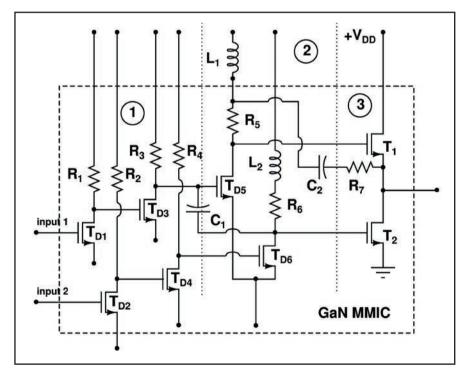

In short, as photo-thermal quenching is a basic property of phosphor materials, it will impact LED efficiency. While LED architecture design can be used to mitigate this form of droop, ultimately, the best solution is at the material level. We have shown success in this area through the use of ceramic phosphors.