# COMPOUND SENICONDUCTOR Connecting the Compound Semiconductor Community

Volume 25 Issue 2 MARCH 2019

🔰 @compoundsemi

www.compoundsemiconductor.net

Diamond draws the heat from GaN HEMTs

Creating transparent circuits with GaN

Obliterating dynamic onresistance degradation

Making smart watches with microLED displays

Electric vehicles enhance the prospects for SiC

**Inside** News Review, News Analysis, Features, Research Review, and much more... Free Weekly E News round up go to: www.compoundsemiconductor.net

# Global mega trends require best performance III-V materials AIX 2800G4-TM

RIXTROI

RIXTRON

L'an

uu

- 3D sensingAugmented reality

- Autonomous driving

- Cloud computing

- Internet of things

Next generation displays

Discover the MOCVD tool of record for AsP-based applications

Made in Germany

www.aixtron.com

# Viewpoir

By Dr Richard Stevenson, Editor

### GaN-on-diamond gathers pace

YOU AND I both know that the uses of diamond are not limited to jewellery. Unlike those working outside our industry, we are aware of the exceptional thermal conductivity of this material, and its capacity to suck the heat out of devices placed on top of it.

Championing the capability of GaN-on diamond is Felix Ejeckman. He invented the technology at Group4Labs, took it to new heights when this company was bought by Element Six, and more recently has co-founded Akash Systems, which is working on getting GaN-on-diamond products on board satellites (see p 20 for details).

But Akash is by no means alone in advancing this technology. Other companies are getting involved, creating a strengthening supply chain, as I discovered when attending the inaugural Diamond D-Day meeting.

At this one-day gathering, held in Bristol at the end of January and attended by 120 delegates from all over the world, makers of diamond deposition tools rubbed shoulders with the suppliers of GaN-on-diamond epiwafers and those that offer foundry services for these materials.

One company that made a particularly strong impression was the South Korean outfit RHFIC, which has ambitions

to dominate the GaN-on-diamond market. It has over 60 patents, and intellectual property that covers all markets, apart from the commercial satellite sector. Its vision is to see GaN-on-diamond replace GaN-on-SiC, with

products serving in self-driving cars, military radar, and industrial, medical and scientific sectors.

RHFIC produces GaN-on-diamond epiwafers at both its R&D facility in the US, and its production line in Korea. At the latter, the aim is to crank up production to 100 wafers per month.

One company capable of processing these wafers into devices is GCS. This foundry has developed techniques for running this material through its automated lines, and has produced devices with encouraging results. These include 0.65 µm HEMTs producing a power density of 22.5 W/mm at 2 GHz when biased at 100 V.

GCS is also developing a process to realise through substrate vias. Initial results are validating the approach.

Given the impressive efforts by the likes of Akash, RHFIC and GCS, sales of GaN-on-diamond devices are sure to grow over the next few years. But will they ever overtake GaN-on-SiC, and be the dominate technology in the GaN RF market? Probably not, but only time will tell.

Editor Richard Stevenson Contributing Editor Rebecca Pool News Editor Christine Evans-Pughe Sales Executive Jessica Harrison USA Representatives Tom Brun Brun Media Janice Jenkins Publisher Jackie Cannon Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor richardstevenson@angelbc.com +44 (0)1291 629640 editorial@rebeccapool.com chrise-p@dircon.co.uk jessica.harrison@angelbc.com tbrun@brunmedia.com iienkins@brunmedia.com iackie.cannon@angelbc.com sharon.cowley@angelbc.com

mitch.gaynor@angelbc.com

+44 (0)2476 718209 +001 724 539-2404 +001724 - 929 - 3550+44 (0)1923 690205 +44 (0)1923 690200 +44 (0)1923 690214

Circulation Director Jan Smoothy +44 (0)1923 690200 jan.smoothy@angelbc.com stephen.whitehurst@angelbc.com +44 (0)2476 718970 Chief Executive Officer Stephen Whitehurst

Directors Bill Dunlop Uprichard - EC, Stephen Whitehurst - CEO, Jan Smoothy - CFO Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal

Published by Angel Business Communications Ltd. Unit 6. Bow Court. Fletchworth Gate, Burnsall Road. Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

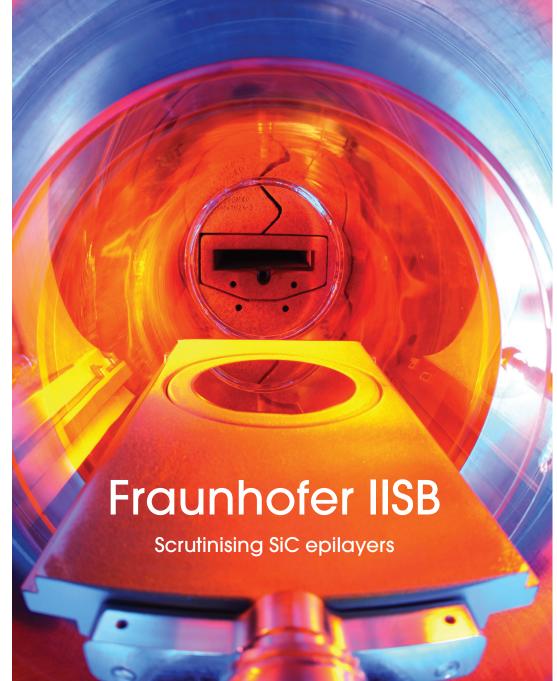

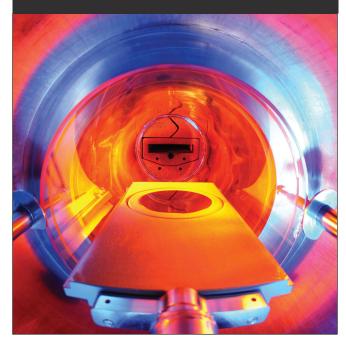

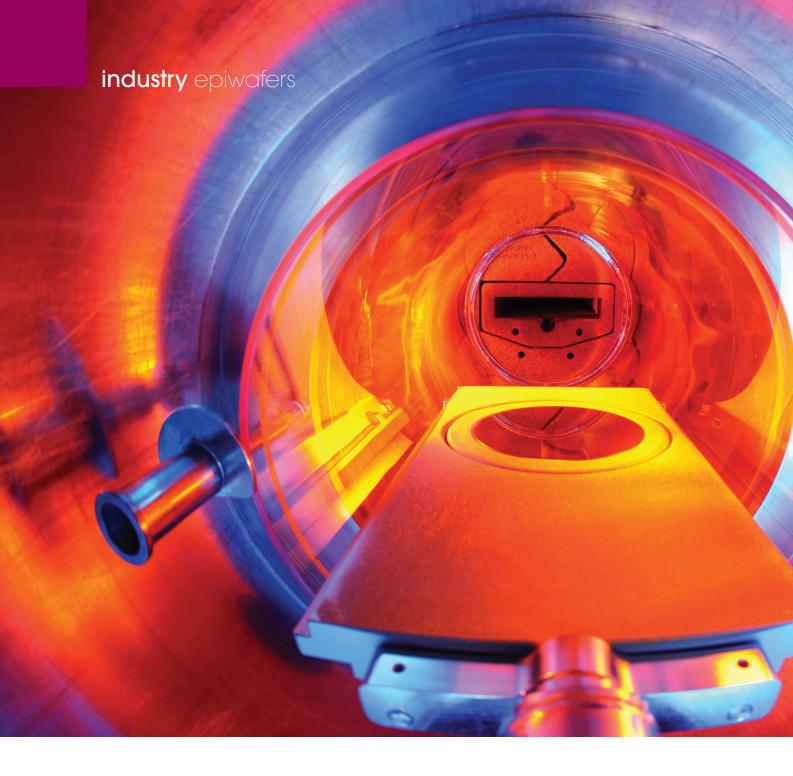

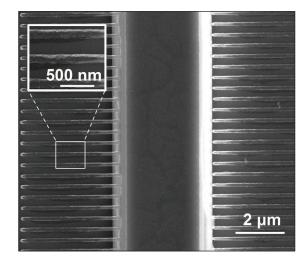

### Cover photo by "Kurt Fuchs/Fraunhofer IISB. © 2019.

recycle Angel 🕢 ppa The Professional Publishers Association Member

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 68P. UK. The 2019 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2019.

# CONTENTS

### 50 COVER STORY

### Scrutinising SiC epilayers

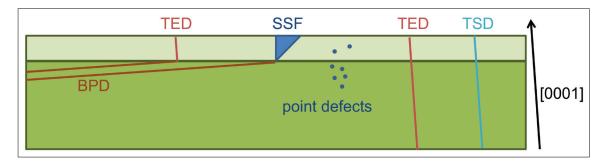

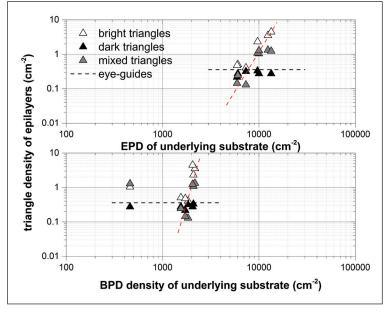

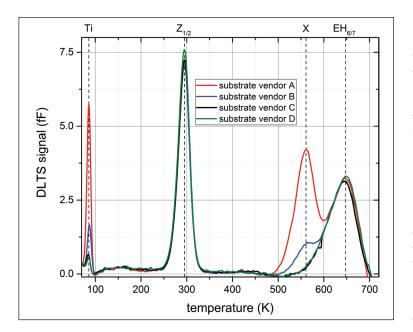

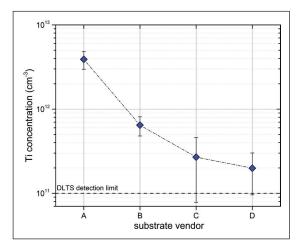

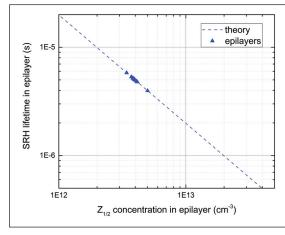

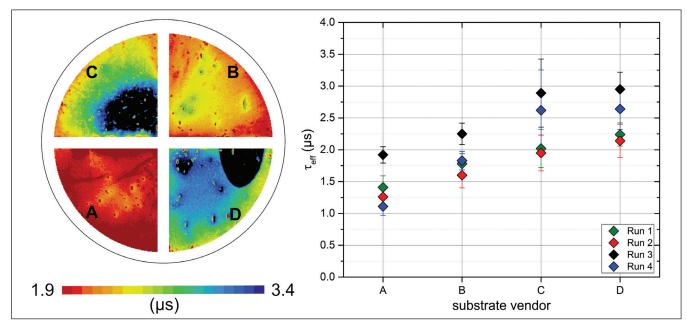

Careful control of the growth process limits the carbon vacancies that govern the carrier lifetimes, but some extended defects and point defects in epilayers are determined by the substrate quality

# 20 Drawing the heat with diamond

Sucking the heat out of a GaN transistor with diamond film is to become ever more common, thanks to a strengthening supply chain for this technology

### 24 Invisible contacts

Transparent GaN circuits are on the horizon, thanks to transfer processes for shifting the transistors onto glass, and the creation of see-through contacts, based on indium tin oxide and ion implantation

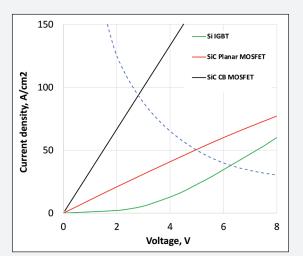

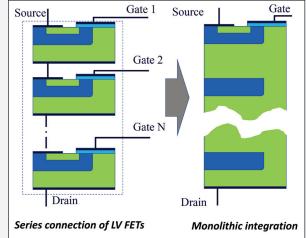

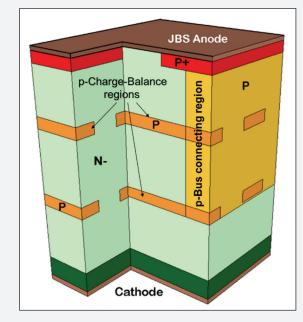

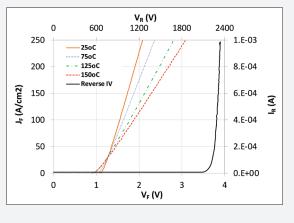

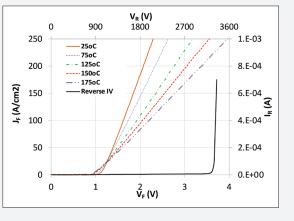

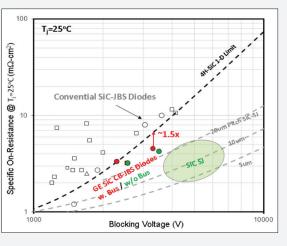

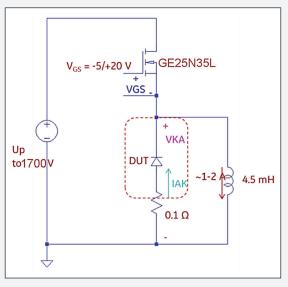

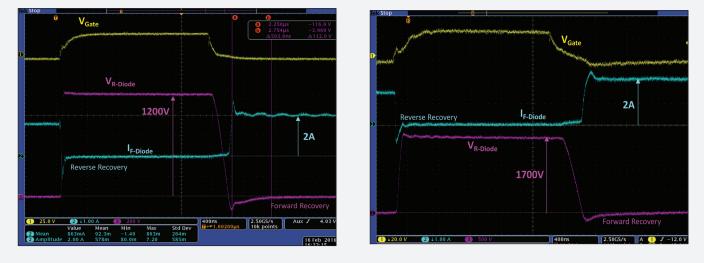

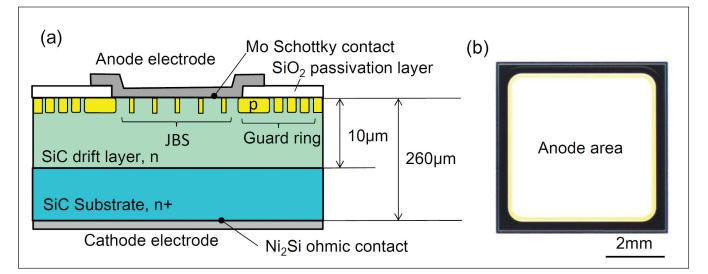

# 34 Balancing charges to boost performance

Incorporating a novel charge-balance drift region into a SiC Schottky barrier diode sets a benchmark for the key metric: on-resistance as a function of breakdown voltage

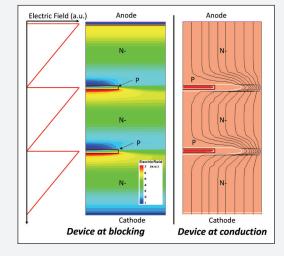

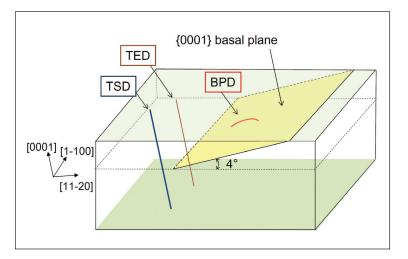

### 40 Superior silicon carbide

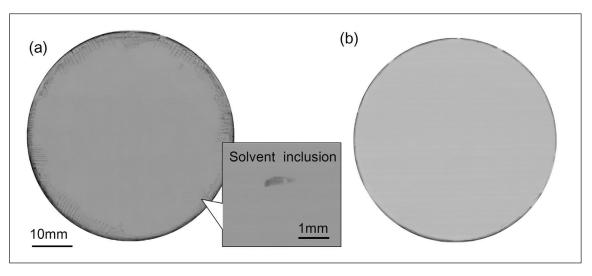

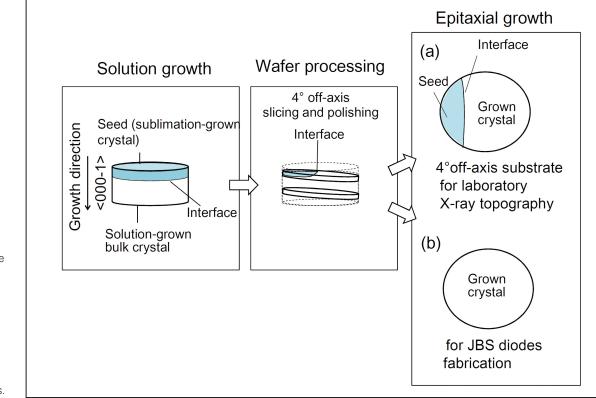

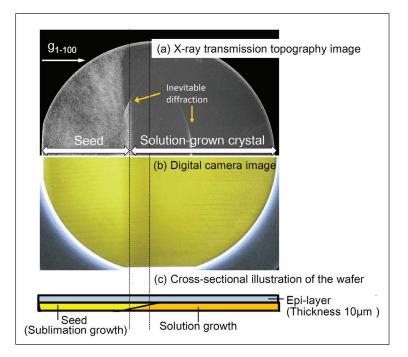

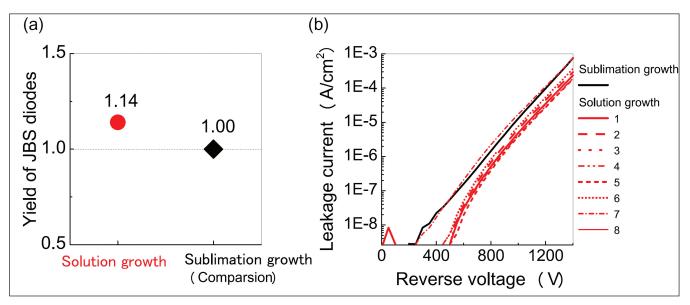

Solution growth eliminates basal plane dislocations in high-quality single crystals of bulk SiC

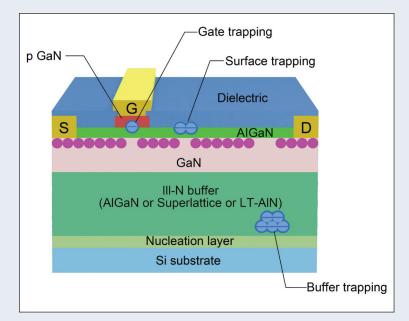

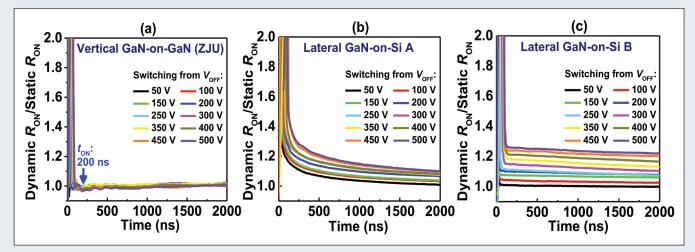

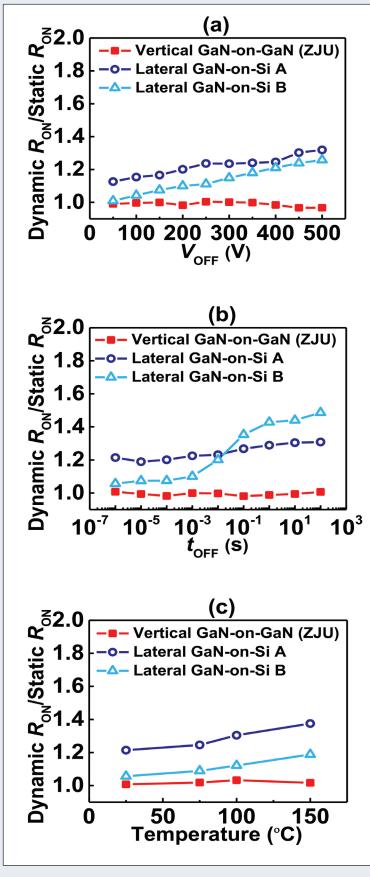

### 56 Obliterating dynamic on-resistance degradation

Vertical GaN-on-GaN power devices enable currentcollapse-free performance

### news

- O6 ARPA-E awards \$35 million for power device research

- 07 Cree boosts horticulture efficiency with new red LEDs

- 08 Laser lights for cars

- 09 RF GaN growing at 23 percent CAGR

- 10 SUSS opens excellence centre in Switzerland

- JEDEC WBG committee publishes first document

### news analysis

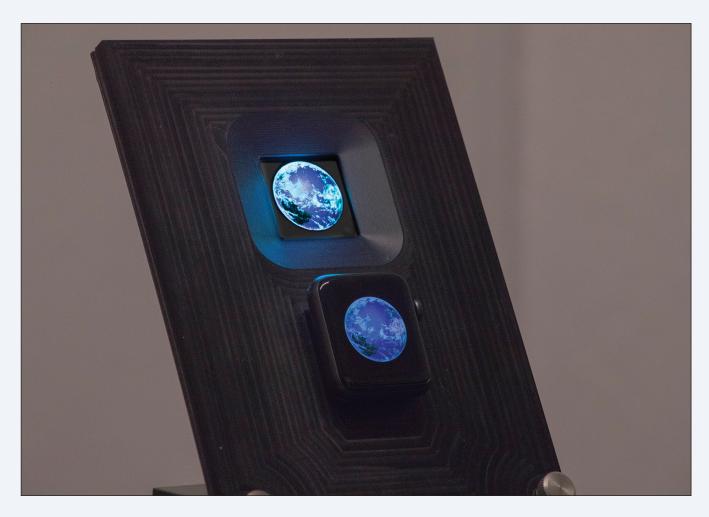

# 12 Glo on cusp of commercialization

A smart watch made from Glo's micro-LEDs could be on your wrist very soon

### 14 Wolfspeed: From strength to strength

Since joining Cree, chief executive, Gregg Lowe, has bolstered its power and RF business beyond belief.

### research review

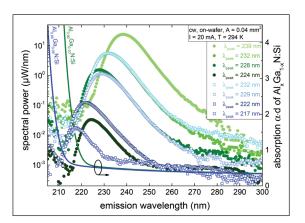

62 Understanding the limitations in deep UV LEDs

> Experiments expose a decline in carrier-injection efficiency as a major barrier to highperformance, deep UV LEDs

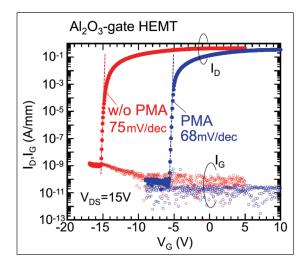

### 63 Assessing the optimal GaN HEMT

For great gate controllability and operation stability, make and anneal GaN MISHEMTs

### 64 GaSb laser combines power with spectral purity

Chromium gratings create lasers with a 40 mW single-mode output and a ground-breaking side-mode suppression ratio

## ARPA-E awards \$35 million for power device research

THE US DEPARTMENT OF ENERGY has announced \$35 million in awards for 12 projects that find new ways to harness medium-voltage electricity for applications in industry, transportation, on the grid and beyond.

The selected projects are part of ARPA-E's Building Reliable Electronics to Achieve Kilovolt Effective Ratings Safely (BREAKERS) programme, as well as the latest OPEN+ cohort, Kilovolt Devices.

"America's energy landscape is constantly evolving, and as new ways to generate and distribute power gain popularity, it's critical we develop the tools to maximise their utility," said US Secretary of Energy Rick Perry. "These ARPA-E projects serve first and foremost to modernise how we move power around safely, reliably and efficiently, creating a new set of capabilities for tomorrow's utilities and industry. "

The eight BREAKERS projects will work to develop new direct current (DC) devices to better manage power by eliminating electrical faults, improving efficiency and reaction times, and potentially enabling greater proliferation of energy storage and renewable resources. The four Kilovolt Devices OPEN+ projects will focus on a variety of challenges facing power electronics

in the medium-voltage space, with a particular eye toward grid security and reliability.

Today's power distribution networks are primarily powered by alternating current (AC) electricity, but DC can provide lower distribution losses and higher power carrying capacity. BREAKERS projects will develop DC devices that prevent electric arcing, a safety hazard, while handling large amounts of power and voltage.

Medium-voltage DC circuit breakers could enable significant improvements in the United States' electrical system, transforming how electricity is delivered and managed across the entire power grid, as well as critical applications in industry, transportation, and resource production.

Example projects include \$3,760,000 awarded to Eaton to develop a DC Wide Bandgap Static Circuit Breaker. Eaton will develop a SiC-based direct-current circuit breaker design that boosts efficiency and can scale up or down medium-voltage application requirements. The team's comprehensive approach includes a robust design that effectively dissipates excess energy and autonomously coordinates fault protection across multiple devices. The project results will extend to future ultra-wide bandgap power semiconductor devices and other advances affecting future generations of devices and power electronics.

Ohio State University has been awarded \$2,211,712 to develop GaN semiconductor materials suitable for high voltage (15-20 kV) power control and conversion. The team will develop a unique method to grow thick GaN films with low background impurity contamination, necessary to allow high voltage operation with high efficiency.

The thick GaN layers will be deposited on high-quality bulk GaN base materials with reduced defects, critical to depositing high-quality GaN films on top, and perform high-voltage device design, fabrication, and testing to provide feedback for further GaN material growth and optimisation.

### Macom and STMicro ramp GaN-on-silicon support for 5G

MACOM TECHNOLOGY and STMicroelectronics have announced the 2019 expansion of 150 mm GaN-on-silicon production capacity in ST's fabs, and 200 mm as demand requires. The expansion is designed to service the worldwide 5G Telecom buildout. This builds upon the broad GaN-on-silicon agreement between Macom and ST announced in early 2018.

The global rollout of 5G networks and move to Massive MIMO (M-MIMO) antenna configurations is expected to create a substantial increase in the demand for RF Power products. Specifically, Macom estimates there will be a 32x to 64x increase in the number of Power Amplifiers required. In turn, this is expected to more than triple dollar content over the course of a 5-year cycle of 5G infrastructure investment and thus drive an estimated 10x to 20x decrease in the cost per amplifier.

"Major base station OEMs understand they need wide bandgap GaN performance with transformational cost structures and manufacturing capacity to meet 5G antenna cost, range and energy efficiency targets in the field. By teaming with ST, we believe Macom is uniquely poised to provide it all performance, cost and high-volume supply chain," said John Croteau, President and CEO of Macom. "We anticipate that our joint investment at this early stage in bringing on more capacity positions for us to service up to 85 percent of the global 5G network buildout."

"ST has built a strong foundation as a global leader in SiC and we are now moving forward with RF GaN-on-silicon, which will enable OEMs to build a new generation of high-performance 5G networks," said Marco Monti, president of the Automotive and Discrete Product Group, STMicroelectronics. "While SiC is ideal for certain power applications such as automotive power conversion, GaN-on-silicon provides the necessary RF performance, scale, and commercial cost structures to make 5G a reality. With this move ST and Macom aim to unlock the industry bottleneck and fulfil the demand for 5G buildouts."

news review

## Cree boosts horticulture efficiency with new red LEDs

CREE has announced the nextgeneration XLamp XP-E2 Photo Red (660 nm) and Far Red (730 nm) LEDs, delivering higher performance for horticulture applications.

The new Red XP-E2 LEDs provide a dropin upgrade for the previous generation that outperforms competing LEDs by up to 68 percent. These higher-performance horticulture LEDs make it more affordable to grow food under optimised lighting, according to Cree.

"Lettuce and tomato farmers in the UK, the Netherlands and Belgium are choosing our Hyperion grow lights, powered by Cree's horticulture LEDs, as the primary light source for their large indoor, state-of-the-art growing facilities," said Jonathan Barton, director of Grow Lighting at Plessey Semiconductors. "Our customers like that the Hyperion lights replace 1000 W sodium lights one-for-one with up to 40 percent energy savings that are enabled by Cree LEDs. We are pleased that Cree is delivering this efficiency upgrade in a form that's easily integrated, so that we can quickly improve our product's performance." The new XP-E2 LEDs are a dropin upgrade for existing XP-based horticulture designs with the same mechanical and optical characteristics as the previous generations.

With up to 57 percent improvement in Far Red and up to 21 percent improvement in Photo Red, this new generation of XP-E2 LEDs delivers industry-leading output levels and efficiency within their performance class. "LEDs for specialty applications, including architectural lighting and horticulture, are a core part of our product strategy," said Claude

Demby, Cree LEDs senior vice president and general manager. "Cree is first to enable full spectrum luminaires that employ Photo Red and Far Red LEDs to deliver 50 percent energy savings over sodium-based lighting systems. This upgrade to our horticulture LEDs demonstrates our commitment to delivering industry-leading high-power LED performance."

### Laser light for cars

OSRAM has introduced the PLPT9 450D\_E A01 – a second generation blue multi-mode laser diode designed to be a light source for auxiliary high beam that doubles the range (compared to previous LED solutions) to 600 meters. It also simplifies the system design, according to the company.

"With our newly developed laser diode, car lights can be designed and built even smaller than before– without compromising light output. It combines powerful light with compact dimensions," explains Walter Rothmund, marketing manager automotive for Emitter Laser Sensor at Osram Opto Semiconductors. In terms of brightness, laser diodes offer advantages compared to LEDs.

At a typical operating current of 2.2 A, the blue PLPT9 450D\_E A01 laser reaches an optical output of 3.5 W and emits blue light with a wavelength of 447 nm. With the help of appropriate optics, the laser light is focused at a point only a few micrometers in diameter. A special phosphor converter converts the blue light into white light required for front lighting applications. The luminance achieved is three times higher than that of an LED light source. In comparison,

the laser produces 600 cd/mm<sup>2</sup> while LEDs deliver around 200 cd/mm<sup>2</sup>.

The PLPT9 450D\_E A01 laser diode qualified for use in cars is approved for an operating temperature range of -40°C to 120°C. Compared to the first generation with three pins, the TO90 package contains only two pins, which allows for much easier connection and heat dissipation. The laser's compact dimensions of 9 mm in diameter and a height of < 4.5 mm (without contact pins) mean that headlights can be built much smaller in the future, says Osram.

### II-VI introduces 56 Gb/s PAM4 VCSEL arrays

OPTICAL COMPONENT FIRM II VI has introduced its 56 Gb/s PAM4 VCSEL arrays for 400 gigabit Ethernet (GbE) short reach transceivers and active optical cables (AOCs) deployed in data centres.

The availability of Ethernet equipment with greater than 12 Tb/s of switching capacity enables hyperscale data centres to accelerate the migration from 100 to 400 GbE transmission. II-VI's 8-element VCSEL arrays can be modulated at 56 Gb/s using 4-level pulse amplitude modulation (PAM4) to achieve a combined 400 Gb/s over short reach multimode links.

"Customers come to II-VI because of our ability to deliver differentiated VCSEL

technology without ever compromising on reliability," said Karlheinz Gulden, general manager, II-VI Laser Enterprise. "Our new 56 Gb/s PAM4 VCSEL arrays represent the leading edge in VCSEL technology for AOCs and transceivers, which are in high demand in data centres for server to server connectivity."

AOCs and transceivers based on VCSELs offer the most cost effective solution for datacenter links that span from 10 to 300 meters. They enable new applications in consumer electronics to connect ultrathin HDTV screens to remotely located driver electronics. The demand for VCSELs is expected to accelerate, driven by a growing number of 3D sensing applications in automotive and consumer electronics.

### Qorvo ships 100 million RF devices for 5G

RF COMPANY Qorvo has announced that it has shipped over 100 million 5G wireless infrastructure components since January 2018. It released the news at Mobile World Congress 2019, February 25-28, in Barcelona.

Qorvo's 5G portfolio includes solutions for both the receive and transmit RF front end, enabling customers to use beamforming with massive multiple-in/multiple-out (MIMO) base stations to achieve higher data capacity, wider coverage, and indoor penetration using sub-6 GHz frequencies.

The installation of new 5G networks using massive MIMO architectures have created demand for new products supporting higher frequencies and increased integration. Qorvo's portfolio includes dualchannel low noise amplifiers (LNAs) integrated with high-power-handling switches, high linearity transmit pre-drivers, and final stage power amplifiers (PAs). Qorvo's GaN-based PAs for all sub-6Gz 5G bands feature fully integrated Doherty solutions that support the higher frequency, small size, weight, power consumption and thermal management requirements for 5G equipment.

Roger Hall, general manager, Qorvo High Performance Solutions, said: "Qorvo is enabling mobile operators to enhance their existing network capacity and transition to 5G with minimal effort. Our technology leadership with massive MIMO based on beamforming is revolutionizing the base station market and accelerating the path to 5G."

New Qorvo products that are available now to wireless infrastructure customers include the QPB9337 Dual-Channel Switch LNA module, the QPL9057 Ultra-Low NF LNA, and the QPA3503 Doherty Power Amplifier module.

## **RF GaN growing at 23 percent CAGR**

THE RF GaN industry is showing an impressive growth with a 23 percent CAGR between 2017 and 2023, driven by telecom and defence applications.

By the end of 2017, the total RF GaN market was close to \$380 million and 2023 should reach more than \$1.3 billion with an evolving industrial landscape. Telecom and defence are looking for innovative technologies and RF GaNbased devices are directly answering to the market demand.

Defence remains a major RF GaN market segment, as its specialised high-performance requirements and low price sensitivity offer many opportunities for GaN-based products. In 2017-2018, the defence sector accounted for more than 35 percent of the total GaN RF market, and the global defence market shows no signs of slowing down.

"We believe this important GaN market segment will continue growing along with GaN's overall penetration rate," says Hong Lin, senior technology and market analyst at Yole Développement (Yole), part of Yole Group of Companies.

Yole's partner, Knowmade, has recently looked at more than 3,750 patents published worldwide up to October 2018 and produced a report based on its analysis. The patents apply to RF GaN epiwafers including GaN-on-SiC

and GaN-on-silicon, RF semiconductor devices, including HEMTs and HBTs, integrated circuits, including RFICs and MMICs, operating methods and packaging, for all functions, such as RF PAs, RF switches and RF filters and from radio frequencies <6GHz to microwaves >6GHz and mm-waves >20GHz.

"Cree (Wolfspeed) indisputably has the strongest IP position, especially for GaN HEMTs on SiC substrate," says Nicolas Baron, CEO and co-founder of Knowmade. "Sumitomo Electric, the market leader in RF GaN devices, is well positioned but far behind Cree."

Furthermore, Sumitomo Electric has been slowing down its patenting activity while other Japanese companies like Fujitsu, Toshiba and Mitsubishi Electric are increasing their patent filings and thus today have strong patent portfolios as well.

Intel and Macom are currently the most active patent applicants for RF GaN, both especially for GaN-on-silicon technology, and are today the main IP challengers in the RF GaN patent landscape.

Other companies involved in RF GaN market, such as Qorvo, Raytheon, Northrop Grumman, NXP/Freescale, and Infineon, hold some key patents but do

not necessarily have a strong IP position. CETC and Xidian University dominate the Chinese patent landscape with patents on GaN RF technologies targeting microwave and mm-wave applications. And the emerging foundry HiWafer, entered the IP landscape three years ago, is today the most serious Chinese IP challenger.

From a device perspective, Cree (Wolfspeed) has also taken the lead in the GaN HEMT IP race for RF applications. "The analysis of Cree's RF GaN patent portfolio shows it can effectively limit patenting activity in the field and control the freedom-to-operate of other firms in most key countries," explains Baron from Knowmade.

Intel, which entered the GaN HEMT patent landscape later, is currently the most active patent applicant and it should strengthen its IP position in coming years, especially for GaN-onsilicon technology. New entrants in the GaN RF HEMT related patent landscape are mainly Chinese players: HiWafer, Sanan IC and Beijing Huajin Chuangwei Electronics.

Other noticeable new entrants are Taiwan's TSMC and Wavetek Microelectronics, Korea's Wavice and Gigalane, Japan's Advantest, and America's Macom and ON Semiconductor.

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and defense industries.

MasimoSemiconductor.com | 603-595-8900

## SUSS opens excellence centre in Switzerland

SUSS MICROOPTICS is setting up an excellence centre in Neuchâtel Switzerland for manufacturing waferlevel optics (WLO) in order to meet the increase in demand for precision optics applications.

Among the various structures that can be manufactured at wafer-level, freeform micro-optic arrays are one of the most challenging, as they have no rotational symmetry. Thanks to this property, they can generate new light distribution patterns, correct for aberrations, as well as improve miniaturisation of the optical systems.

This will be key for driving the volume production of new optics for volume markets such as automotive, transportation, lighting, augmented reality, medical, datacom, consumer electronics etc. The excellence centre will be part of 800m<sup>2</sup> of new cleanroom space currently built in Neuchâtel and certified for the main markets targeted by SUSS MicroOptics.

The European photonic industry Consortium (EPIC) has consistently shown strong support for European funded Photonics Pilot Lines manufacturing photonic devices. EPIC is already the dissemination partner of the MIRPHAB pilot lines (manufacturing of MID-IR photonics sensors), PIXAPP (manufacturing of packaged integrated photonic devices) and InPULSE (manufacturing of photonic integrated circuits based InP).

Jose Pozo, EPIC's CTO, claims "these European pilot lines, whether funded or not by the EU, are essential for the exploitation of the great innovations in photonics in Europe.

Photonics21 and the Photonics public private partnership, are playing the necessary role for manufacturing of Photonics, as a key enabling technology, in Europe. We strongly believe that such pilot lines are the best way of enabling the manufacturing of photonics in Europe to customers worldwide and of valorising and monetising the photonics innovations which have positioned Europe in the lead of photonics R&D."

The expertise of SUSS MicroOptics, based on imprint technologies, enables the production of the last mile in optics: the so-called freeform micro-optics, mainly optical diffractive, refractive or reflective components with no rotational symmetry. Until now most freeform optics applications have been in niche markets, such as space and others.

Recently however, high volume applications in consumer markets especially in automotive, mobile phones, lighting and high-end cameras have emerged. According to SUSS MicroOptics, the goal is to enable volume manufacturing from pilot production all the way to high-volume production in Europe and in particular in Neuchâtel.

Neuchâtel was chosen as the location because of the city's long-standing connection with the high-end watch industry and its role in transforming expensive, low-volume technologies to higher volumes, keeping high quality standards while reducing costs.

CSEM, a Research Technology Organisation (RTO), has traditionally been the link between R&D lines and user applications. Rolando Ferrini, Section Head MicroNano Optics & Photonics at CSEM has been appointed in charge of linking wafer-level R&D lines to volume manufacturing. As he says: "finding synergies between the huge technological developments in wafer-level micro-optics, which have happened in Europe in the last decade, mostly funded by European H2020 grants and regional funds, positions today Europe as a leader in bringing freeform micro-optics to higher volumes: it is now or never to create volume manufacturing capabilities in Europe in this strategic field, which is foreseen to have strong impact in several application domains."

The SUSS Excellence Centre will use SUSS MicroTec's manufacturing equipment to provide manufacturing services which can be scaled up to contract manufacturing. SUSS MicroOptics CEO, Reinhard Völkel says: "the best way of bringing high-quality freeform micro-optics in applications such as microlens arrays for cameras, is to prove the pilot production of such micro-optics in Neuchâtel and other locations in Europe.

The goal must be to convince highvolume companies that they can start pilot production with us and scale to volume production either by licensing or by replicating SUSS's production process in their own facilities by using European equipment. This is key for European innovation and most importantly for the smart use of R&D innovation funds"

news review

## JEDEC WBG committee publishes first document

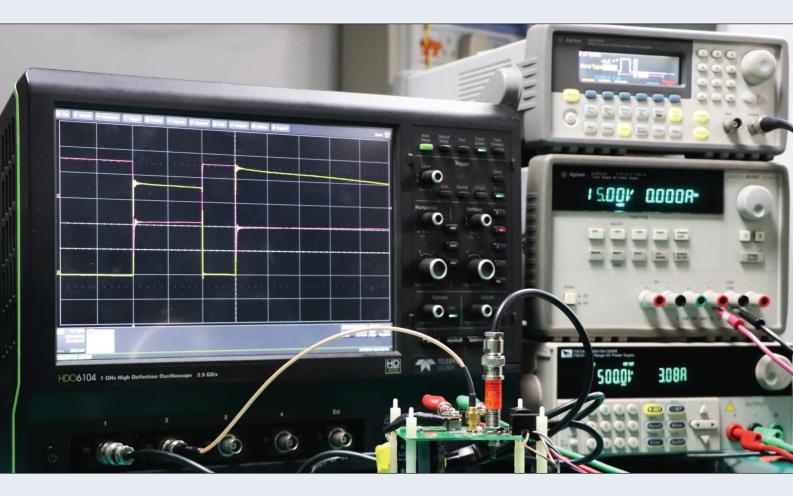

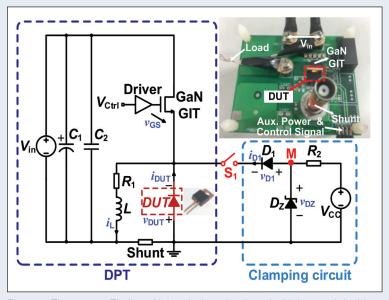

JEDEC Solid State Technology Association, a standards development organisation for the microelectronics industry, has published JEP173: Dynamic On-Resistance Test Method Guidelines for GaN HEMT Based Power Conversion Devices. This is the first publication developed by JEDEC's newest main committee, JC-70 Wide Bandgap Power Electronic Conversion Semiconductors.

The document is available for free download from the JEDEC website. JEP173 addresses a key need of the user community of GaN power FETs, namely a method for the consistent measurement of Drain-to-Source Resistance in the ON-state ( $R_{DS(ON)}$ ) encompassing dynamic effects. These dynamic effects are characteristic of GaN power FETs, and the value of the resulting measured ( $R_{DS(ON)}$ ) is method dependent.

"JEP173 demonstrates how quickly

the GaN industry came together to address this important topic and begin to establish standards across suppliers for datasheet, qualification, and test methods," noted Stephanie Watts Butler, technology innovation architect at Texas Instruments and the chair of JC-70. "The release of JEP173 will help accelerate industry-wide adoption of GaN by ensuring consistency across the supplier base."

Formed in October 2017 with twentythree member companies, JC-70 now has over fifty member companies, which underscores industry interest in the development of universal standards to help advance the adoption of wide bandgap (WBG) power technologies.

Global multinational corporations and technology startups from the US, Europe, Middle East, and Asia are working together to bring to the industry a set of standards for reliability, testing, and parametrics of WBG power semiconductors. Committee members include industry leaders in power GaN and SiC semiconductors, as well as prospective users of wide bandgap power devices, and test and measurement equipment suppliers. Technical experts from universities and national labs also provided inputs into the new JEP173 guideline.

"Strong commitment from the committee members was required to complete this work to set up universal standards to help advance the adoption of wide bandgap (WBG) power technologies." remarked Tim McDonald, senior advisor to Infineon's CoolGaN programme and the chair of the JC-70.1 subcommittee. "Our Task Groups are diligently making progress on other key GaN and SiC guidelines in the areas of test, reliability, and datasheets."

# **Glo on cusp** of commercialization

A smart watch made from Glo's micro-LEDs could be on your wrist very soon, reports Rebecca Pool.

THEY'VE BEEN QUITE A WHILE coming but later this year, smart watches with microLED displays, manufactured by Glo, should be commercially available.

Based on red, green and blue microLEDs, Glo's prototype wearable display measures 1.5 inches in the diagonal and packs in 264 pixels per inch. Crucially, the 20  $\mu$ m InGaN microLEDs deliver extraordinary clarity on the same low-temperature polycrystalline silicon backplane used in liquid crystal and organic light emitting diode displays.

And while today's OLED displays produce a brightness of 1000 nits, Glo's display generates a dazzling 4000 nits, draws less than 1 W of power, and combines a wide colour gamut with a 120 Hz refresh rate.

"Our displays deliver ten times more brightness and five times more power efficiency than an OLED display," highlights Glo chief executive, Fariba Danesh.

"We are working with our manufacturing partners to launch in the latter half of this year, and we feel very confident and comfortable with this," adds Glo executive chairman, Aniruddha Nazre.

Since spinning out from Sweden-based Lund University back in 2005, Glo has attracted more than US\$150 million in funds from numerous investors including pan-European venture capital firm, Wellington Partners, Sweden-based Foundation Asset Management and most notably, Google Inc.

As Danesh points out, the company now comprises 65 employees, the majority of which are technologists, and many with in-depth experience in compound semiconductors. Since the Google cash injection – the tech giant took a 13 percent stake in Glo – employees have been focused on producing devices, especially the smart watch, on low-temperature polycrystalline silicon (LTPS) backplanes.

"If the microLED display is to compete with OLED displays, it really has to leverage the existing LTPS backplane infrastructure," says Nazre. "So we've been working with the major suppliers of these backplanes and have a manufacturing agreement in place, with a second following soon." Crucially, Glo's microLEDs, operate efficiently at very low currents – they are one-hundredth of that of typical LEDs. Operating at these microamp currents makes Glo's devices suitable for use with displays that are driven by transistors on LTPS glass substrates, as well as CMOS substrates. Indeed, as Nazre emphasises, Glo is, right now, the only company making microLED displays using off-the-shelf commercial LTPS backplanes.

At the same time, the company has also been scaling LED manufacture of its red, green and blue microLEDs. As Nazre puts it: "Customers will want half a million, a million, five million or even more watches; if you cannot solve the capacity problem for them they will never touch you and commercialisation will always just be a pipe dream."

To this end, Glo's microLEDs have, from word go, been designed with standard LED equipment at the company's pilot line in Sunnyvale, California. As a result, Danesh reckons the company can 'import' its processes into a high-volume LED facility very easily.

"Go into any LED shop and you will see that, in essence, they have the same tools as us; our focus has been to not customise anything that could create difficulties when scaling," she says.

"Factor in that we can also use the backplane that is available in the market at high volumes and then you can see that we have a very simple supply chain."

At the same time, Glo has used GaN to fabricate all of its microLEDs – red, green and blue – simplifying the display circuitry. And as Danesh asserts, device cost structures are good, relative to OLED displays.

"We don't use these complex OLED lines, giving us significantly better costs," says the chief executive.

"We have been able to leverage the existing economies of scale that are available to the display companies," she adds. "We really have opened a door for them to create new technologies that can compete with existing OLEDs while using their existing infrastructure, and this is also a huge opportunity for them."

### news analysis

Still, microLED displays have been notoriously difficult to manufacture using traditional pick-and-place transfer processes, in which each sub-pixel is placed onto a backplane one at a time. To counter this, many companies have been developing mass transfer processes, including Glo. The company's scaleable, direct-wafer-transfer process allows it to manufacture 0.1-inch to 75-inch displays with resolutions up to 3000 ppi on both LTPS and CMOS backplanes.

Indeed, as well as its 1.5 inch wearable display, Glo has also showcased a 0.7 inch 1000 ppi red, green and blue display for artificial reality and head-up displays on a CMOS backplane. And the company has produced displays, more than 8-inch in the diagonal, with up to 200 ppi for tablets, laptops, wall displays and more.

"One of the differences with our 'mass transfer' process, compared to other processes out there, is that we use a completely selective direct wafer transfer," says Nazre. "So you can transfer the microLEDs from the wafers onto the backplane without using any intermediaries, and you can do this selectively."

"This is unique and we have been doing it successfully for two years and counting on both silicon and glass substrates," he adds.

Glo, alongside the likes of Sony and Samsung, will construct its larger displays from 'tiles' of microLEDs. But according to

Danesh, thanks to the high precision of the company's mass transfer process, the so-called stitch lines between tiles that plague this modular approach aren't visible to the naked eye. "One of the challenges of tiling is these stitch lines which you just don't want to see," she says. "With Samsung's tiles, you can see these lines if you stand close enough, but using our process, the stitch lines are not even visible under 50X magnification."

So with the microLEDs and the mass transfer process in place, where next for Glo? Success would seem to be the way forward.

Given the much anticipated demand in the smart watch market, as well as head-up displays, industry analyst, Boris Kobrin from n-tech Research, recently predicted that the global microLED market will swell from \$2.7 billion in revenue in 2019, to a hefty \$10.7 billion in 2022. And while competition from the likes of Apple with Luxvue, Aledia, Sony, Samsung Electronics and many more is rising, Glo's leaders are not fazed.

As Danesh and Nazre point out, Glo has both the InGaN microLEDs and mass transfer process in place, unlike many rival companies, and is set to produce bright, stable displays that can scale in size and production volumes.

"Like everyone else, we think we're smarter than the rest," says Danesh. "But we've met the [key] technical challenges that allow us to make displays at a much larger scale than anyone else that we know."

### news analysis

# **Wolfspeed:** From strength to strength

Since joining Cree, chief executive, Gregg Lowe has bolstered its power and RF business beyond belief. Where next for Wolfspeed, asks Rebecca Pool? When Gregg Lowe joined Cree as chief executive in September 2017, he decided to make more of Wolfspeed.

At the time, the power and RF subsidiary was still smarting from its failed sale to Infineon, while at \$220 million, yearly revenues paled compared to the incomes of \$700 million and \$550 million from Lighting and LED businesses.

Fast forward to 2019, and Cree has reported stronger than expected financial results, driven by revenue growth from Wolfspeed. The company has also acquired Infineon's RF business and announced a \$250 million SiC wafer supply agreement with STMicroelectronics.

As Lowe tells *Compound Semiconductor*: "Our entire Wolfspeed business was worth a little over \$200 million in 2017 and here we are now, announcing a deal that's actually bigger than that."

"When I arrived at Cree, we re-evaluated strategy and looked for the company's key differentiators," he adds. "Thanks to its SiC and GaN capability, Wolfspeed nailed it. We set out to quadruple Wolfspeed revenues to \$850 million by 2022, and we are well on the way to achieving this ambitious goal."

Lowe's confidence in Wolfspeed is linked to the huge

### news analysis

potential for silicon carbide growth in key markets. Demand for SiC inverters in photovoltaics is gaining traction while the use of SiC in, say megahertz switching, is set to prove instrumental to the rollout of 5G infrastructure.

But for the Cree chief executive, electric vehicles is where the real excitement lies. "In terms of growth, the electric vehicle market is exploding right now," he says.

Lowe reckons that since joining Cree, he has seen car manufacturers such as Volvo, BMW, GM and Toyota invest more than \$170 billion in electric vehicles, with SiC destined for inverters, onboard chargers and charging stations.

"I feel that SiC has hit the perfect window here and in terms of power electronics adoption, the tipping point has really happened," he says.

### Facing challenges

But high wafers costs and limited supply remain key hurdles to SiC adoption. Right now the cost of a SiC wafer is at least double that of a silicon wafer, a thorny issue that is only exacerbated by capacity constraints.

Still, industry players have been tackling problems head on. For example, Infineon recently bought Germany-based Siltectra, which has devised a technology to split SiC wafers and double the number of chips produced from one wafer. Meanwhile, SiC wafer supplier, II-VI has expanded capacity, and Dow has revealed similar intentions.

For its part, Cree has been scaling capacity accordingly. In February 2018, the company started to divert research and development, and capital expenditures from its Lighting and LED businesses to Wolfspeed, and capacity has more than doubled since this time.

What's more, long-term supply agreements with Infineon, an unnamed partner, and now STMicroelectronics, will also help. As Lowe says: "I am pretty bullish that we will double capacity again within the next two years, and one of the ways that we are doing this is through long-term supply agreements."

"These give us the capability to invest more capital in our business," he explains. "We've [secured] three agreements and have a number of others that we are working on that we'll hopefully announce soon."

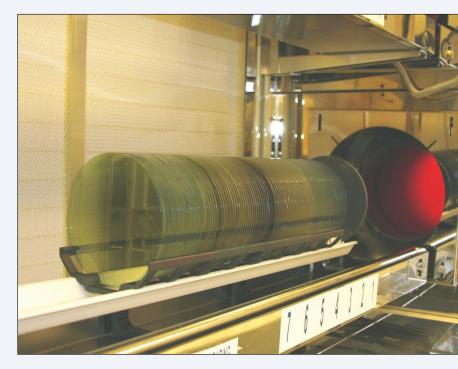

Currently, industry players are also transitioning from 4-inch to 6-inch SiC wafer manufacturing, with an eventual shift to 8-inch manufacturing necessary to optimise output and yields. In the past, such a transition has caused short-term shortages, but according to Lowe, his company's shift from 4-inch to 6-inch wafers has been 'fantastic' with every issue tackled without any major set-backs. "When you are doubling capacity there is much that can go wrong, but the wafer quality on our 150 mm wafers is excellent and that's from customer feedback," he says. "Our doubling in capacity has also given us more feedback on the quality of crystal growth, which we are using to improve the entire fleet and raise yields."

"Our increase in capacity also gives us a better cost base as we have more scale," he adds. "We have chosen to drive costs and yields very hard to decrease the price differential between silicon and SiC, in order to increase market adoption, and we will continue to do this over the coming years," he adds.

So where next for Wolfspeed? Without a doubt, the competition for SiC market share is increasing with other key players, including Infineon, STMicro, Rohm and ON Semi, all striving to fulfil growing market demands.

Still, as Lowe highlights, Cree grows crystals, produces wafers and performs epitaxy, giving it a 'unique advantage' in the market.

"We are fostering the adoption of SiC in the marketplace by providing materials to ST and Infineon, the folks that we effectively compete against in chip and power MOSFET markets," he says. "But this market could be worth many billions of dollars, so there is plenty of room for a number of semiconductor businesses converting from silicon to silicon carbide."

"This is the first time I've been at the heart of such a dramatic industry transition and it's so exciting to be a part of this," he adds. "We're converting an entire industry; how cool is that?"

Wolfspeed has doubled its silicon carbide production capacity by moving from 100 mm wafers to 150 mm wafers

### **CONFERENCE 26-27 MARCH 2019** Sheraton Airport Hotel Brussels

Connecting, informing and inspiring the compound semiconductor industry

# CS INTERNATIONAL 2019 CONFERENCE SPEAKERS ANNOUNCED!

With over 40 presentations and a record breaking number of sponsors, the ninth CS International is set to be the biggest and best yet!

# **Book your place NOW!**

www.cs-international.net/register to secure your place It's set to be another sellout

To be held again at the Sheraton Airport Hotel in Brussels on 26 - 27 March 2019, CS International will once more prove to be the must-attend event for the global compound semiconductor community.

Delivering over 40 talks CS International will provide comprehensive coverage of the global semiconductor industry exploring 5 key themes

- Propelling the power electronics revolution

- Pushing the performance envelope

- Speeding communication

- Opportunities for LEDs and lasers

- Targeting Transportation

Each theme includes talks given by the leading decision makers and influencers within the industry.

# This two day event

### Covers FIVE Themes (Speakers announced to date)

### PROPELLING THE POWER ELECTRONICS REVOLUTION Sponsored by ClossOn How can the manufacture of SiC devices evolve, so that they capture a greater share TECHNOLOGY of the power electronics market? And what are the opportunities for the GaN-on-silicon HEMT? SPEAKERS • Farid Medjoub – IEMN Increasing the blocking voltage of GaN HEMTs - KEYNOTE • Richard Eden – IHS Markit Is the infrastructure in place to ramp SiC and GaN production? - ANALYST O Ralf Lerner – X Fab Printing GaN HEMTs onto silicon CMOS O Cem Basceri – Qromis 200mm GaN Power: Technology and Commercialization Status on QST Platform O Mohammed Alomari – IMS Chips Enabling GaN/Si in an Industry 4.0 environment O Torsten Stoll – Nanometrics Process control solutions for maximum yield in HVM for SiC and GaN power devices • Thomas Uhrmann – EV Group Direct wafer bonding for GaN devices • Ke Xu – Suzhou Nanowin Science & Technology Bulk GaN substrate growth by HVPE technology for GaN-on-GaN devices • Rob Rhoades – Revasum Presentation Title TBC O Julie Orlando – Nanotronics Presentation Title TBC

### **OPPORTUNITIES FOR LEDS AND LASERS**

Can the MicroLED make an impact? And what are the emerging markets for visible lasers

**SPEAKERS**

- Masahiro Murayama Sony [KEYNOTE] Watt-class blue and green lasers

- Pars Mukish Yole Développement [ANALYST] 3D Imaging/Sensing: The next killer application for laser diodes?

- Hiromi Fujita Asahi Kasei Antimonide LEDs for gas sensing

- Mark McKee Veeco

Accelerating Photonics growth through advances in High Performance As/P MOCVD and Wet Processing technology

Liyang Zhang Enkris Semiconductor

- Mastering the manufacture of microLEDs on silicon

- Norbert Lichtenstein II-VI Incorporated The tremendous opportunities for the VCSEL

- Babu Dayal Padullaparthi Sanan IC Semiconductor lasers and detectors for DCI, 5G Front-haul, 3D Sensing & beyond

- Joe Wu Sino Nitride Semiconductor The fabrication of high quality low cost free-standing GaN substrates and GaN templates

Sponsored by

INSPECTROLOG

### SPEEDING COMMUNICATION

Are faster lasers going to lead us into a new era of communication? Or will it be the build out of 5G?

### **SPEAKERS**

- Roger Hall Qorvo [KEYNOTE] Pushing Performance in RF for 5G Networks

- Eric Higham Strategy Analytics [ANALYST] More data: More wireless or more fibre

- Valery Tolstikhin Intengent Fabless PICs in InP: Why, What, and How?

- David Danzilio WIN Semiconductors GaN-on-SiC Technologies for 5G Radio Access

- Edward Wasige EU Project-IBROW Project Mm-wave/THz Multi-Gigabit Wireless Links – the iBROW Project

- Gong Xiao National University of Singapore/MIT Alliance Targeting mm-wave communications with wafer-level integration of InGaAs HEMTs and silicon CMOS

Mikko Soderlund – Beneq

- ALD for Compound Semi Power and RF industrial applications

PUSHING THE PERFORMANCE ENVELOPE Sponsored by PFL Where will heterogeneous integration take us? And how can we extract the ultimate performance out of wide bandgap semiconductors? **SPEAKERS** O Bernardette Kunert – imec III/V Nano-ridge Engineering for novel Device Integration on Si [KEYNOTE] O Remy Comyn – Knowmade Innovators in Power SiC - [ANALYST] • Gabriele Formicone – Integra Increasing the Power of Solid-State RF Amplifiers O Marco Malinverni – Exalos Superior superluminescent LEDs O Markus Behet – EpiGaN GaN on Si – A Key enabling technology for 5G O Andy Sellars – Compound Semiconductor Applications CATAPULT Accelerating the commercial application of compound semiconductors • Gerald Klug – DISCO HI-TEC EUROPE Laser-lift-off (LLO) and CONDOx for wafer ultra-thinning process f or 3D stacked devices, TSV, eWLB and WLCSP wafers O David Lishan – Plasma-Therm Extending performance in advanced packaging with low temperature, low damage plasma technologies O Jens Voigt – AIXTRON Enabling Global Mega Trends with Compound Semiconductors **O** John Ghekiere – ClassOne Advancing Performance of Compound Semiconductor Devices Through Advanced Plating Processes O Mukundkrishna Raghunathan – KLA Corporation Presentation Title TBC

### TARGETING TRANSPORTATION

Can the strengths of SiC drive its adoption in electric vehicles? And what are the opportunities for III-V optoelectronics in the cars of today and tomorrow?

### **SPEAKERS**

- Aly Mashaly Rohm Semiconductor [KEYNOTE] Giving Formula E racing cars an edge

- Hong Lin Yole Développement [ANALYST] SiC and GaN adoption by EV/HEV market

All speakers and presentations are subject to change. ©2019 Angel Business Communications Ltd.

PLATINUM SPONSORS

SEPIC

European Photonics Industry Consortium

# Drawing the heat with diamond

Sucking the heat out of a GaN transistor with diamond film is to become ever more common, thanks to a strengthening supply chain for this technology

### **RICHARD STEVENSON REPORTS**

DIAMOND has many fine attributes. It is renowned for its brilliance, which makes it a very fine choice for making jewellery; and it is blessed with great hardness, allowing it to be used in tools for cutting, drilling and sawing, and on the tip of cantilevers, to trace the modulations in vinyl records.

Lesser known, but equally exceptional, is diamond's thermal conductivity. Thanks to strong covalent bonds and low phonon scattering, its conductivity is around 2000 W m<sup>-1</sup> K<sup>-1</sup>, a value five times that of copper.

This incredibly high conductivity has piqued the interest of the electronic community, which has been investigating diamond's capability for extracting the heat out of a GaN HEMT. Efforts in this direction can be traced back to 2003, with the first successful attempt to produce a GaN-on-diamond structure. Milestones since then include the first GaN-on-diamond transistor in 2006, and DARPA's Near Junction Thermal Transport (NJTT) programme, kicked off in 2011, that has aided the development of this technology.

Recently, further strides have been made that put in place the groundwork to support the commercialisation of GaN-on-diamond technology. Several companies are now playing a significant role in this fledgling industry, with many in attendance at Diamond D-day, a one day conference held in Bristol, UK, towards the end of January. Those at this gathering, organised by Martin Kuball from the University of Bristol, included suppliers of tools for depositing diamond, providers of GaN-on-diamond epiwafers and foundry services, and makers of devices.

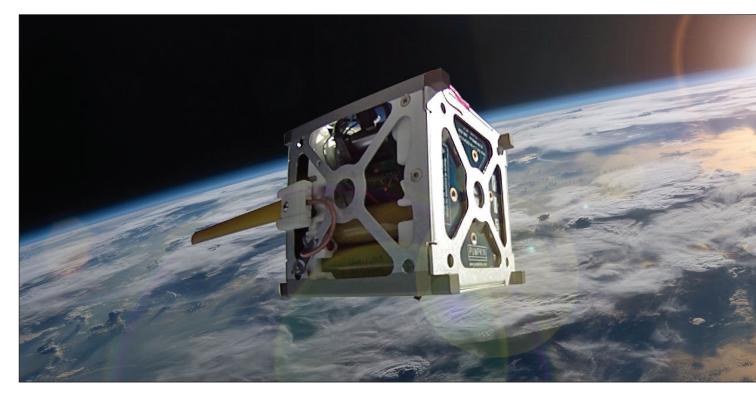

#### Up in space

One of the pioneers of the GaN-on-diamond HEMT is Akash Systems. This outfit, based in San Francisco, CA, devotes its efforts to developing small satellites, satellite transmitters, and the RF power amplifiers that serve them.

Speaking on behalf of Akash, the company's vice president of materials, Daniel Francis, began his talk by claiming that diamond is a satellite's best friend. He argued that the addition of a diamond foundation produces a three-fold hike in power density, and a considerable reduction in operating temperature. He cited work by the Air Force Research Laboratory, showing that the addition of a diamond layer reduced the channel temperature by between 40 percent and 50 percent, compared with GaN-on-silicon and GaNon-SiC devices.

That reduction is a big deal. Note that the rays of the sun can propel satellite temperatures to as high  $180 \,^{\circ}\text{C}$  – and radiation is the only option for dissipating heat, so it is crucial to get as much of it as possible out of the device.

Akash is producing its GaN-on-diamond devices from 4-inch wafers. "If it's not full wafer, it's not production," said Francis.

He outlined three potential options for forming GaNon-diamond structures. One is to grow GaN layers directly on diamond, but this requires the use of intermediate layers, and is ruled out by the relatively small the size of the diamond substrate. Another option is bonding, but a 'glue' is needed to bond the GaN and the diamond. Amorphous SiN is a popular choice,

but it has a thermal conductivity of just 1 W m<sup>-1</sup> K<sup>1</sup>, compromising the benefits of the diamond layer.

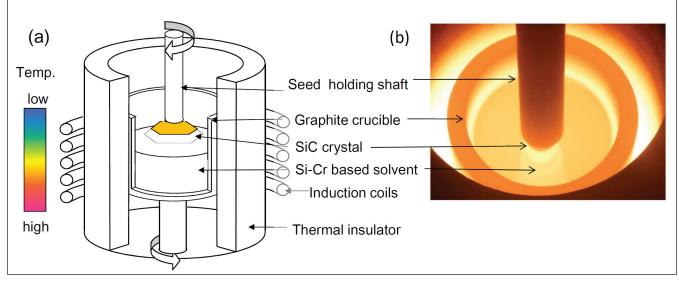

The third way, pursued by Akash, is to grow diamond on GaN-based epistructures. Engineers at the westcoast firm start with GaN-on-silicon epiwafers with a SiN transition layer – it is less than 35 nm-thick, has a conductivity of around 10 W m<sup>-1</sup> K<sup>-1</sup>, and provides a good dielectric interface. Fabrication of devices involves separating the epilayers from the silicon substrate.

Efforts associated with improving production have led to a greater consistency associated with removal of the AlGaN buffer, better control of the thickness of the adhesion layer – it is now controlled to within 5 nm – and a reduction in wafer bow to less than 20  $\mu$ m.

Engineers target a thickness for the diamond layer of 125  $\mu$ m. To ensure that they realise this, they deposit more material, and then apply a polishing step to thin

the diamond to the required thickness.

Francis revealed that when the growth of diamond begins, it can create nanocrystals, which have a low thermal conductivity. But as growth continues, grains get larger, increasing thermal conductivity.

Capacitance-voltage measurements on the processed wafers reveal a "low, flat capacitance". This is attributed to low interface charging. Plots are much closer to those for GaN-on-SiC, than for GaN-on-silicon.

Results on recent multi-finger devices reveal a poweradded efficiency of around 60 percent. According to Francis, this figure is comparable to that of standard devices operating at 10 GHz.

### GaN-on-diamond epiwafers

If developers of GaN-on-diamond devices prefer to start their fabrication work with epiwafers of this

The Diamond D-day conference, held at the Bristol Mari ot Hotel, attracted 120 delegates. About half of those that attended came from overseas. material, they have the option of buying 4-inch material from RFHIC.

At Diamond D-Day, RFHIC's Director and General Manager, US, Won Sang Lee, began his presentation by claiming that the market for epiwafers of GaN-on-SiC HEMTs is "strong". But he believes that GaN-ondiamond will be "the next step".

RFHIC wants to be the pioneer of the GaN-ondiamond semiconductor industry. It is well-placed, having 63 patents associated with this technology, and exclusive intellectual property that is said to cover everything except the commercial satellite sector. The company has identified several potential markets for GaN-on-diamond, including self-driving cars, military radar, and industrial, medical and scientific sectors.

Lee compared what he considers to be the three main technologies for RF, high-power devices: silicon LDMOS, GaN-on-SiC, and GaN-on-diamond. He argued that the it is only the latter that is capable of providing operating frequencies up to 100 GHz, making it the leading candidate for the future.

He predicts that the success of GaN-on-diamond will begin with deployment in 5G base stations. The merits of this material combination are not limited to a substantial power density, but also include: greater linearity, stemming from superior carrier transport; and better reliability, due to the lower operating temperature of the chip.

RHFIC, which started developing its GaN-on-diamond technology back in 2015, is now capable of producing GaN-on-diamond material in substantial volumes in Korea, and in smaller quantities at its R&D facility in the US. The plan is to start shipping engineering samples to its customers in the second quarter of this year.

Goals for the future include increasing the production quantity of GaN-on-diamond to 100 epiwafers per month, optimising device layers to improve performance, and increasing yield – currently it's just 40 percent.

### **Device foundry**

One company with the capability to process RHFIC's GaN-on-diamond epiwafers into devices is compound semiconductor foundry service provider GCS. In Bristol Daniel Hou, a spokesman for the company, detailed some of the challenges and the rewards of this approach.

A downside is that in an automated fab, some tools may be unable to handle these epiwafers. This can be caused by tensile strain in the material, leading to a wafer bow of up to a few millimetres. Such a distortion

can wreak havoc with printing processes for i-line steppers. The solution, explained Hou, is to choose a carrier with the right coefficient of thermal expansion. Using a combination of a perforated SiC carrier, dry and wet etching steps, thermal release tape bonding and high-temperature polymer bonding, bow can be slashed to just 20  $\mu$ m.

Hou revealed that another issue is that the implant isolation step can lead to a "huge" leakage current. It rockets by six orders of magnitude.

The engineers at GCS address this hike with an additional step for treating the surface. This results in DC characteristics that are similar to those for GaN-on-silicon: maximum current is 1 A/mm, peak transconductance is 250 mS/mm, breakdown voltage exceeds 100 V, and the on-off ratio is in excess of 10<sup>6</sup>.

RF measurement on these devices are encouraging. Applying a 10 percent duty cycle to  $0.65 \,\mu m$  HEMT, and cranking up the voltage from 50 V to 100 V, produces an increase in the power density at 2 GHz from 15.5 W/mm to 22.5 W/mm.

Efforts at GCS have also been directed at developing a through-substrate via process. This involves: laser drilling from the frontside; plating with gold to partially fill the via; sputtering a seed metal; and then gold plating, both on the front side and the back side.

Multi-finger devices made with this process are capable of producing an output of 11.2 W, and 15-19 dB of gain. Hou describes these results as "respectable", and says they provide proof that the via process is "working".

#### An all-diamond device

With a bandgap of 5.45 eV – that is even higher than that of gallium oxide – diamond can also be viewed as a promising material for making high-power devices.

Some of the results obtained with diamond devices were briefly discussed in a talk given by Andrew Barnes from the European Space Agency. He mentioned transistors with a maximum oscillation frequency of 20 GHz, and a cut-off frequency of about 7.7 GHz. This enabled up to 22 dB of gain, a result Barnes described as "quite encouraging".

However, he warned the audience that diamond has its drawbacks, including being very expensive, and very difficult to dope.

An even stronger case for steering clear of diamond devices came from Oliver Williams from Cardiff University, who said: "I did my PhD on diamond devices and it didn't go well." In his view, *n*-type doping doesn't work, and the diameter of the native substrate is stuck at half an inch, despite promises dating back two decades that 1-inch material is just around the corner.

So, based on the presentations at Diamond D-day, it is best to restrict diamond's role within the compound semiconductor industry to extracting the heat out of the GaN HEMT. Used for this, it can do a great job. And with a strengthening supply chain taking place, there is a good chance that GaN-on-diamond devices will start to see widespread in space, along with increasing deployment in applications far nearer to home. As the small satellite space race takes off, Akash Systems is set to send GaNon-diamond systems into orbit.

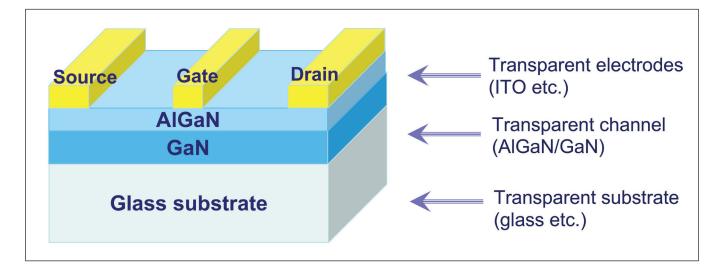

### GaN transparent transistors

# Invisible contacts

Transparent GaN circuits are on the horizon, thanks to transfer processes for shifting the transistors onto glass, and the creation of see-through contacts, based on indium tin oxide and ion implantation

BY ZHIHONG LIU FROM SINGAPORE-MIT ALLIANCE FOR RESEARCH AND TECHNOLOGY, GEOK ING NG FROM NANYANG TECHNOLOGICAL UNIVERSITY AND EUGENE FITZGERALD FROM MASSACHUSETTS INSTITUTE OF TECHNOLOGY

24 WWW.COMPOUNDSEMICONDUCTOR.NET | MARCH 2019 | COPYRIGHT COMPOUND SEMICONDUCTOR

### **N** transparent transistors

EVER MORE EFFORT is being devoted to the development of invisible electronic circuitry and optoelectronic devices. This field, known as either transparent electronics or see-through electronics, promises to spawn many new products and businesses. To name but a few, it could lead to: smart wind shields in automobiles, smart building windows, transparent flat panel displays, and see-through solar cell panels.

A key component in many transparent electronic systems is this transistor. Today, this device is often in the form of a thin-film transistor, made from a transparent conductive oxide, such as  $In_2O_3$ ,  $ZnO_2$  or  $SnO_2$ .

Unfortunately, the performance of those thin-film transistors is vastly inferior to the more common visible transistors, such as the silicon MOSFET. Inferior intrinsic physical properties are to blame, including the polycrystalline structure, lower thermal conductivity, and lower electron mobility – in  $\ln_2O_3$ ,  $ZnO_2$  and  $SnO_2$ , the mobility is typically just 100 cm<sup>2</sup> V<sup>1</sup> s<sup>-1</sup>, one quarter of the value of that of silicon. The low mobility hampers the current that is available to transparent transistors. They are held back by a low current, a low speed, and the need to be driven by a high voltage. What is needed are alternative materials for producing transparent, high-performance devices.

Candidates for replacing the conductive oxides include carbon nanotubes, graphene, and twodimensional transition metal dichalcogenides. But they all have their own weaknesses, which are difficult to overcome in real applications. Carbon nanotubes are held back by agglomeration, dispersion, purification and sorting; graphene is compromised by fabrication issues for yielding high-quality material, and its intrinsic bandgap limit prevents the transistor channel from fully closing; and two-dimensional transition

| Material                       | Bandgap<br>(eV) | Mobility<br>(cm²/Vs) |  |

|--------------------------------|-----------------|----------------------|--|

| In <sub>2</sub> O <sub>3</sub> | 3.75            | ~100                 |  |

| ZnO <sub>2</sub>               | 3.35            | ~100                 |  |

| SnO <sub>2</sub>               | 3.6             | 15                   |  |

| GaN                            | 3.42            | >1500 (2DEG)         |  |

Table I.

Comparison of carrier mobilities in transparent conductive oxides commonly used in GaN and in today's transparent transistors. metal dichalcogenides are impaired by carrier mobilities that are typically even lower than those for transparent conductive oxides.

At the Singapore-MIT Alliance for Research and Technology, we are pioneering a promising alternative: GaN. From an optical perspective, the bandgap of GaN of 3.42 eV is similar to that of the other contenders (for  $\ln_2O_3$ ,  $ZnO_2$  and  $SnO_2$ , values are 3.75 eV, 3.35 eV and 3.6 eV, respectively), giving GaN an absorption wavelength of 362 nm that enables transparency over the whole visible range. And from an electrical performance perspective, GaN wins hands-down. Mobility is more than double that of silicon in the bulk, and four times that in the form of a two-dimensional electron gas. The saturation velocity is also far higher, as is the critical breakdown field and the thermal conductivity.

### Hurdles to a transparent transistor

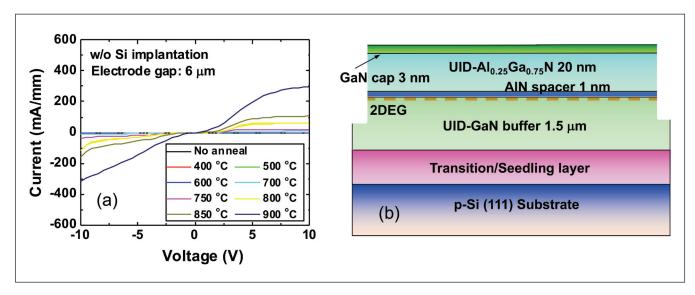

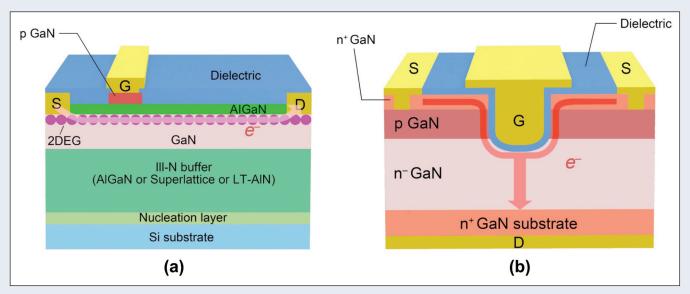

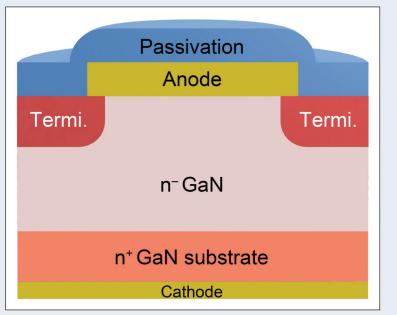

Figure 1. A typical GaN transistor must be modified to form a transparent device. At the heart of a typical GaN transistor is a conducting channel, formed by creating a two-dimensional electron gas at the interface between an AlGaN barrier and the GaN buffer (see Figure 1). This device tends to be produced on a foreign substrate, typically silicon or SiC, and sport three electrodes: a source, a drain and a gate. To ensure transparency, transparent active materials – that is, GaN-based materials – have to be used alongside a transparent substrate and transparent electrodes.

It is not difficult to use a transparent substrate. While a lot of GaN devices are formed by growing nitride layers on an opaque substrate, for example, silicon, there are plenty of transparent options to choose from, including SiC, sapphire, AIN and native bulk GaN. However, all of them are pricey, while the most commonly used substrate for transparent circuits applications – glass – is very cheap.

Our solution is a two-step process that leads to the formation of GaN transistors on glass. Our first step is to deposit GaN materials on a cheap-but-visible silicon substrate, before we transfer the GaN layers onto the glass. Alternatively, we can directly sputter GaN materials on a glass substrate, using a technology developed recently by Hiroshi Fujioka's group at Tokyo University.

What about the electrodes? Normally, GaN transistors have the pairing of nickel and gold as the gate metal, and employ either a Schottky contact or a metaloxide-semiconductor (MOS) structure. To ensure transparency, we can modify this design, moving from these opaque metals to a transparent conductive material, such as indium-tin-oxide, which is widely used in transparent electronics. This oxide is a good choice, as it can form a good Schottky contact to the AlGaN/GaN and work as a gate in a GaN transistor. Encouragingly, there are a few reports demonstrating an indium-tin-oxide (ITO) gate in a GaN transistor, and it has been shown that a MOS structure with ITO can also be employed as a transparent gate in a GaN device.

For the source and drain electrodes, we have to form an ohmic contact between the source and drain material and the channel material. The conventional choice are metals, such as the pairing of titanium and aluminium. Just replacing these opaque materials with ITO is not an option, as the oxide cannot form

Figure 2. (a) A current-voltage (I-V) curve measured for a pattern with two electrodes made of ITO after different annealing temperatures. The plots show that when the annealing temperature is lower than 600 °C, the current is very small and can be neglected. Increasing the temperature to 700 °C causes current to appear, but ohmic contacts cannot form, even with an annealing temperature as high as 900 °C. The nitride materials in this transistor (b) were grown by the epiwafer supplier IQE, by loading a 200 mm *p*-type silicon wafer into an MOCVD chamber.

an ohmic contact with the two-dimensional electron gas (see Figure 2). Note that although upping the annealing temperature increases the current, even at 900 °C, it does not lead to an ohmic contact.

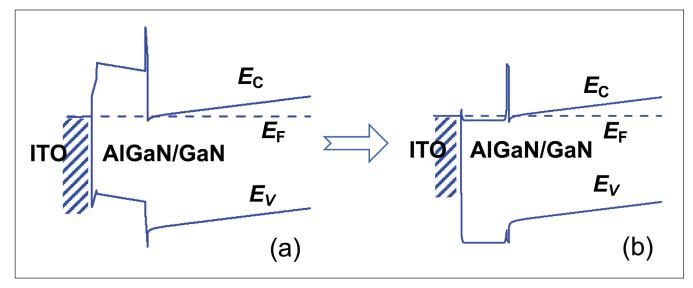

### Transparent ohmic contacts...

Simulations of the energy bands reveal why ITO fails to form a good ohmic contact in a GaN transistor. They show that there is a high energy barrier between the ITO and the two-dimensional electron gas at the interface between AlGaN and GaN (see Figure 3(a)). This barrier prevents electrons from travelling smoothly between the ITO and the triangle well in the GaN – and thus prevents the formation of a good ohmic contact. To make one, an approach is needed that pulls down the conduction band of the AlGaN/ GaN materials close to the ITO and minimizes the energy barrier (see Figure 3(b)).

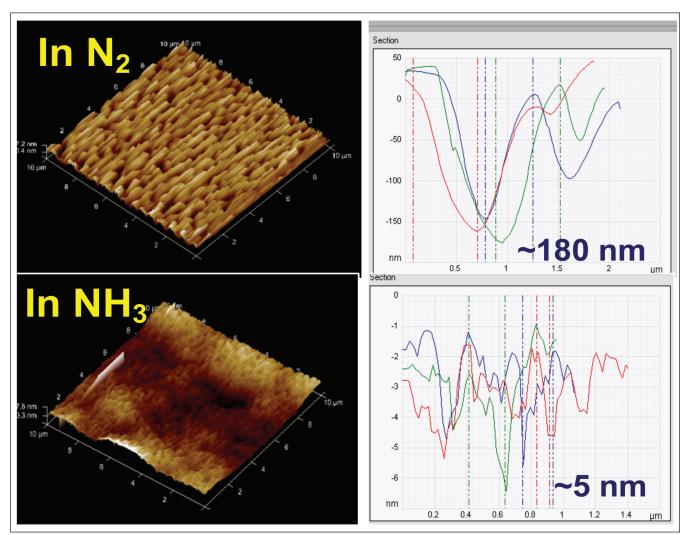

One effective approach to pulling down the electron conduction band is to use ion implantation to dope AlGaN and GaN. We have a lot of experience with this, having optimized ion implantation technology to form highly-doped AlGaN/GaN regions and realize good CMOS-compatible ohmic contacts in GaN transistors. Our efforts include the development of an activation annealing method, using ammonia rather than the more common nitrogen to reduce the surface damage

Figure 3. (a) For the energy band diagram for ITO and the AlGaN/GaN heterostructure, there is a high energy level between the ITO and the two-dimensional electron gas (2DEG) at the interface of AlGaN/GaN heterostructure. (b) To form a good ohmic contact, there is a need to pull down the conduction band of the AlGaN/GaN materials close to the ITO and minimize the energy barrier.

### **GaN** transparent transistors

Figure 4. Activation annealing in ammonia can greatly suppress the surface damage caused by high temperature (1200 °C, 2 minutes)

| Group       | Substrate | R <sub>sh</sub><br>(Ω/□) | R <sub>c</sub><br>(Ω mm) |

|-------------|-----------|--------------------------|--------------------------|

| Mitsubishi  | SiC       | 215                      | 0.28                     |

| Mitsubishi  | SiC       | N.A.                     | 0.16                     |

| UCSB        | SiC       | N.A.                     | 0.2                      |

| Hosei Univ. | sapphire  | 140                      | 0.045                    |

| Our work    | sapphire  | 50                       | 0.07                     |

| Our work    | silicon   | 58                       | 0.07                     |

Table II. Excellent results in both sheet resistance (R<sub>sh</sub>) of the implanted regions and ohmic contact (R<sub>c</sub>) have been achieved using silicon ion implantation and CMOS-compatible (Ti/Al metals) ohmic contact technology developed at the Singapore-MIT Alliance for Research and Technology.

during high-temperature annealing of the GaN transistor surface (see Figure 4). By optimising the ion energy, dosage, activation annealing thermal budget and the post-metal annealing thermal budget, we have realised excellent results for the ohmic contact and the sheet resistance of the implanted regions (see Table II).

More recently, we have transferred these silicon ion implantation techniques to our transparent devices. The implantation conditions that we have adopted are a 30 keV energy, with a  $2 \times 10^{15}$  cm<sup>-2</sup> dosage, plus a 80 keV energy with a  $2 \times 10^{15}$  cm<sup>-2</sup> dosage, at 7° tilt, using a 300 nm layer of SiO<sub>2</sub> as a hard mask for protection. This is deposited by PECVD. We activate the silicon ions by heating to 1200 °C for 5 s in an ammonia atmosphere. The last step is the sputtering of an ITO film, followed by annealing in a nitrogen atmosphere.

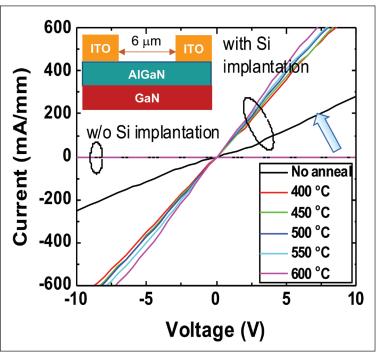

This approach can form good ohmic contacts between the ITO and the silicon-implanted AlGaN/ GaN heterostructure (see Figure 5). Note that good ohmic contacts are even formed when annealing at just 400 °C. Recall that this is in stark contrast to the lack of any current in samples without silicon implantation that are annealed at temperatures below 600 °C (see Figure 6). So there is no doubt that silicon implantation is highly beneficial for the formation of ohmic contacts between ITO and GaN materials.

### ... and working transistors

To test our approach, we have applied our transparent source and drain ohmic contact technology to real GaN transistors, which use the design shown in Figure 1. In these devices, the two-dimensional electron gas Hall density and mobility are about  $8 \times 10^{12}$  cm<sup>2</sup> and 1500-1600 cm<sup>2</sup> V<sup>1</sup>s<sup>-1</sup>, respectively. The ITO ohmic contact is formed with the assistance of silicon ion implantation, followed by annealing under nitrogen for 1 minute at 600 °C.

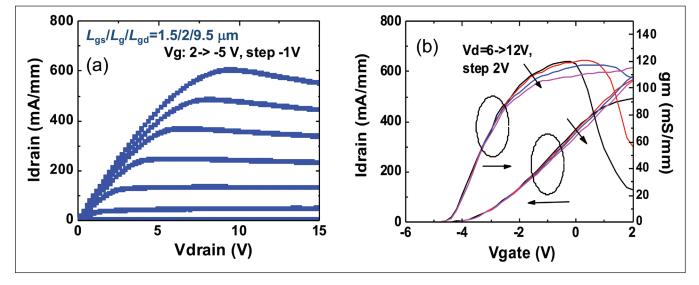

DC tests on our devices show excellent results, highlighting the potential that GaN has to be applied in tomorrow's future transparent electronic systems. Our transistors, which have a gate-to-source distance of 1.5  $\mu$ m, a gate length of 2  $\mu$ m, and a gate-to-drain distance of 9.5  $\mu$ m, exhibit a maximum drain current of 602 mA/mm, a maximum transconductance of 121 mS/mm and a threshold voltage of typically -3.0 V. These values are similar to those found in devices with conventional metal electrodes, indicating that the ITO gate and fabrication process does not introduce obvious extra charges on the device surface. The Schottky barrier height between ITO and AlGaN/GaN

#### **Further reading**

Z. Liu *et al.* Proc. of IWN, 2018

B. Lu *et al.* Electron. Dev. Lett. **31** 951 (2010)

T. Itoh *et al.* Sci. Reports **6** 29500 (2016)

Z. Liu et al. Proc. of IWN, 2016

Figure 5. Good ohmic contacts were formed between ITO and the silicon implanted regions in the AIGaN/GaN heterostructure.

is 0.7 eV, which is a little higher than 0.62 eV, a value reported elsewhere.

Our work underscores the potential of transparent GaN transistors. To spur their development, we will now try to further optimize the transparent ohmic contact and reduce the contact resistance. This should lead to fully transparent GaN transistors with excellent RF or power performance, and ultimately enable the production of GaN transparent circuits and systems.

Figure 6. Measured DC performance including (a) output (b) characteristics of a GaN transistor with ITO source/drain (S/D) and gate electrodes.

### **PICTINTERNATIONAL** CONFERENCE Sheraton Airport Hotel Brussels

Connecting, informing and inspiring the photonic integrated circuits industry

# PIC INTERNATIONAL 2019 CONFERENCE SPEAKERS ANNOUNCED!

With over 30 presentations and a record breaking number of sponsors, the fourth PIC International is set to be the biggest and best yet!

# Book your place NOW!

www.picinternational.net/register to secure your place It's set to be another sellout

To be held again at the Sheraton Airport Hotel in Brussels on 26 -27 March 2019, PIC International will once more prove to be the must-attend event for the global integrated photonic circuits community.

Delivering over 30 talks PIC International will provide comprehensive coverage of the integrated photonics industry exploring 5 key themes

- PICs Today: Datacom, Imaging and Transport

- PIC Innovation: EPDA, TAP & PICs Beyond Datacom

- PICs Reimagined: Hybrids and Materials Innovation

- PIC ROI: Show Me the Money

- PICs Beyond 100G: Evolution and Revolution

Each theme includes talks given by the leading decision makers and influencers within the industry.

# This two day event includes FIVE new themes and two new panel sessions for 2019

### PICS TODAY – DATACOM, IMAGING AND TRANSPORT

Today's primary PIC applications in data centers and telecom are foundations for new opportunities. We will explore PICS for healthcare, diagnostics, imaging/ranging and vehicle automation as well as new approaches for data transport.

### **SPEAKERS**

- Katharine Schmidtke Facebook [KEYNOTE] Achieving high quality 100G data center PIC Integration

- Mehrdad Ziari Infinera

Large scale PICs, integration with InP lasers and PICs across future networks and markets

Michael Liehr AIM Photonics

- AIM Photonics' role in developing next generations of PICs and TAP manufacturing expertise • Pauline Rigby - Lightcounting – [ANALYST]

- New VCSEL opportunities in 3D sensing and beyond

- Henk Bulthuis Kaiam Corporation The future and economics of PICs and PLCs in data center applications

- Callum Littlejohns CORNERSTONE Device prototyping using the CORNERSTONE platform

- Ignazio Piacentini ficonTEC PIC differentiation, emerging markets, and common modular platforms for assembly and test.

- Rene Penning de Vries PhotonDelta Presentation Title TBC

### PIC INNOVATION – EPDA, TAP & PICS BEYOND DATACOM

Electro-photonic design automation (EPDA) paired with automated test, assembly and packaging (TAP) are essential for ensuring rapid PIC development cycles and quality control. We will explore how tools and processes will enable greater yield, reliability and sector growth.

### **SPEAKERS** • Tom Daspit, Mentor ... A Siemens Business Photonics and EDA - Round Hole and Square Pegs • Albert Hasper, PHIX Large scale assembly and packaging foundry for PICs O Scott Jordan, Physik Instrumente The Emergence of Non-Position Positioning in Fast Manufacturing Automation O Martijn Heck - ePIXfab/Aarhus University Presentation Title TBC O Ronald Broeke – BRIGHT Photonics Rethinking the photonics IC design flow to make high-quality PIC design easier, cheaper and faster O David Cheskis - IQE VCSELs in 3D facial recognition Remco Stoffer – Synopsys How Synopsys Is Driving the PIC Revolution with a Trusted and Scalable Design Flow? • André Richter - VPIphotonics Hybrid PICs - Technology Alternatives and Design Implications James Pond - Lumerical Scalable PIC design: increasing yield of components, circuits and systems Luc Augustin – SMART Photonics Open access integration platform: versatile solution for photonic integrated circuits Peter O'Brien – Tyndall National Institute Presentation Title TBC • Pieter Dumon – Luceda Photonics Presentation Title TBC

### PICS REIMAGINED – HYBRIDS AND MATERIALS INNOVATION

PIC innovation is already linked to hybrids – InP lasers are driven by silicon chips and die-level devices are combined into modules. While silicon photonic (SiP) optimization continues we will concurrently explore the benefits of bringing compound semiconductor technologies such as GaAs, GaN, lithium niobate, and silicon carbide into PIC development programs.

### **SPEAKERS**

- O Jochen Zimmer Nanoscribe

- Additive manufacturing by two-photon-polymerization for photonic integration • Arne Leinse – LioniX International

- Vertical Integration in Silicon Nitride (siN) based foundry enables new applications

Michael Geiselmann LIGENTEC

- New advances in Silicon Nitride (siN) PIC Applications

- Arnaud Rigny Teem Photonics

Optical passive device platform to enhance photonics performances

Di Liang Hewlett Packard Enterprise

- Presentation Title TBC

- Michael Lebby Lightwave Logic Polymer PIC opportunities in Applications Beyond 100G

Kei May Lau – Hong Kong University of Science & Technology

- III-V lasers directly grown on Silicon

- Other speaker presentation themes to be confirmed include:

- Multiphoton Optics

TBC