Volume 35 Issue 1 2013

**Digital power** market forecast 🔁 @siliconsemi

www.siliconsemiconductor.net

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

New european thrust

## The race is on to replace silicon with InGaAs

Silicon's crown is under threat

Features, News Review, Industry Analysis, Research News and much more. Free Weekly E News round up, go to www.siliconsemiconductor.net

28<sup>29</sup> **30** 1 26 **25**

25

20

19 18 17 16 15 14 <sup>13</sup>

duntenturturturt

24

23

22

21

20

ź з 4 5

5

6

7

8

9

10

1211

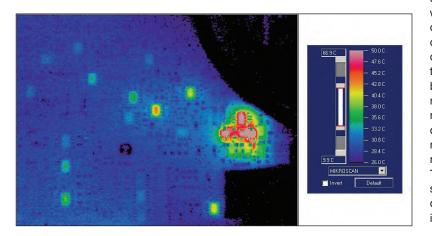

## Optimize the Thermal Performance of your Process Equipment.

Extensive computational tools enable product designs to be highly refined for ultimate performance.

Multi-zone circuit layouts in a polyimide construction are highly customized to deliver exacting performance up to 250°C.

EZ-ZONE<sup>®</sup> RM Multiloop controllers are fully scalable with up to 152 PID Loops and 256 monitor points per system. Washing at low provides innovative solutions to help process tool manufacturers meet the needs of the semiconductor technology roadmap. Our approach is to work collaboratively to help solve complex thermal challenges associated with state-of-theart manufacturing processes; helping to improve yield, throughput and cost of ownership. This includes innovative heaters, controllers and sensors for use in front-end and back-end applications such as CVD, PECVD, Etch, Diffusion, Bonding, IC test and more.

WATLO

ASSURANT<sup>™</sup> gas and pump line heaters feature high temperature capabilities with low outgassing.

## Contact Watlow<sup>®</sup> today for the latest thermal solutions for semiconductor applications.

| Europear | Technical Sales Offices               | Italy |

|----------|---------------------------------------|-------|

| Germany  | +49 (0) 7253-9400-0<br>info@watlow.de | Spain |

| France   | +33 1 41 32 79 70<br>info@watlow.fr   | UK    |

+39 02 4588841 italyinfo@watlow.com +34 91 675 1292 info@watlow.es

+44 (0) 115-964-0777 info@watlow.co.uk

# executiveview

By Jay Shah, Worldwide Marketing Operations, Keithley Instruments, Inc.

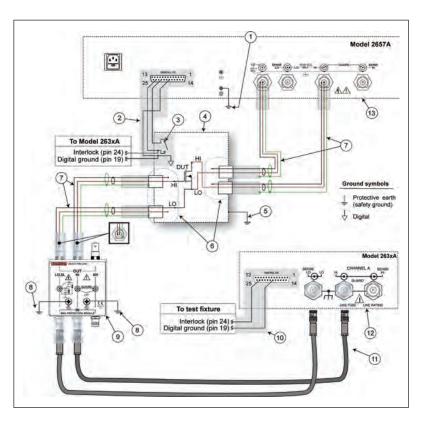

## Capable power semiconductor testing solutions required

Power semiconductors will become more important in 2013 given the burgeoning demand for efficient energy production and management. With fossil fuel prices remaining volatile, there is renewed focus on green energy sources like solar power and wind farms. The demand for efficiency management in motor drivers, lighting, and power supplies is rising, which in turn drives demand for power semiconductor devices. The developers of test and measurement instrumentation have a responsibility to help their customers meet the challenges that come with researching (universities/labs) and building (fabs) the next generation of power devices.

As power semiconductor manufacturers have continued to explore wide-bandgap alternatives to traditional silicon-based devices, testing these devices has become increasingly challenging. Higher voltage ratings, higher peak current ratings, and lower leakage specifications, made possible by the use of silicon carbide (SiC) and gallium nitride (GaN), are complicating design, characterization, and testing.

From a characterization and test perspective, SiC and GaN require far more powerful instrumentation than silicon-based technologies ever did. Devices based on these materials typically have much higher power density, smaller size, better high temperature performance, higher frequency response, lower leakage, and lower ON resistance than their silicon equivalents, all of which add up to greater operating efficiency. They also have far lower leakage than silicon, so at the same time as there is a need for sourcing higher voltages in testing; there is also a need for greater current measurement sensitivity. For all their technical advantages, there are a variety of barriers to the mass adoption of SiC and GaN devices, the most significant of which is price. Making these devices more affordable will depend on manufacturers' ability to improve material quality and processing efficiency, both of which require intensive characterization and testing.

Solutions such as custom systems that attempt to integrate power sources with current measurement instruments simply can't provide the low current accuracy required to characterize next-generation devices and materials. As single-quadrant devices, power supplies cannot sink power; therefore, they require several seconds for the capacitance charge to bleed off after testing, which slows the test process, which is particularly problematic in production applications. In addition, in many cases, they lack the necessary power to support today's operating or characterization levels. Such custom-designed systems also typically require large test engineering teams to develop and maintain them.

Although commercial ATE systems have always been used for power semi production test, their cost, size, and lack of characterization and low current measurement capabilities make them impractical for R&D and QA/FA applications. Curve tracers were once the solution of choice for device characterization, but they are now largely unavailable. Fortunately, a number of T&M innovators, including Keithley Instruments, have begun applying the integrated sourcing and measurement capabilities of high-power SMU (source measure unit) instruments to this challenge.

| News Editor Dr. Su Westwater                      | suwestwater@angelbc.co.uk  | Subscriptions Manager Debbie Higham                                                    | debbie.higham@angelbc.com                  |  |

|---------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------|--------------------------------------------|--|

| Director of SOLAR & SEMI Publishing Jackie Cannon | jackie.cannon@angelbc.com  |                                                                                        | +44 (0)1923 690220                         |  |

| Ũ                                                 | +44 (0)1923 690205         | Chief Operating Officer Stephen Whitehurst                                             | stephen.whitehurst@angelbc.com             |  |

| Senior Sales Executive Robin Halder               | robin.halder@angelbc.com   |                                                                                        | +44 (0)2476 718970                         |  |

|                                                   | +44 (0)2476 718109         | Directors Bill Dunlop Uprichard - CEO, Stephen Whitehurst - COO, Jan Smoothy - CFO,    |                                            |  |

| Sales Manager Shehzad Munshi                      | shehzad.munshi@angelbc.com | Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal                                |                                            |  |

|                                                   | +44 (0)1923 690215         |                                                                                        |                                            |  |

| USA Representatives Tom Brun Brun Media           | E: tbrun@brunmedia.com     | Published by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road,       |                                            |  |

|                                                   | Tel: 724 539-2404          | Watford, Herts WD17 1JA, UK.                                                           |                                            |  |

| Janice Jenkins                                    | E: jjenkins@brunmedia.com  | T: +44 (0)1923 690200 F: +44 (0)1923 690201 E: ask@angelbc.com                         |                                            |  |

|                                                   | Tel: 724-929-3550          |                                                                                        |                                            |  |

| Director of Logistics Sharon Cowley               | sharon.cowley@angelbc.com  | Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, |                                            |  |

|                                                   | +44 (0)1923 690200         | Coventry CV5 6SP, UK.                                                                  |                                            |  |

| Design & Production Manager Mitchell Gaynor       | mitch.gaynor@angelbc.com   | T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@ang                              | elbc.com                                   |  |

|                                                   | +44 (0)1923 690214         |                                                                                        |                                            |  |

| Circulation Director Jan Smoothy                  | jan.smoothy@angelbc.com    | Angel 🕢 DDA Corecy                                                                     | <i>r</i> cle                               |  |

|                                                   | +44 (0)1923 690200         |                                                                                        | ave finished with<br>ne please recycle it. |  |

Silicon Semiconductor is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright orensights in a subsequent issue of the publication. Angel Business Communications Ltd will be happy to acknowledge any copyright consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor (ISSN 1096-598X) is published four times a year for a subscription of \$198 by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Hers WD17 1JA, UK. Periodicals postage paid at Rahway, NJ. POSTMASTER: send address changes to: Silicon Semiconductor, c/o Mercury International Ltd, 365 Blair Road, Avenel, NJ 07001. Printed by: Pensord Press. @ Copyright 2013. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online).

## Features

# **27** "Airbus for chips" could take European chip industry to the future

The semiconductor industry is fighting an uphill battle against the forces of the globalization: could the concept of an "Airbus for chips" generate new thrust?

## **30** Design challenges of high voltage instrument development

Designing an instrument capable of measuring very low currents and having an output stage capable of producing 3000V is extremely challenging.

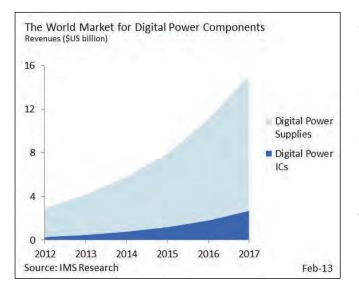

## **34** Digital power market forecast to quadruple in five years

The digital power market is currently one of the fastest growing segments of the power management industry for power supply and power IC manufacturers. IMS Research – now part of IHS offers an analysis of the digital power market.

37

## Driving innovation

"If I'd asked my customers what they wanted, they would have said a faster horse." – Henry Ford. This quote from the automotive pioneer is bound to stir debate about how companies should approach the innovation process.

### **Research News**

- I 2 The race is on to replace silicon with InGaAs

- 14 Chips steer light in the right direction

- 17 Germanium p-Type transistor: highest ever 'carrier mobility'

- **I9** Improving on diamond in supercomputers

- **2** Si-InP sandwich chips combine the best of both worlds

### Industry Analysis

23 SEMI: FAB equipment to rocket 24% in 2014

- 24 IC suppliers to monopolise 300mm wafer space

- **25** Cu pillar and micro-bumping flip-chip invigorate the market

**NEWS: D7** EV Group Ships 300mm wafer bonding system to China **D7** Brewer Science upgrades production for CNT memory devices **D7** imec announce launch of integrated silicon photonics platform **D8** AGC and nMode collaborate **D8** Axcelis wins order from major memory & flash device maker **D9** Infineon's 300mm CoolMOS silicon chips now shipping globally **D9** Martin L. Edelman jumps on board at AMD **I0** Oxford Instruments awarded patent for plasma film deposition **ID** Watlow acquires Semiconductor Tooling Services **ID** Silicon threatens to muscle in on III-V devices

Magazine & Front Cover: Designed by Mitch Gaynor

## THE GAME CHANGER for Semiconductor Manufacturing

## Introducing GF135, the revolutionary new PTI mass flow controller that tests accuracy in real time.

The new GF135 delivers revolutionary technology that will set new standards in semiconductor manufacturing. The GF135 provides smarter functionality with real-time, integrated rate-of-decay flow measurement. Patent-pending flow error detection technology and advanced diagnostics verify accuracy, check valve leak-by and monitor sensor drift – all without stopping your production.

You are no longer limited to flow checks once per month, per day or even per hour. The GF135 can verify flow at every step change or more frequently if desired, so your process keeps running and your wafers meet QA specs.

That means you improve your process yield, uptime and your bottom line. In fact, an increase in wafer yield of only 1% could result in \$60,000 in savings per day!

*Learn what the GF135 performance can do for you. Visit www.BrooksInstrument.com for details.*

High-accuracy PTI-MF real-time critical flo error detection

Application Experience Beyond Measure

12 SP for

# EV Group ships 300mm wafer bonding system to China

EV GROUP (EVG), a supplier of wafer bonding and lithography equipment, has announced that it has installed a fully automated 300-mm system from EVG's Gemini product family of integrated wafer bonding clusters to a leading Chinese semiconductor foundry. This customer will use the system for 3D IC integration and advanced packaging-two highvolume applications.

"This order from one of the largest Chinese foundries further cements EV Group's position as the market and technology leader in wafer bonding for leading-edge applications," stated Hermann Waltl, executive sales and customer support director at EV Group.

"China is an important market for us, and this order is further testament to our continued success in penetrating leading high-volume microelectronics manufacturers in China-from advanced substrate suppliers to light emitting diode (LED) and semiconductor device makers."

EVG won this order following a competitive bid with other leading process equipment suppliers.

Reasons cited by the customer for choosing EVG included high alignment accuracy, comprehensive process development and support, successful demo results in EVG cleanrooms, unmatched expertise in wafer bonding and other high-volume process solutions, and a technology roadmap that is strongly aligned with that of the customer.

## Brewer Science upgrades production

LITHOGRAPHY INNOVATOR Brewer Science has installed a scale-up reactor to increase production of its CNTRENE C100 family of electronics-grade carbon nanotube (CNT) materials by tenfold. Such materials are used in chemical and biological sensors and nanotube-based non-volatile random access memory (RAM) device applications, which require extremely low levels of metal ion contaminants with concentration limits in parts per billion.

CNT technology is developing at a rapid rate and is quickly becoming a worthy rival to silicon in memory applications. "Small-scale reaction equipment can only take manufacturing so far with respect to quality and delivery time. This new scaleup reactor will provide the capability to complete weeks of reactions in three days while producing materials that meet stringent microelectronics specifications," says Stephen Gibbons, Director of Technology of Brewer Science's Carbon Electronics Centre. Jim Lamb, Director of Business Development for the Carbon Electronics Centre adds, "With increasing customer usage and the move toward commercial adoption in devices, we needed to implement our third round of scale-up to support market demand. Growth of our CNTRENE C100 family of products is driven by their use in nanotube-based non-volatile random access memory devices, a universal CNT memory structure developed by Nantero, Inc., sold under the name NRAM, which could replace embedded memory, DRAM, SRAM, and flash memory devices."

"This structure allows flexible placement of memory in the device stack and can be stacked for vertically placed memory cells. NRAM devices provide other key benefits including robustness, 3-nanosecond write speeds, low operating power, radiation-hardened memory cells, and the ability to perform at high operating temperatures," continues Lamb.

## imec announce launch of integrated silicon photonics platform

NANOELECTRONICS research centre imec has announced the launch of its fully integrated silicon photonics platform through a cost-sharing Multi-Project Wafer (MPW) service via ePIXfab. The platform enables costeffective R&D of silicon photonic ICs for high-performance optical transceivers (25Gb/s and beyond) and optical sensing and life science applications. The offered integrated components include low-loss waveguides, efficient grating couplers, high-speed silicon electro-optic modulators and highspeed germanium waveguide photodetectors.

Since 2007, imec and its associated laboratory at Ghent University have been offering a platform for passive silicon photonic components via ePIXfab, for R&D under shared cost conditions. Now, imec extends its silicon photonics offering, using a standard130nm CMOS toolset, with active components such as high-speed optical modulators and integrated germanium photodetectors.

"imec's Silicon Photonics platform provides robust performance and solutions to integrated photonics products in medical diagnostics, telecom and datacom industries. Companies can benefit from our silicon photonics capability through established standard cells, or explore the functionality of their own designs in MPW," stated Philippe Absil, program director at imec. "This Silicon Photonics MPW offer provides a costefficient solution, with state-of-the-art performance, design flexibility and superior CD and thickness control". The first run opens for registration with tape-in on 9th of Oct 2013 and first devices will be out in May 2014. Support, registration and design kit access will be organized by Europractice IC service, in collaboration with world-wide MPW partners.

## **NEWS** REVIEW

## AGC and nMode collaborate

TOKYO-BASED Asahi Glass Co., Ltd. (AGC) and nMode Solutions Inc. of Tucson, Arizona, have invested \$2.1 million to co found a subsidiary business, Triton Micro Technologies. The new company will develop innovative via-fill technology for interposers, enabling nextgeneration semiconductor packaging solutions using ultra-thin glass.

Headquartered in Tucson with a manufacturing facility planned in California, the subsidiary will combine nMode's interposer technology for electrically connecting semiconductor devices with AGC's materials technology and micro-hole drilling techniques to produce 2.5-dimensional (2.5D) and three-dimensional (3D) through-glass-via (TGV) interposers needed for advanced semiconductor devices. To achieve the next generation in high-density semiconductor packaging, interposer technologies are needed to form the high number of electrical connections between a silicon chip and a printed circuit board. Interposers allow high packaging integration in the smallest available form factors.

Triton will manufacture ultra-thin glass interposers using a high-efficiency continuous process that lowers costs and helps to commercialize the widespread use of interposers. The company will draw upon nMode's intellectual property and AGC's carrier-glass technology and via-hole drilling methodologies to fabricate its interposers. Triton will then apply its proprietary technology to fill the high-aspect-ratio via holes with a copper paste that has the same coefficient of thermal expansion as glass. This reduces the potentially damaging effects of thermal stress during manufacturing and long-term use. Triton's process

creates high-quality electrodes within the interposer to provide the electrical interface capable of accommodating advanced, high-density ICs. Triton's interposers are compatible with wafers having diameters from 100mm to 300mm and thicknesses of 0.7mm and below. The company can also design and manufacture customised solutions for unique applications.

"The global semiconductor industry recognises that silicon is approaching its performance limits as an interposer material, but the need remains to create smaller, more efficient packages for today's and tomorrow's highperformance ICs," comments Tim Mobley, CEO at Triton. "Our technology allows us to achieve known-good-die testing at the highest levels of packaging integration, faster cycle times and the lowest cost per unit in the market."

## Axcelis wins order from major memory & flash device maker

AXCELIS TECHNOLOGIES has announced that its Purion M medium current implanter has been selected by one of the world's leading chipmakers. The system will be used to develop and manufacture next generation memory and FLASH devices.

Bill Bintz, executive vice president of product development, engineering and marketing comments, "We're very excited about this, new win and the growth opportunities the system provides Axcelis." He continues, "The Purion M was selected after an extensive evaluation focused on implant accuracy, purity and repeatability; key requirements to achieve the customer's most challenging demands for emerging new device architectures. The system's innovative angle control system provides significant advantages over the competition in this critical area."

"In addition, the Purion M effectively demonstrated its ability to maintain the industry's highest levels of productivity,

beyond the traditional operating range for medium current implanters, resulting in unmatched levels of manufacturing flexibility and capital efficiency, significantly reducing their implant bay operating costs," Blintz adds.

# Infineon's 300mm CoolMOS silicon chips now shipping globally

INFINEON TECHNOLOGIES AG says it has achieved a major breakthrough in the manufacturing of power semiconductors on 300 millimetre thin wafers.

In February, the company received the first customer go-aheads for products of the CoolMOS family produced by the 300 millimetre (mm) line at the Villach (Austria) site. The production process based on the new technology has completed qualification from start to finish and customers have given the go-ahead.

Infineon believes its revolutionary silicon CoolMOS power family sets new standards in the field of energy efficiency. Using high voltage MOSFETs, CoolMOS offers a significant reduction of conduction and switching losses and enables high power density and efficiency for superior power conversion systems.

CoolMOS products are application specific and optimised for consumer products, renewable energy, telecom power supply, adapters and many others. "Infineon put its faith in this manufacturing technology very early on and continued to invest even in economically difficult times. We think and act with foresight and are now reaping the benefits: The qualification of our entire 300mm line represents a veritable leap ahead of the competition," says Reinhard Ploss, CEO of Infineon Technologies AG. "300mm thin-wafer manufacturing for power semiconductors will enable us, with the corresponding demand, to seize the opportunities that the market offers."

Infineon says it is the first and only company worldwide to produce power semiconductors on 300mm thin wafers. Thanks to their larger diameter compared to standard 200mm wafers, two-and-ahalf times as many chips can be made from each one.

The next step is for the present manufacturing concept for CoolMOS products, qualified from start to finish, with the front-end site Villach and assembly of the thin chips at the back-end site Malacca (Malaysia), to be expanded to the front-end site Dresden. Here the focus is on high-volume production in a fully automated 300mm line.

The basis for the processes required and the manufacturing technology is currently

being developed in research projects in Dresden. The technology transfer to Dresden is running on schedule and qualification of the first CoolMOS products will be completed in March.

Shortly, in Villach more power semiconductor technologies will be transferred to the 300mm line and produced. The development of the next power technology generation will focus on 300 instead of 200mm technology.

With these solutions customers can reduce development times and put new, more powerful products on the market more quickly. 300mm thinwafer technology guarantees that in the future Infineon will continue to be able to produce sufficient quantities at competitive costs.

## Martin L. Edelman jumps on board at AMD

AMD has appointed Martin Edelman to the company's board of directors as a representative of West Coast Hitech L.P., an affiliate of Mubadala Development Company and AMD's largest stockholder. Edelman's appointment follows the resignation of Waleed al Muhairi after four years of service on the AMD Board.

Edelman currently serves as Of Counsel, Real Estate Department for the law firm Paul, Hastings, Janofsky & Walker LLP, a New York City law firm where he is responsible for real estate transactions as well as corporate mergers and acquisitions. He serves as a member of the board of directors at several private and public companies, including Avis Budget Group, Ashford Hospitality Trust and Capital Trust.

Edelman is also a senior advisor to Mubadala Development Company, a strategic investment and development company headquartered in Abu Dhabi. He brings an extensive legal background to the board of directors, with more than 40 years of experience in the legal profession.

## **NEWS** REVIEW

## Oxford Instruments awarded patent for plasma film deposition

OXFORD INSTRUMENTS says plasma enhanced deposition processes typically decrease the deposition temperature, compared to chemical vapour deposition processes driven by heat alone. Using a high density plasma source offers a significant decrease in processing temperature for the same quality material, and can deposit silicon dioxide layers below 1000C. This development opens up this style of plasma processing to a new range of substrate materials including polymers.

The European patent EP1889946B1 cites Thomas, Griffiths and Cooke as inventors, and discloses a method of optimising uniformity over larger areas using a plasma transmission plate.

This technique has been used in more than 25 tools shipped by Oxford Instruments since the patent application was filed. Oxford Instruments Plasma Technology's CTO Mike Cooke says, "The grant of this patent covering high density plasma assisted thin film deposition is part of a broad platform of intellectual property rights which continue to be developed by our company. Oxford Instruments now has multiple patents, and we believe that this intellectual property reinforces our influential position in the plasma technology field."

Oxford Instruments Plasma Technology are leaders in the manufacture of flexible, configurable process tools and leading-edge processes for the precise, controllable and repeatable engineering of micro- and nano-structures.

The company's systems provide process solutions for the etching of nanometre sized features, nanolayer deposition and the controlled growth of nanostructures.

## Silicon threatens to muscle in on III-V devices

DEVICE REVENUES for gallium arsenide (GaAs), a compound semiconductor, grew slightly from 2011 to 2012. The primary drivers for the increase were in handset growth, particularly smartphones. Strategy Analytics maintains that although Skyworks and WIN Semiconductors remain at the top of this market, the silicon threat is looming.

According to the market research firm's "GaAs Device Industry Closes up in 2012" report, the silicon device market has seen recent developments which could compete with GaAs device revenues in the immediate future.

In the short-term, revenue in the GaAs device market is expected to exceed the historical average. But in the longer term, it is expected that recent developments in CMOS multi-mode, multi-band handset PAs from Qualcomm and others will pose a significant threat to the GaAs device market. "Smartphones continue to grow faster than the overall handset market. This growth, coupled with more bands and increased GaAs device content remains the single biggest driver for revenue growth in the GaAs device market," notes Eric Higham, Director of the Strategy Analytics GaAs and Compound Semiconductor Technologies Service (GaAs). "In the short-term, we anticipate this combination of factors will drive GaAs device revenue growth above historical averages."

Asif Anwar, Director, Strategy Analytics Strategic Technologies Practice, adds, "Strong growth in the last quarter of 2012 provides a good starting point for the GaAs industry in 2013.

However, recent announcements about CMOS multi-mode, multi-band PAs and envelope tracking will threaten the GaAs device market and these developments will be monitored closely."

## Watlow acquires Semiconductor Tooling Services

WATLOW, a designer and manufacturer of complete thermal systems, has acquired San Jose, California-based Semiconductor Tooling Services, Inc. (STS) as a wholly-owned subsidiary. The terms of the agreement will not be disclosed.

STS' primary offering is the development and application of precision bonds between critical components in a process tool assembly. These bonds are responsible for adhesion, as well as to provide specific heat conducting properties.

The acquisition will allow Watlow and STS to provide its shared customers a greater product offering. and increased capabilities.

"We are pleased that STS is now a part of Watlow because it helps us provide even more value to our semiconductor customers. One of Watlow's goals is to improve our domain knowledge and elevate our technical expertise in our strategic markets," says Tom LaMantia, Watlow's president.

"We fully support this acquisition," adds John Lilleland, owner of STS. "We have worked with Watlow for many years and have developed a mutual respect. Our complementary capabilities and mutual strengths will allow us to provide industryleading solutions for our customers." Watlow designs and man ufactures industrial heaters, temperature sensors, controllers and supporting software as well as assemblies - all of the components of a thermal system.

The company partners with its customers to optimize thermal performance, decrease design time and improve efficiency of their products and applications. Watlow brings its experience to numerous industries, including semiconductor processing, and environmental chambers.

## Instrumental in change

## Leading plasma process innovation

Oxford Instruments Plasma Technology is turning smart science into world class products with its flexible systems for precise and repeatable etching, deposition and growth of micro and nano structures

Plasma Etch & Deposition

Atomic Layer Deposition

Ion Beam Etch & Deposition

Deep Silicon Etch

-0

For more information, please contact Oxford Instruments Plasma Technology: **Tel:** +44 (0)1934 837 000 **Email:** plasma@oxinst.com

### www.oxford-instruments.com/plasma

The Business of Science

## **RESEARCH** NEWS

RESEARCHERS AT PURDUE UNIVERSITY have announced a new type of transistor shaped like a Christmas tree, where each transistor contains three tiny nanowires made of InGaAs.

So III-Vs replacing silicon seems to be a hot research topic, with InGaAs being one of the main contenders. Now scientists at MIT's Microsystems Technology Laboratories have also created a compound transistor, which performs well despite being just 22nm length. This also makes it a promising candidate to eventually replace silicon in computing devices, says codeveloper Jesús del Alamo, the Donner Professor of Science in MIT's Department of Electrical Engineering and Computer Science (EECS), who built the transistor with EECS graduate student Jiangian Lin and Dimitri Antoniadis, the Ray and Maria Stata Professor of Electrical Engineering.

To keep pace with our demand for ever-faster and smarter computing devices, the size of transistors is continually shrinking, allowing increasing numbers of them to be squeezed onto microchips. "The more transistors you can pack on a chip, the more powerful the chip is going to be, and the more

functions the chip is going to perform," del Alamo says.

But as silicon transistors are reduced to the nanometre scale. the amount of current that can be produced by the devices is also shrinking, limiting their speed of operation. This has led to fears that Moore's Law - the prediction by Intel founder Gordon Moore that the number of transistors on microchips will double every two years - could be about to come to an end, del Alamo savs.

To keep Moore's Law alive, researchers have for some time been investigating alternatives to silicon, which could potentially produce a larger current even when operating at these smaller scales. One such material is the compound InGaAs, which is already used in fibre-optic communication and radar technologies, and is known to have extremely good electrical properties, del Alamo says.

But despite recent advances in treating the material to allow it to be formed into a transistor in a similar way to silicon, nobody has yet been able to produce devices small enough to be

## The race is on to replace silicon with InGaAs

Silicon's crown is under threat. The semiconductor's days as the king of microchips for computers and smart devices could be numbered, thanks to the development of the smallest transistor ever to be built from III-V semiconductor indium gallium arsenide (InGaAs).

28<sup>29</sup> 30 1 26 25

25

20

19 18 17 16 15 14 <sup>13</sup>

24

23

22

21

20

2

34

5

6

7

8

9

10

net Iss

## **RESEARCH** NEWS

packed in ever-greater numbers into tomorrow's microchips. Now del Alamo, Antoniadis and Lin have shown it is possible to build a nanometre-sized metal-oxide semiconductor field-effect transistor (MOSFET) - the type most commonly used in logic applications such as microprocessors - using the material. "We have shown that you can make extremely small indium gallium arsenide MOSFETs with excellent logic characteristics, which promises to take Moore's Law beyond the reach of silicon," del Alamo says.

Transistors consist of three electrodes: the gate, the source and the drain, with the gate controlling the flow of electrons between the other two. Since space in these tiny transistors is so tight, the three electrodes must be placed in extremely close proximity to each other, a level of precision that would be impossible for even sophisticated tools to achieve. Instead, the team allows the gate to "self-align" itself between the other two electrodes.

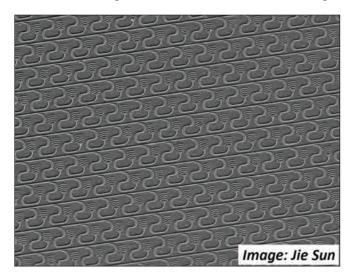

The researchers first grow a thin layer of the material using molecular beam epitaxy (MBE), a process widely used in the semiconductor industry in which evaporated atoms of indium, gallium and arsenic react with each other within a vacuum to form a single-crystal compound. The team then deposits a layer of molybdenum as the source and drain contact metal. They then "draw" an extremely fine pattern onto this substrate using a focused beam of electrons - another well-established fabrication technique known as electron beam lithography.

Unwanted areas of material are then etched away and the gate oxide is deposited onto the tiny gap. Finally, evaporated molybdenum is fired at the surface, where it forms the gate,

tightly squeezed between the two other electrodes, del Alamo says. "Through a combination of etching and deposition we can get the gate nestled [between the electrodes] with tiny gaps around it," he says.

The image above, courtesy of the researchers, shows a crosssection transmission electron micrograph of the fabricated transistor. The central inverted V is the gate. The two molybdenum contacts on either side are the source and drain of the transistor. The channel is the InGaAs light colour layer under the source, drain, and gate.

Although many of the techniques applied by the MIT teamare already used in silicon fabrication, they have only rarely been used

to make compound semiconductor transistors. This is partly because in applications such as fibre-optic communication, space is less of an issue.

" Although many of the techniques applied by the MIT team are already used in silicon fabrication, they have only rarely been used to make compound semiconductor transistors. This is partly because in applications such as fibre-optic communication, at small-device dimensions," space is less of an issue

transistors onto a chip, then we need to completely reformulate the fabrication technology of compound semiconductor transistors to look much more like that of silicon transistors," del Alamo says.

The team presented its work at the International Electron Devices Meeting in San Francisco. Their next step will be to work on further improving the electrical performance, and hence the speed of the transistor by eliminating unwanted resistance

within the device.

Once they have achieved this, they will attempt to further shrink the device, with the ultimate aim of reducing the size of their transistor to below 10 nm in gate length.

Matthias Passlack, of Taiwanese semiconductor manufacturer TSMC, says del Alamo's work has been a milestone in semiconductor research. "He and his team have experimentally proven that indium arsenide channels outperform silicon he says. "This pioneering

work has stimulated and

facilitated the development

of CMOS-compatible, III-V-

based-technology research and development worldwide.' The research was funded by DARPA and the Semiconductor Research Corporation.

"But when you are talking about integrating billions of tiny

© 2013 Angel Business Communications. Permission required

# Chips steer light in the right direction

"Record-setting" 'optical phased arrays' could lead to better laser rangefinders, smaller medical-imaging devices and even holographic TVs.

IF YOU WANT TO CREATE A MOVING LIGHT SOURCE, you have several possibilities. One is to mount a light emitter in some kind of mechanical housing - the approach used in, say, theatrical spotlights, which stagehands swivel and tilt to track performers. Another possibility is to create an array of light emitters and vary their "phase" - the alignment of the light waves they produce. The out-of-phase light waves interfere with one another, reinforcing each other in some directions but annihilating each other in others. The result is a light source that doesn't move, but can project a beam in any direction.

Such "phased arrays" have been around for more than a century, used most commonly in radar transmitters, which can be as much as 100 feet tall.

Now researchers from MIT's Research Laboratory of Electronics (RLE) have demonstrated a 4,096-emitter array that fits on a single silicon chip. Chips that can steer beams of light could enable a wide range of applications, including cheaper, more efficient, and smaller laser rangefinders; medical-imaging devices that can be threaded through tiny blood vessels; and even holographic televisions that emit different information when seen from different viewing angles. In a paper published this week in the journal Nature, the MIT team, led by Michael Watts, an associate professor of electrical engineering, report on two new chips. Both chips take in laser light and re-emit it via tiny antennas etched into the chip surface.

Issuel 201

SEARCH NEWS

## RESEARCH NEWS

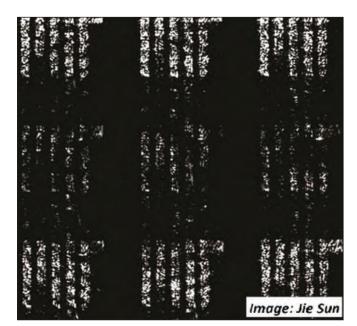

### Calculated incoherence

A wave of light can be thought of as a sequence of crests and troughs, just like those of an ocean wave. Laser light is coherent, meaning that the waves composing it are in phase. In other words, their troughs and crests are perfectly aligned. The antennas in the RLE researchers' chips knock that coherent light slightly out of phase, producing interference patterns. In the 4,096-antenna chip, a 64-by-64 grid of antennas, the phase shifts are pre-calculated to produce rows of images of the MIT logo, as shown in the figure at the top of this story.

The antennas are not simply turned off and on in a pattern that traces the logo, as the pixels in a black-and-white monitor would be. All of the antennas emit light, and if you were close enough to them (and had infrared vision), you would see a regular array of pinpricks of light. Seen from more than a few millimetres away, however, the interference of the antennas' phase-shifted beams produces a more intricate image.

In the other chip, which has an eight-by-eight grid of antennas, the phase shift produced by the antennas is tuneable, so the chip can steer light in arbitrary directions. In both chips, the design of the antenna is the same; in principle, the researchers could have built tuning elements into the antennas of the larger chip. But "there would be too many wires coming off the chip," Watts says. "Four thousand wires is more than Jie (the lead author of the paper), wanted to solder up."

Indeed, Watts explains, wiring limitations meant that even the smaller chip is tuneable only a row or column at a time. But that's enough to produce some interesting interference patterns that demonstrate that the tuning elements are working. The large chip, too, largely constitutes a proof of principle, Watts says. "It's kind of amazing that this actually worked," he says. "It's really nanometre precision of the phase, and you're talking about a fairly large chip."

#### **Precision engineering**

In both chips, laser light is conducted across the chip by silicon ridges known as "waveguides." Drawing light from the optical signal attenuates it, so antennas close to the laser have to draw less light than those farther away. If the calculation of either the attenuation of the signal or the variation in the antennas' design

Because of the interference of the phase-shifted light beams emitted by the antennas, images of the MIT logo appear to hover above the surface of the chip

is incorrect, the light emitted by the antennas could vary too much to be useful.

Both chips represent the state of the art in their respective classes. No two-dimensional tuneable phased array has previously been built on a chip, and the largest previous non-tuneable (or "passive") array had only 16 antennas. Nonetheless, "I think we can go to much, much larger arrays," Watts says. "It's now very believable that we could make a 3-D holographic display."

"I think it's one of the first clearly competitive applications where photonics wins," says Michal Lipson, an associate professor of electrical and computer engineering at Cornell University and head of the Cornell Nanophotonics Group.

"Within the photonics community, Lipson says, most work is geared toward "the promise that if photonics is embedded in electronic systems, it's going to really improve things. Here, (the MIT team) has developed a complete system. It's not a small component: This system is ready to go. So it's very convincing."

Lipson adds that the tuning limitation of the MIT researchers' prototype chips is no reason to doubt the practicality of the design. "It's just physically hard to come up with a very high number of contacts that are external," she says. "Now, if you were to integrate everything so that it's all on silicon, there shouldn't be any problem to integrate those contacts." More details of this work are published in the paper, "Large-scale nanophotonic phased array," by Jie Sun et al in Nature, 493, 195–199, (10 January 2013). DOI: 10.1038/ nature11727.

© 2013 Angel Business Communications. Permission required.

From the lab to the fab and to boardrooms all around the globe - one recruitment portal can fill your vacancy today

Reaches professionals from the silicon semiconductor, compound semiconductor and solar industries

Over 100,000 qualified professionals globally will see your vacancy

If you are recruiting and need a professional with the right experience to fit into your company, contact

## semisolarjobs.net

## **RESEARCH** NEWS

# Germanium p-type transistor boasts highest ever 'carrier mobility'

Almost all computer chips use two types of transistors: p-type (positive), and n-type (negative). Improving the performance of the chip as a whole requires parallel improvements in both types.

AT THE IEEE's International Electron Devices Meeting (IEDM) in December 2012, researchers from MIT's Microsystems Technology Laboratories (MTL) presented a p-type transistor which they claim has the highest "carrier mobility" yet measured. By that standard, the device is twice as fast as previous experimental p-type transistors and almost four times as fast as the best commercial p-type transistors. Like other experimental high-performance transistors, the new device derives its speed from its use of a material other than silicon.

The researchers in this case, used germanium. Alloys of germanium are already found in commercial chips, so germanium transistors could be easier to integrate into existing chip-manufacturing processes than transistors made from more exotic materials. The new transistor also features what's called a trigate design, which could solve some of the problems that plague computer circuits at extremely small sizes (and which Intel has already introduced in its most advanced chip lines). For all these reasons, the new device offers a tantalising path forward for the microchip industry - one that could help sustain the rapid increases in computing power, known as Moore's Law, that consumers have come to expect.

#### **Pluses and minuses**

A transistor is a switch that in one position allows charged particles to flow through it ; in the other position, it doesn't. In an n-type transistor, the electrons, which are the charge carriers, produce an ordinary electrical current. In a p-type transistor, the charge carriers are positively charged "holes." A p-type semiconductor doesn't have enough electrons to balance out the positive charges of its atoms; as electrons hop back and forth between atoms, trying futilely to keep them electrically balanced, holes flow through the semiconductor, in much the way waves propagate across water molecules that locally move back and forth by very small distances.

"Carrier mobility" measures how quickly charge carriers whether positive or negative - move in the presence of an electric field. Increased mobility can translate into either faster transistor switching speeds, at a fixed voltage, or lower voltage for the same switching speed.

For decades, each logic element in a computer chip has consisted of complementary n-type and p-type transistors whose clever arrangement drastically reduces the chip's power consumption. According to the MIT scientists, in general, it's easier to improve carrier mobility in n-type transistors; the MTL researchers' new device demonstrates that p-type transistors should be able to keep up.

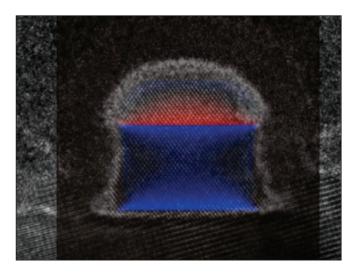

#### Handling the strain

The researchers from MIT and the University of British Columbia achieved their "record-setting" hole mobility by "straining" the germanium in their transistor. This forced its atoms closer together than they'd ordinarily find comfortable. To do that, they grew the germanium on top of several different layers of silicon and a silicon-germanium composite. The germanium atoms naturally try to line up with the atoms of the layers beneath them, which compresses them together. The micrograph at the top of this story, shows an experimental transistor. Blue highlighting indicates areas of "strain," where germanium atoms have been forced closer together than they find comfortable. One of the reasons for the transistor's record-setting performance is that the strain has been relaxed in the lateral direction.

"It's kind of a unique set of material structures that we had to do, and that was actually fabricated here, in the MTL," professor of electrical engineering and computer science at MIT, Hoyt says. "That's what enables us to explore these materials at the limits. You can't buy them at this point."

"These high-strain layers want to break," Teherani, lead author of a paper describing the work, adds. "We're particularly successful at growing these high-strain layers and keeping them strained without defects."

Indeed, Hoyt is one of the pioneers of strained-silicon transistors, a technology found today in almost all commercial computer chips. At last year's IEDM, she and Eugene Fitzgerald, the Flemings-SMA Professor of Materials Science and Engineering at MIT, received the IEEE's Andrew S. Grove

## **RESEARCH** NEWS

As transistors have grown smaller, their gates have shrunk, too. But at smaller sizes, that type of lockstep miniaturisation won't work: Gates will become too small to reliably switch transistors off

Award for outstanding contributions to solid-state devices and technology. The award announcement cited Hoyt's "groundbreaking contributions involving strained-silicon semiconductor materials."

#### Gatekeeping

Another crucial aspect of the new transistor is its trigate design. If a transistor is a switch, throwing the switch means applying a charge to the transistor's "gate." In a conventional transistor, the gate sits on top of the "channel," through which the charge carriers flow. As transistors have grown smaller, their gates have shrunk, too. But at smaller sizes, that type of lockstep miniaturisation won't work: Gates will become too small to reliably switch transistors off. In the trigate design, the channels rise above the surface of the chip, like boxcars sitting in a train yard. To increase its surface area, the gate is wrapped around the channel's three exposed sides - hence the term "trigate."

By demonstrating that they can achieve high hole mobility in trigate transistors, Hoyt and her team have also shown that

their approach will remain useful in the chips of the future."The germanium part helps in increasing the drive current, and the trigate part helps in reducing the leakage in the off state," says Krishna Saraswat, the Rickey/Nielsen Professor in Engineering at Stanford University, who was not involved in this research. "So a combination of those two just gives you an ideal transistor for the next generation."

Saraswat believes that the semiconductor industry is already planning a move toward germanium circuits. "The choice is to scale the silicon transistor without any performance gains - just get to higher packing density - or get higher packing density as well as better performance," he says. "And it's fairly clear that the industry will go for high-strain germanium." The MIT researchers' work was supported by the U.S. Defence Advanced Research Projects Agency and the Semiconductor Research Corporation.

> © 2013 Angel Business Communications. Permission required

RESEARCHERS FROM THE UNIVERSITY OF WÜRZBURG have modified SiC crystals to exhibit new and surprising properties. This makes them interesting with regard to the design of highperformance computers or data transmission. SiC crystals consist of a regular lattice formed by silicon and carbon atoms. At present, these semiconductors are extensively used in micro and optoelectronics. They are particularly suited for use in high temperature applications in power semiconductors. Now physicists from Saint Petersburg and the University of Würzburg have succeeded in manipulating SiC in a way so it can be used in novel, super-fast quantum computers. would have to consist of one individual atom in ten years' time. At this scale, however, special physical laws apply, namely the laws of quantum mechanics. The computers of today process information with the binary system (0/1): Electricity flows or it does not. A quantum computer processes information in the form of so-called qubits.

These can be based on the spin of electrons. In simplified terms, the spin represents their angular momentum. It can point in several directions, for which reason it can represent much more information than a classical bit.

## Improving on diamond in supercomputers

By creating a silicon vacancy defect in silicon carbide, scientists have generated additional energy levels in the so band gap for use in supercomputers.

### A defect in the crystal

"We have removed a silicon atom from the crystal lattice, thus creating a silicon vacancy defect," Georgy Astakhov says, explaining the method applied by the physicists. Astakhov is a research fellow at the Department for Experimental Physics VI of the University of Würzburg.

To the researchers' surprise, this crystallographic defect gives the material interesting new properties. In order for the semiconductor to emit light, its electrons must be raised to a higher energy level by means of energy-rich light, for instance. The silicon vacancy defect leads to the generation of additional energy levels in the so-called band gap.

#### Stepladder for electrons

Vladimir Dyakonov, chair of the Department for Experimental Physics VI, explains the process with a simple analogy; "In a regular, perfectly structured silicon carbide crystal, the electron must overcome a big hurdle with only one step. This requires a lot of energy. Due to the defect, the electron is provided with a ladder. It can clear the hurdle with two steps, requiring less energy."

When the electrons "fall back" from the higher energy level to the lower one, this type of silicon carbide emits infrared rather than ultraviolet light. According to Astakhov, such light is better suited to transfer information in an optical fibre. "This requires wavelengths in the infrared range," the physicist says.

### Application in a quantum computer

The modified SiC is particularly promising for another application – as a semiconductor and storage medium in novel quantum computers. "Since their invention, transistors have shrunk from several tens of micrometers to approximately 10nm, i.e. about one thousandth of their original size," Astakhov notes. If the miniaturisation continues at this speed, transistors

#### The information lies in the defect

"In this field of research, a lot of attention has been paid to the colour centres in diamond, which exhibit defects that are similar to those of our silicon carbide," says Astakhov.

Their qubits can be easily addressed, changed or read even at room temperature. However, the diamond production technology is not nearly as advanced as that of silicon semiconductors. "For this reason, there is a worldwide hunt for quantum systems that combine the advantages of diamond and silicon within one material," Astakhov explains.

## **RESEARCH** NEWS

The Würzburg physicists believe SiC with a vacancy defect to be a suitable candidate for this purpose. "The missing atom also has as a consequence that the crystal lattice lacks an electron, which in turn is equivalent to the spin that can be used as information carrier in a quantum computer," Dyakonov explains. What's more, the SiC technology is fairly well developed. LEDs, transistors, micro-electro-mechanical components or sensors made from this material are already on the market.

## Exposing the material to light and radio waves

The Würzburg physicists conducted their experiments in collaboration with researchers from Saint Petersburg. By "hitting" the silicon crystals simultaneously with light and radio waves, they were able to manipulate the spins in a targeted way, enabling them to store and retrieve information at will.

What the physicists are particularly enthusiastic about is the fact that the silicon vacancy qubits in a densely packed crystal behave almost like atoms with well-defined, very sharp optical resonances. "This is very unusual," Astakhov adds.

"This is a new research field where experimental data of other study groups are still scarce at the moment. However, the reviewers looked favourably on our experiments and immediately recommended our manuscript for publication. We are very curious to know how the scientific community will react to our study," Astakhov reveals. The first reaction has already materialised; Astakhov has been invited to present his results at the Quantum Science Symposium in Cambridge.

Spin quantum computers not only require the ability to process information, but also to store the information for as long as possible. This is still a problem at this point, since the stray field of adjacent nuclei can gradually erase the information stored in the defects.

Therefore, the researchers from Würzburg and Saint Petersburg plan as a next step to produce SiC crystals that are formed from a silicon isotope without a magnetic moment. "We know that spin-free isotopes of silicon and carbon atoms exist," concludes Astakhov. A SiC crystal exclusively consisting of such isotopes should therefore be capable of storing the information over a long period of time.

Further details of this work have been published in the paper, "Resonant addressing and manipulation of silicon vacancy qubits in silicon carbide", by D. Riedel, et al in Physical Review Letters, 109, 226402 (2012). DOI:10.1103/ PhysRevLett.109.226402

> © 2013 Angel Business Communications. Permission required

## Submit your Lab & Fab article

Research is the foundation for the growth of the Silicon Semiconductor industry.

If you want to highlight the important breakthroughs that you make, submit your latest research stories to: jackie.cannon@angelbc.com

It is imperative that Silicon Semiconductor remains a timely resource for this industry, so we are only interested in highlighting very recent work reported in academic papers.

Therefore, please only consider writing a short piece highlighting your work if you have a journal paper that has been accepted and about to appear in press, or a paper that has been published within the last month.

## RESEARCH NEWS

# Si-InP sandwich chips combine the best of both worlds

The integration of a silicon chip with an indium phosphide chip could hold the key to faster and more powerful terahertz chips for high resolution and mobile applications.

TWO LEIBNIZ INSTITUTES have broken new technological ground; they have successfully combined their - up to now separate technologies. Due to their high performance, the novel chips developed within the HiTeK project promise to open the door to new applications.

Wolfgang Heinrich and Bernd Tillack are convinced of holding the key to faster and more powerful terahertz chips. The two scientists and their teams come from the Berlin-based Ferdinand-Braun-Institut (FBH) and from the IHP-Leibniz-Institut für innovative Mikroelektronik in Frankfurt/Oder. FBH is one of the leading institutes in developing III-V semiconductors, while IHP is specialised in silicon-based systems and circuits. Both Leibniz institutes joined forces within the HiTeK project to combine the advantages of silicon-based CMOS (Complementary Metal Oxide Semiconductor) circuits from the IHP with those of indium phosphide (InP) circuits from the FBH.

The partners have taken an important step within the project by successfully integrating both circuits onto a semiconductor wafer, with experimental results demonstrating their high performance. With the integration on one chip, new ambitious applications in the THz range are within reach. These include high-resolution imaging systems for medical and security technology as well as ultra-broadband mobile communication applications.

For such applications, high output powers along with faster computer processors are needed, offering enhanced computer operation per second. In order to achieve this, circuits on the chips need to become smaller - the key reason which boosts miniaturisation in the semiconductor industry. If the frequency range around 100 gigahertz (GHz) and beyond is to be covered, however, the breakdown voltage in the CMOS switching circuits decreases significantly. As a consequence, the available output power of the chips declines. This implies that the capability of generating sufficiently strong signals to establish a radio link and to detect material defects becomes insufficient. To find a solution to this problem, IHP conducted research on bipolar CMOS based on SiGe, enhancing the breakdown voltages at high speed compared to pure CMOS. By combining a standard CMOS circuit with a second InP circuit promised further improvement.

Both circuits are realised in a "sandwich-like" structure and lie one on top of another. Where the traditional silicon-based CMOS technology reaches its limits, this novel material

combination delivers the desired properties; high output powers at high frequencies. The sandwich chips enable a high level of production and integration of CMOS circuits - particularly regarding the fact that 95 percent of all digital and analoguedigital circuits are based on this technology.

"It was particularly challenging to make both technologies compatible at the interfaces", underlines Wolfgang Heinrich from the FBH. To achieve this, the whole development environment of both processes as, for example, the software for the circuit layout had to be merged in a first step. Subsequently, both layers had to be dimensioned so that they reach the essential good transmission properties for frequencies around 200 GHz. Precision work was also highly demanded to adjust the circuits precisely to each other with an accuracy of less than 10µm.

Heinrich is especially proud of the friction-less cooperation, "We managed to align both technology worlds so smoothly that the circuits deliver fully the specified high-frequency performance. This also demonstrates what added value can be created by bundling the competencies of two institutes like IHP and FBH". The next steps are to further stabilise the process and to optimise the circuits. A follow-up project has already been granted. In this way, the potential of the hybrid chips will be exploited fully to reach the borders of what is feasible . This will set the stage for the novel sandwich circuits to be integrated in sophisticated applications in the near future.

© 2013 Angel Business Communications. Permission required.

## The Power of [2

# SEMICON® Europa2013

## Connect to the trends, technologies and people driving the European Semiconductor Industry forward.

SEMICON Europa is the place to see the leading companies, technologies, and people driving the future of micro- and nanoelectronics design and manufacturing.

SEMICON Europa exhibitors are the suppliers to and partners of Europe's leading microelectronics companies. From silicon to system – and everything in between and beyond - SEMICON Europa showcases the biggest and brightest names in microelectronics manufacturing.

## Plan now to be part of **SEMICON Europa 2013**

PE 2013 EXHIBITION & CONFERENCE

Co-located with:

### **SEMICON Europa** Programs:

- 15<sup>th</sup> European Manufacturing Test Conference (EMTC)

- Advanced Packaging Conference

- 17<sup>th</sup> Fab Managers Forum

- International MEMS / MST Industry Forum

- 7<sup>th</sup> Executive Summit

- SEMI Market Briefing

- Metrology, Process Control, Automation and Software Session

- 3D IC Session

- Power Electronics Session

- Secondary Equipment and Technology Session

- LED / SSL Session

- Workshop on Equipment Assessment & Performance Improvements

- Standards Meetings

### www.semiconeuropa.org

www.plastic-electronics.org

## **INDUSTRY** ANALYSIS

# SEMI: Flat Fab equipment in 2013 to rocket 24% in 2014

Fab equipment spending for Front End facilities is expected to hover around flat in 2013 and with an increase of 24 percent in 2014 as shown in Table 1 below. The SEMI World Fab Forecast, published at the end of February, reveals little has changed from the projections published at the end of November when the report was last issued. The report tracks equipment spending at over 180 facilities in 2013.

At the time of the November 2012 publication, semiconductor companies had not announced their capex plans for 2013, so fab spending predictions were based on extensive modelling. More than 262 updates have been made since the last publication and are based on announced spending plans, including major changes for TSMC, Samsung, Intel, SK Hynix, Globalfoundries, UMC, and for some Japanese facilities and LED facilities.

Despite these adjustments, the overall forecast for equipment spending for 2013 has remained about the same. Depending on macro-economic risk factors, possible scenarios project a range of -3 percent to +3 percent change rate for fab equipment spending in 2013; in other words, hovering around flat. Global chip sales have started on a bright note in 2013, as the SIA reports that three-month average for global chip sales for January increased 3.8 percent above January 2012. It also appears that the average sentiment for revenue growth is in the upper single digits in 2013, about 7 percent Y-o-Y, compared to about -3 percent in 2012.

Though the overall outlook has improved some, fewer players in the market can afford the rising costs for R&D and upgrading facilities as the amount of

money needed to upgrade facilities at the leading edge technologies is immense.

The World Fab Forecast report shows increases for fab equipment spending, varying by technology node. Fab equipment spending for 17nm and below is expected to kick off in 2013 and increase by a factor of 2.4 to about \$25 billion from 2013 to 2014. Fab construction spending is now expected to increase more than previously predicted.

Back in November 2012, a change of 3.7 percent Y-o-Y was forecasted; now, 6.7 percent growth is forecasted with construction spending to reach almost US\$6 billion. In 2014, however, construction project spending is expected to contract by about 18 percent. Construction spending is led, far and away, by TSMC, with seven different projects for the year; followed by Intel with projects including D1X module 2, Fab 42 and some other sites. Fab construction spending in China will increase by a factor of four because of Samsung's Mega fab in Xian. Since the 2008/2009 economic downturn, the industry has been adding capacity more slowly than ever, as reflected in SEMI's World Fab Forecast data. Capacity is now forecasted to expand by just 2.8 percent for this year, and to improve to 5.4 percent growth in 2014.

Excluding 2009, the years 2012 and 2013 show the lowest growth rate for new capacity over that past ten years. The World Fab Forecast gives detailed capacity information by industry segment and by individual company and fab. Dedicated foundries are expected to add 10 to 11 percent more capacity in 2013 and 2014. Flash will add 4 percent new capacity in 2013 and about 10 percent in 2014. New capacity expansions for the System LSI segment should drop from the double digits of previous years to single digits in 2013 and 2014.

SEMI believes that there will be a pent-up demand for some product types because capacity additions have been cut to a minimum level while chip demand keeps increasing. Capacity additions and equipment spending are expected to pick up in the second half of 2013. In 2014, at least 5 percent in new capacity will be added and fab equipment spending will increase by 24 percent.

© 2013 Angel Business Communications. Permission required.

| Fab Equipment Spending: Front End |        |        |         |        |          |  |

|-----------------------------------|--------|--------|---------|--------|----------|--|

|                                   | 2010   | 2011   | 2012    | 2013   | 2014     |  |

| Equipment spending                |        |        |         |        |          |  |

| in US\$ Million                   | 33,530 | 38,710 | 31,802  | 31,668 | 39,266   |  |

| Change %                          | -      | 15.4%  | -17.18% | -0.4%  | 24%      |  |

| including used and in-house       |        |        |         | •      | <u> </u> |  |

Source: SEMI World Fab Forcast reports (February 2013)

## **INDUSTRY** ANALYSIS

Intel, is focused on MPUs. Samsung is expected to maintain its lead in installed capacity through 2017, with aggressive capital spending plans seen over the past few years continuing over the next five years.

However, in terms of growth rate, IC Insights expects the largest increase in 300mm capacity to come from the pureplay foundries - TSMC, GlobalFoundries, UMC, and SMIC. In total, IC Insights expects these four companies to more than double their collective 300mm wafer starts per month by 2017.

IC Insights believes that the companies listed in the table above will represent essentially all the advanced 300mm

# IC suppliers to monopolise 300mm wafer space

SEMICONDUCTOR INDUSTRY capital spending is becoming more concentrated with a greater percentage of spending coming from a shrinking number of companies. As a result, IC industry capacity is also becoming more concentrated and this trend is especially prevalent in 300mm wafer technology. The table lists the 300mm installed capacity leaders for 2012 and IC Insights' forecast for 2013.

The list was compiled and included in IC Insights' updated report titled, "Global Wafer Capacity 2013 - Detailed Analysis and Forecast of the IC Industry's Wafer Fab Capacity".

Samsung was by far the leader in 2012 having about 61 percent more 300mm capacity than second-place SK Hynix. Intel was the only other company that held a double-digit share of 300mm capacity at the end of 2012.

Assuming Micron is successful in acquiring Elpida in the first half of 2013, the combined 300mm wafer capacity of the two companies will make the merged company the second-largest holder of 300mm capacity in the world behind Samsung.

Of the top 10 companies on the list, half are primarily memory suppliers, two are pure-play foundries, and one company, IC production and capacity in the future. The market research firm also anticipates that the top seven or eight companies -Samsung, "Micron-Elpida," TSMC, SK Hynix, Intel, Toshiba/SanDisk, and GlobalFoundries - can be considered an "elite" group that is just about guaranteed to be a driving force in 300mm capacity additions.

The remaining companies are likely to participate in future 300mm capacity expansion, but all have varying degrees of risk associated with fully realising their long-term 300mm IC production capacity goals.

Meanwhile, there is still much uncertainty as to when the industry will make the next wafer-size transition - from 300mm to 450mm - and how much it will cost to do so, but momentum continues to build and the transition can now be considered certain to happen.

IC manufacturers have yet to fully optimise the high-volume manufacturing cost structure for the 300mm wafer size. However, the potential per-die cost savings that the larger wafer can provide is enough of a motivating factor to make the transition happen.

© 2013 Angel Business Communications. Permission required.

| 300mm Wafer Capacity Leaders Forecast<br>(Installed Monthly Capacity in 300 mm Wafers x 1000) |                  |                                          |                       |                                           |                           |  |

|-----------------------------------------------------------------------------------------------|------------------|------------------------------------------|-----------------------|-------------------------------------------|---------------------------|--|

| 2013F<br>Rank                                                                                 | Company          | 2012<br>Installed<br>Capacity<br>(K w/m) | 2012 % of<br>WW Total | 2013F<br>installed<br>Capacity<br>(K w/m) | 2013 F%<br>of WW<br>Total |  |

| 1                                                                                             | Samsung          | 675                                      | 18.8%                 | 717                                       | 18.4%                     |  |

| 2                                                                                             | Micron-Elpida*   | 512                                      | 14.4%                 | 536                                       | 13.8%                     |  |

| 3                                                                                             | SK Hynix         | 420                                      | 11.7%                 | 450                                       | 11.6%                     |  |

| 4                                                                                             | Intel            | 388                                      | 10.8%                 | 441                                       | 11.3%                     |  |

| 5                                                                                             | TSMC             | 356                                      | 9.9%                  | 414                                       | 10.7%                     |  |

| 6                                                                                             | Toshiba/SanDisk  | 320                                      | 8.9%                  | 320                                       | 8.2%                      |  |

| 7                                                                                             | Global Foundries | 125                                      | 3.5%                  | 150                                       | 3.9%                      |  |

| 8                                                                                             | Nanya            | 125                                      | 3.5                   | 127                                       | 3.3%                      |  |

| 9                                                                                             | UMC              | 97                                       | 2.7%                  | 115                                       | 3.0%                      |  |

| 10                                                                                            | Powerchip**      | 125                                      | 3.5%                  | 90                                        | 2.3%                      |  |

| 11                                                                                            | TI               | 51                                       | 1.4%                  | 57                                        | 1.5%                      |  |

| 12                                                                                            | SMIC             | 51                                       | 1.4%                  | 57                                        | 1.5%                      |  |

| -                                                                                             | Top 12           | 3245                                     | 90.4%                 | 3477                                      | 89.5%                     |  |

| -                                                                                             | Others           | 346                                      | 9.6%                  | 410                                       | 10.5%                     |  |

| -                                                                                             | Total            | 3591                                     | 100%                  | 3887                                      | 100%                      |  |

Assumes Micron completes acquisition of Elpida in 1H13

\*\* Assumes Powerchip either sells or tears down B3 Fab as it plans to do Source: Companies, IC Insights

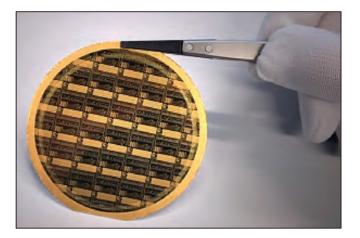

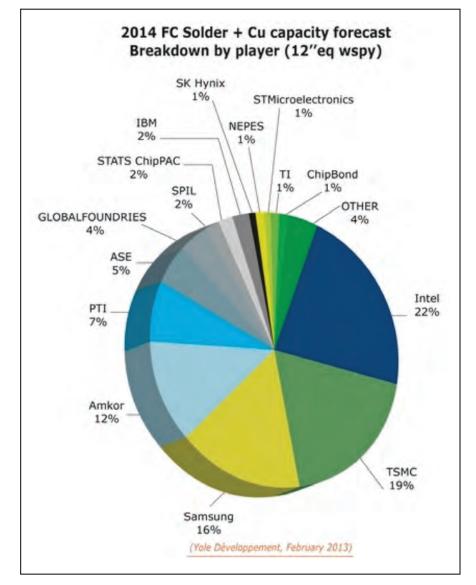

# Cu pillar and micro-bumping flip-chip platforms invigorates the market

OVER THE NEXT FIVE YEARS, wafer growth is expected to triple for the Flip-Chip platform, which will reach over 40 million of 12"eq wspy by 2018.

This is according to Yole Développement's "Flip Chip Market and Technology Trends" report, which updates the business status of the Flip-Chip market including data for TIM, underfills, substrates and Flip-Chip bonders.

Despite its high 19 percent CAGR, Flip-chip is not new - in fact, it was first introduced by IBM over 30 years ago. As such, it would be easy to consider it an old, uninteresting, mature technology but this is far from true. Instead, Flip-Chip is keeping up with the times and developing new bumping solutions to serve the most advanced technologies, like 3DIC and 2.5D.

Indeed, no matter what packaging technology you're using, a bumping step is always required at the end. In 2012, bumping technologies accounted for a massive 81 percent of the total installed capacity in the middle end area. This represents over 14 million 12''eq wafers. What's more, fab loading rates are high, especially for the Cu pillar platform (88 percent).