Volume 35 Issue 4 2013

🔁 @siliconsemi

www.siliconsemiconductor.net

### Material advancements

New acoustic tools for wafers

# Europe's new global force

Revolutionising electronics

Nanoscale lithography

Cost-effective surface mounting of complex stacked die

NOVA

Die and flip-chip bonding strive for ultra high precision

AMICRA

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

Features, News Review, Industry Analysis, Research News and much more. Free Weekly E News round up , go to www.siliconsemiconductor.net

# Optimize the Thermal Performance of your Process Equipment.

Extensive computational tools enable product designs to be highly refined for ultimate performance.

Multi-zone circuit layouts in a polyimide construction are highly customized to deliver exacting performance up to 250°C.

EZ-ZONE<sup>®</sup> RM Multiloop controllers are fully scalable with up to 152 PID Loops and 256 monitor points per system. Washing at low provides innovative solutions to help process tool manufacturers meet the needs of the semiconductor technology roadmap. Our approach is to work collaboratively to help solve complex thermal challenges associated with state-of-theart manufacturing processes; helping to improve yield, throughput and cost of ownership. This includes innovative heaters, controllers and sensors for use in front-end and back-end applications such as CVD, PECVD, Etch, Diffusion, Bonding, IC test and more.

WATLO

ASSURANT<sup>™</sup> gas and pump line heaters feature high temperature capabilities with low outgassing.

# Contact Watlow<sup>®</sup> today for the latest thermal solutions for semiconductor applications.

| Europear | Technical Sales Offices               | Italy |

|----------|---------------------------------------|-------|

| Germany  | +49 (0) 7253-9400-0<br>info@watlow.de | Spain |

| France   | +33 1 41 32 79 70<br>info@watlow.fr   | UK    |

+39 02 4588841 italyinfo@watlow.com +34 91 675 1292 info@watlow.es

+44 (0) 115-964-0777 info@watlow.co.uk

# executiveview

by Robert Cappel, Senior Director of Corporate Marketing, KLA-Tencor

# Optical & E-Beam inspection address smaller designs

SEMICONDUCTOR MANUFACTURERS are implementing new patterning techniques and structures to produce smaller, faster devices for consumer electronics. At sub-20nm design nodes, innovative process control is required to optimize fab processes and ensure optimal yields.

Metrology and inspection tools serve as the key "check and balances" branch of IC manufacturing, enabling faster learning cycles and improved ramp-to-revenue schedules. By finding design, patterning or process issues early, fabs can maximize yield and device performance, while reducing costs and risks.

The real industry work horse for defect inspection has always been optical inspectors. As design nodes shrink and critical defects become smaller, it's worth exploring whether e-Beam inspection should move to a more prominent role in a fab's inspection strategy.

Let's consider today's manufacturers who must find small defects very quickly over large areas. Suppose we scale a 10nm defect to the size of a coin and disperse hundreds of coins across an area the size of California-representative of a 300mm wafer. Currently, broadband plasma optical inspection is the only technology capable of finding all the coins across a range of surfaces over this entire area in an hour. It would take the e-Beam tool over a year to inspect the entire area; or, it could inspect a very small area in an hour, missing critical

information such as the overall distribution of coins or critical areas where they are located. Lacking this information, a fab could miss a major yield excursion, resulting in hundreds of millions of dollars in lost profit.

Innovations in optical technologies such as a laser-pumped broadband light source, optics as complex as those used in steppers, selectable apertures and high-speed sensors produce the sensitivity required to find small defects on advanced devices. The combination of these technologies provide inspection flexibility and capability that cannot be found in other optical or e-Beam inspectors, enabling critical defect detection on the widest range of process layers.

Additional innovations have made optical inspection smarter: NanoPoint provides ultra-focused inspection of critical patterns that serve as early indicators of design or process issues.

Since optical inspection couples critical defect sensitivity with the speed required for monitoring wafer and lot variations, it will continue as the dominant defect inspection approach. E-Beam will continue to play a complementary role, supporting optical inspection set up and detecting defect issues related to electrical problems, such as opens, shorts and reliability issues. With this strategy, IC manufacturers can quickly identify yield and reliability issues, ensuring successful and fast product ramp.

| News Editor Dr. Su Westwater                                                                                                          | suwestwater@angelbc.com    | Circulation & Subscriptions Assistant Annette Weatherilt                               | annette.weatherilt@angelbc.com |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------|--------------------------------|

| Director of SEMI Publishing Jackie Cannon                                                                                             | jackie.cannon@angelbc.com  |                                                                                        | +44 (0)1923 690220             |

|                                                                                                                                       | +44 (0)1923 690205         | Chief Operating Officer Stephen Whitehurst                                             | stephen.whitehurst@angelbc.com |

| Senior Sales Executive Robin Halder                                                                                                   | robin.halder@angelbc.com   |                                                                                        | +44 (0)2476 718970             |

|                                                                                                                                       | +44 (0)2476 718109         | Directors Bill Dunlop Uprichard - CEO, Stephen Whitehurst - CO                         | DO, Jan Smoothy – CFO,         |

| Sales Manager Shehzad Munshi                                                                                                          | shehzad.munshi@angelbc.com | Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal                                |                                |

|                                                                                                                                       | +44 (0)1923 690215         |                                                                                        |                                |

| USA Representatives Tom Brun Brun Media                                                                                               | E: tbrun@brunmedia.com     | Published by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road,       |                                |

|                                                                                                                                       | Tel: 724 539-2404          | Watford, Herts WD17 1JA, UK.                                                           |                                |

| Janice Jenkins                                                                                                                        | E: jjenkins@brunmedia.com  | T: +44 (0)1923 690200 F: +44 (0)1923 690201 E: ask@angelbc                             | c.com                          |

|                                                                                                                                       | Tel: 724-929-3550          |                                                                                        |                                |

| Director of Logistics Sharon Cowley                                                                                                   | sharon.cowley@angelbc.com  | Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, |                                |

|                                                                                                                                       | +44 (0)1923 690200         | Coventry CV5 6SP, UK.                                                                  |                                |

| esign & Production Manager Mitchell Gaynor mitch.gaynor@angelbc.com T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com |                            | oc.com                                                                                 |                                |

|                                                                                                                                       | +44 (0)1923 690214         |                                                                                        |                                |

| Circulation Director Jan Smoothy                                                                                                      | jan.smoothy@angelbc.com    | Angel 🔗 🛛 🔂 🔶 Tecyc                                                                    | le                             |

|                                                                                                                                       | +44 (0)1923 690200         | RUSINESS COMMUNICATIONS When you have                                                  | e finished with                |

Silicon Semiconductor is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright orensights in a subsequent issue of the publication. Angel Business Communications Ltd will be happy to acknowledge any copyright consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor (ISSN 1096-598X) is published four times a year for a subscription of \$198 by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Hers WD17 1JA, UK. Periodicals postage paid at Rahway, NJ. POSTMASTER: send address changes to: Silicon Semiconductor, c/o Mercury International Ltd, 365 Blair Road, Avenel, NJ 07001. Printed by: Pensord Press. @ Copyright 2013. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online).

# **Stepper redefined**

### MEETING LITHOGRAPHY CHALLENGES HEAD-ON

Large field of view (52mm x 66mm) 30 reticle library with four-reticle wheel On-the-fly auto focus for each exposure Warped wafer handling Superior depth of focus for thick resists Substrate and size flexibility

(450mm, reconstituted wafers, square interposers, etc.)

### Advancing Tomorrow's Technology

TECHNOLOGIES

RUDO

-JetStep≞ Advanced Packaging-Lithography System

www.rudolphtech.com

# features

### COVER STORY

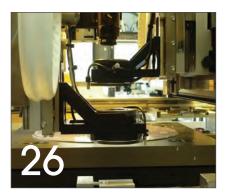

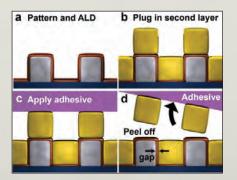

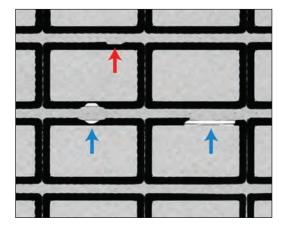

### 26 Die and flip-chip bonding striving for ultra high precision

Cost-effective surface mounting of complex stacked die using TSV interconnect calls for ultra-high-precision die and flip-chip bonders. Consequently, back-end equipment vendors and process designers must come up with modular concepts to accommodate a broad scope of micro-assembly tasks.

# 30 Meeting advanced packaging geometries through material advancements

The boom in the mobile market with increasing demands for smaller geometries has created the need for novel and innovative chemistries to overcome the limitations of existing materials.

# 34 Europe's semiconductor industry can become a global force again

The European Commission's decision to spend up to 10 billion euros for R&D activities will create new opportunity for Europe globally.

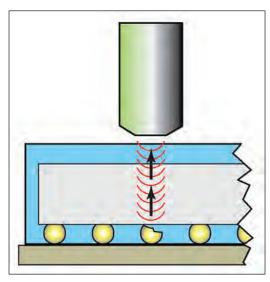

# 36 MUF and wafers get new acoustic tools

Modifications of production processes and changes in device dimensions require new non-destructive techniques to inspect for reliability.

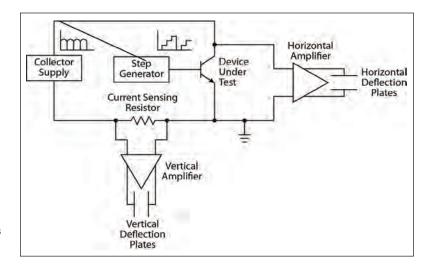

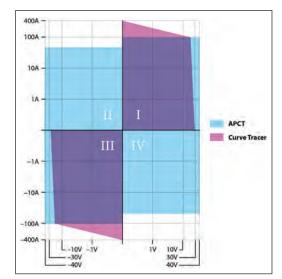

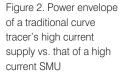

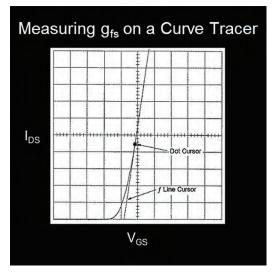

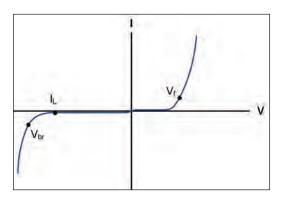

# 42 Testing modern power semiconductor devices requires modern curve tracers

The traditional curve tracer has significant limitations when it comes to testing modern power semiconductor devices. Fortunately, the Source Measure Unit (SMU) offers a capable test solution.

Front Cover designed by Mitch Gaynor

### industry research

14 Taking nanoscale lithography into the third dimension

- 16 Revolutionising electronics with nanotechnology

- 18 Simplifying MEMS pressure sensor technology

- 20 Desktop printing can process semiconductors on the nanoscale

- 22 Era of atomic-scale semiconductor devices

- 24 Scotch tape makes electronic devices smaller and better

### **NEWS** REVIEW

# Modutek partners with WRS on 450mm silicon reclaiming

MODUTEK CORPORATION is working with WRS Materials which provides silicon wafer polishing services, on a 450mm wafer cleaning development project. Richard Mee, President of WRS Materials, says, "Modutek Corporation's expertise on tank design and wet clean technology was crucial to our 450mm upgrade".

The new cleaning line will feature Modutek custom designed chemical baths that will incorporate Kiajo megasonics and custom wafer furniture capable of handling five 450mm wafers per fixture. Doug Wagner, President/CEO of Modutek Corporation, comments, "We were able to offer WRS new processing methods that will help them provide critical cost effective solutions to their customers. It will work to reduce the overall cost of the initial 450mm investments."

He goes on to say, "Our collaboration with WRS provided us the opportunity to utilise our custom designed semiconductor wet processing equipment and ensures they meet all SEMI standard requirements."

This new reclaim line is among the first in operation globally and will reclaim 450mm wafers for most of the blue chip OEM's. With a growing demand and the high cost of 450mm silicon wafers, reclaiming wafers will be a vital resource to the industry for many years to come. Worldwide, the 2011 reclaim wafer market was estimated at \$374 million and is expected to reach as high as \$413 million in 2013. "Technology advancements are driving higher quality standards, these new specifications demand constant investment in better tool sets, strong engineering support and improved training for our production staff. Fortunately we have found a willing partner in Modutek to help in all three areas", comments Richard Mee.

Wagner adds, "Modutek's Megasonic Cleaning Equipment offers a precision cleaning system that was developed for the unique requirements of the Semiconductor, FPD, Hard Disk, Solar and Crystal industries. Our engineers work closely with our customers to provide a solution for each specific application."

# Rudolph expands macro defect inspection series

RUDOLPH TECHNOLOGIES has launched its new NSX 220 automated macro defect inspection system. The company says its system, pictured above, provides fast, easy defect inspection for traditional back-end processes in the semiconductor, MEMS and LED market at a reduced price.

The NSX 220 tool joins the NSX 320 system in the NSX family of automated macro defect inspection and metrology systems for final manufacturing facilities. The first NSX 220 system was installed in July at a major outsourced assembly and test (OSAT) facility in Asia.

Mike Jost, vice president and general manager of Rudolph's Inspection Business Unit says, "The NSX 220 system is a streamlined version of our NSX 320 system.

The NSX 220 system is designed for traditional macro defect inspection of wafers up to 300mm at conventional semiconductor, MEMS and LED final manufacturing facilities, while the NSX 320 System serves next-generation advanced packaging processes with defect inspection and three-dimensional metrology for wafers up to 450mm." He continues, "The NSX 220 system benefits from many of the hardware and software innovations that made the NSX 320 system the market leader in advanced packaging, but is targeted for back-end facilities that do not need the full suite of capabilities offered by the NSX 320 System. Adding the NSX 220 system to the NSX family gives our customers a choice of best-in-class capabilities."

The NSX 220 is an automated macro defect inspection system that uses grey-scale image analysis (with colour image capture) to provide fast, accurate inspection and metrology in final manufacturing applications for wafers up to 300mm. It can detect traditional advanced macro defects such as scratches, mechanical damage, foreign materials, voids and probe damage, while also performing two-dimensional measurements on bumps, probe marks and edge trim processes.

The tool operates over a range of resolutions  $(10\mu m - 0.5\mu m)$  with both brightfield and optional darkfield illumination. The software platform, leveraged from the NSX 320 system's success, uses host-based image processing and delivers significant improvements in usability and

productivity over older-generation NSX series equipment. Using centrallymanaged recipe creation and editing, multiple NSX 220 tools can share a single recipe and be matched across the fab.

An optional suite of yield management software optimises the productivity of both the NSX 220 and 320 systems and minimises the need for operator assistance. Discover Software is designed for use with Rudolph inspection systems to allow real-time analysis for faster solutions and intelligent defect sampling for reduced offline review.

# New applications spur demand for thin layer deposition tools

THE GLOBAL MARKET for thin layer deposition equipment is projected to reach US\$ 18.5 billion by 2018.

This will be driven by emerging applications in medical imaging devices, specialty packaging and industrial coatings according to Global Industry Analysts' " Thin Layer Deposition Equipment: A Global Strategic Business," report. Defined as the building block of miniaturisation and MEMS processing, thin layer deposition is a critical part of the fabrication process and is key to the production of all electronic devices.

With surface treatment applications ranging from electronic components, electronic displays, optical coatings, and optical data storage devices to antistatic coatings, thin layer deposition is expected to witness strong growth in the coming years.

A significant portion of the growth is expected to stem from the robustly growing electronics industry. Developments in equipment design and performance, innovations in thin film materials and processes will also help spur growth.

Typically, demand for Thin Film Deposition (TFD) equipment is largely tied to the demand for semiconductors, electronics, and medical devices, among

# PVD system for 300mm power devices

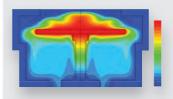

SPTS is to launch its Sigma fxP physical vapour deposition (PVD) system (shown below) for 300mm power device manufacturing. Available system options include modules for frontside thick aluminium processing and backside metal deposition on ultra-thin wafers. The new system is designed to address the technical challenges customers face as they scale power PVD processes up to 300mm wafer size.

In a discrete MOSFET power device, current passes through the silicon substrate so electrical contacts are required on both sides of the wafer. Due to the high currents involved, thick aluminium alloy layers are deposited on the front side of the wafer (typically over 4  $\mu$ m rather than less than 1  $\mu$ m for mainstream silicon interconnects).

However, depositing thick films puts unusually large heat loads on process chamber hardware, potentially resulting in film contamination from outgassing in the chamber furniture.

This contamination can lead to the formation of aluminium whiskers/ extrusions in the growing film that can ultimately result in device killer defects. In traditional front end fab deposition equipment, a common technique to mitigate this issue is to reduce film

deposition rates with a corresponding reduction on system productivity. However, SPTS says the Sigma fxP design overcomes that challenge without compromising throughput. Sigma fxP users routinely deposit thick aluminium layers at above 1.4  $\mu$ m/min without any yield destroying whiskers or extrusions.

With frontside processing complete, wafers are thinned down to 50  $\mu$ m or less to reduce 'on-state' resistance and solder metal layers are deposited on the backside. No supporting carrier substrates are used and the ultra-thin, large area wafer will deform under the influence of uncontrolled film stresses, with miss-handling a potential consequence.

The Sigma fxP carries thin wafer handling hardware and uses film deposition stress control techniques to deliver high throughput processes with low wafer bow. SPTS says that currently, seven out of the top ten power device manufacturers, and major foundries use the Sigma fxP as the process tool for power PVD processing.

With power device manufacturing moving to 300mm format wafers, SPTS has successfully transferred its process knowledge and capability to the new platform.

others. Periods of economic slowdown tend to curtail consumer spending thus impacting business opportunities in this market.

The capital intensiveness of the industry also makes investments a cyclical pattern with growth occurring largely during periods of intermittent revolutionary technology developments.

Atomic Layer Deposition (ALD) Equipment is set to witness considerable demand in the short to medium term period, with ALD process finding large-scale adoption in several end-use application areas.

For a long time, the ALD process has been utilised to generate thin films with different compositions such as nitrides, oxides, pure metals, and carbides among others.

The hallmark of this technology is its ability to produce monolayers on a molecular or atomic scale thus making it highly suitable for deposition of nanofilms with thickness less than 100 nm on various surfaces, including polymers, metals and ceramics.

ALD equipment is expected to witness increased adoption as a manipulation and fabrication tool in nanotechnology. What's more, the ALD equipment market is projected to witness increasing demand from non-IC and IC applications.

A marked trend towards miniaturisation of components is also driving the market, given the technology's proven efficiency in fabrication of smaller size components. Also, with semiconductor fabricators expected to invest in new manufacturing equipment, the market is forecast to witness tremendous opportunity in the coming years. ALD equipment will also find increased adoption in production of other advanced devices such as OLEDs.

The report says Asia-Pacific represents the largest and the fastest growing market with a projected CAGR of 4.9 percent over the analysis period. PVD equipment represents the largest product market.

### **NEWS** REVIEW

# JUSUNG to supply MRAM etching equipment to Crocus

JUSUNG ENGINEERING is to supply an integrated etch and deposition system for advanced MRAM technology to Crocus Nano Electronics (CNE).

Russian Based CNE is a joint venture founded by Crocus Technology, an MRAM semiconductor developer, and RUSNANO, a Russian state-owned international investment company. The supply agreement has a significant meaning to JUSUNG's global expansion strategy as the process technology was validated by Crocus Technology in the USA.

The Genaon Plus MRAM etching equipment to be supplied by JUSUNG is a core process tool that can etch non-volatile materials such as platinum, manganese and cobalt.

Conventional process tools cannot process such new materials that are used in advanced memory devices, making JUSUNG's Genaon Plus a unique enabling technology.

According to JUSUNG, the plasma etching equipment specialized for magnetic metal layers patterning, one of the most critical in MRAM processes, can completely eliminate polymer residue left behind on the side walls during the etching process, thereby enabling chip designers to utilise a variety of new materials.

As a low-power, high-density memory chip that combines storage capacity of flash memory and high speed of DRAM, MRAM is emerging as a next-generation memory. The MRAM market is engaging rapidly and is expected to grow to 925 billion Korean Won in 2018 globally.

JUSUNG is excited to participate at the early stage of such a high growth market. CJ Hwang, CEO of JUSUNG, comments, "We identified Crocus Technology as an ideal partner to launch our nextgeneration equipment. Crocus is an industry leader in the emerging market. While this is a new partnership for JUSUNG, our goal is unchanged to develop innovative technologies to delight our customers."

Boris Omarov, CEO of CROCUS NANO ELECTRONICS, adds, "We made the critical decision for CNE because Jusung is the leader in Magnetic Etch Technology. Jusung is the perfect partner for CNE and Russia, since they all share the same spirit of pacesetting and dedication to perfection."

# ARM acquires Cadence display tech

ARM, A SEMICONDUCTOR IP supplier, and Cadence Design Systems, Inc. an innovator in global electronic design, have signed a definitive agreement for the sale and transfer of Cadence PANTA display controller cores to ARM. The agreement enhances the companies' long-standing ecosystem collaboration and strengthens their technical alignment. Cadence's PANTA family of high-resolution display processor and scaling coprocessor IP cores was co-developed in conjunction with ARM and is targeted at advanced multimedia applications for high-end mobile devices with ultra-low power consumption. "Display technology is critical to the mobile consumer's user experience," says Pete Hutton, executive vice president and general manager, Media

Processing Division, ARM. "The addition of the PANTA family of display cores to the ARM product portfolio will help our ecosystem of partners get to market quickly with high-end displays that are fully integrated with ARM's leading Mali graphics and video solutions and protected with ARM TrustZone security."

Martin Lund, senior vice president of Cadence's IP Group, adds, "ARM and Cadence work together closely on many levels, including IP integration, verification IP (VIP) for all ARM AMBA protocols, and high-performance design solutions optimised for ARM cores.

As a result, both companies offer more tightly integrated solutions to our mutual customers."

# Cabot achieves multiple orders for logic devices

CABOT MICROELECTRONICS has announced that its "Novus A7100 Aluminum" CMP slurry products have been adopted by several customers to help enable 28/20 nanometre High-K Metal Gate integration schemes used for advanced logic devices. The Novus A7100 Aluminum slurry product platform is the result of Cabot Microelectronics' CMP technology and extensive research and development in close collaboration with strategic customers.

Novus A7100 contains a combination of unique engineered abrasive particles and proprietary chemistry to remove aluminium and the complex stack of work-function metals within the transistor gates of advanced semiconductor logic devices. This CMP solution was designed to polish aluminium and then stop on the underlying dielectric material and therefore minimise dielectric material erosion and aluminium recess. Novus A7100 is formulated to optimise removal rate, limit erosion and recess, and meet low defect requirements.

#### Charles Chen, Cabot

Microelectronics' Global Business Director, states, "The Novus A7100 Aluminum CMP slurry provides our customers with a solution for a critical process step in enabling High-K Metal Gate device integration at advanced technology nodes. We believe the extremely low recess levels that can be achieved across a wide range of feature sizes and densities, results in better device reliability and transistor performance."

Cabot Microelectronics Corporation, is a supplier of CMP polishing slurries and a growing CMP pad supplier to the semiconductor industry. The company's products play a critical role in the production of advanced semiconductor devices, enabling the manufacture of smaller, faster and more complex devices by its customers.

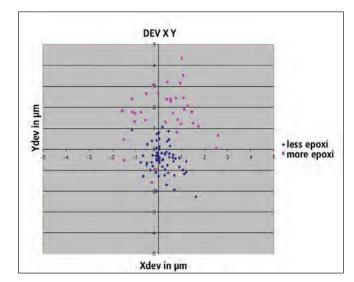

# Die and Flip Chip Bonding for Ultra High Precision

IWLPC, November 5-7, 2013, San Jose, CA Productronica, November, 12-15, 2013, Munich

# **AFC**<sup>PLUS</sup>

- Die Attach & Flip Chip System

- Fully automatic System

- ± 0,5 µm Placement accuracy

- Cycle time < 15 seconds</li>

- Working area up to 300 x 300 mm

# **NOVA**<sup>PLUS</sup>

- Die Attach & Flip Chip System

- Fully automatic System

- ± 2,5 µm Placement accuracy

- Cycle time < 3 seconds</li>

- Working area up to 600 x 600 mm

AMICRA MICROTECHNOLOGIES GMBH WERNERWERKSTR. 4 D-93049 REGENSBURG, GERMANY TEL: +49- 941-208209 0 E-MAIL: SALES@AMICRA.COM WWW.AMICRA.COM

MORE THAN PRECISION

### NEWS REVIEW

# Chip carrier packaging grows thanks to QFN

ADVANCED PACKAGING of semiconductor chips has emerged as a key enabler in many of today's electronic system products. Put another way, package selection is increasingly important to the success of the end product.

While much attention with regard to IC packaging is on 3D stacking and integration technologies, there is another area of packaging that has quietly been flourishing during the past decade and a half.

Introduced in 1998, the quad flat no-lead (QFN) package design (including the related dual-sided DFN) has enjoyed phenomenal growth from the very beginning. With its low cost, small size, and excellent thermal and electrical performance characteristics, the QFN quickly became the mainstream package of choice for many low-to-medium I/O count ICs.

In the past decade, new dual-row and even triple-row technologies have enabled QFNs to support many more I/ Os and, thus, enter a wider range of IC product segments. Today, the QFN is one of the most widely used IC package types.

IC Insights forecasts that the continuous high growth in demand for QFN-type packages will help push the flatpack/chip carrier (FP/CC) category of packages past the "old" small outline (SO) group of packages for the first time ever in 2013, as shown in the figure below.

The QFN is a type of chip carrier. The SO packages emerged in the early 1980s and then grew to become the industry's most widely used package type by 1995. The FP/CC packages emerged around the same time and they offered higher I/O capabilities than the SO packages because they had leads on all four sides.

The QFN package category in the JEDEC standards includes a variety of manufacturer-specific designs such as the MicroLeadFrame (MLF) package from Amkor, Fujitsu's Bumped Chip Carrier (BCC) and small outline no-lead (SON)

packages, Carsem's Micro Leadframe Package (MLP), and ASE's microchip carrier (MCC).

There are similar JEDEC standards for DFN packages that have external bond pads or "lands" on two sides instead of four like the QFN. Besides being categorised in the FP/CC group of packages, QFNs and DFNs are also considered part of a larger group of packages called leadframe CSPs, or chip-scale packages.

QFN and DFN packages are inexpensive to manufacture. They typically don't have solder balls, are targeted at low-I/O applications (typically less than 85), and make use of pre-plated leadframes. Either wirebonds or flip-chip bumps are used to attach the IC to the leadframe.

Versions like the MLF and BCC have an exposed die-attach paddle on the bottom of the package, which serves as an excellent thermal path away from the chip as well as a good ground-plane if the pad is grounded on the circuit board.

That, in conjunction with the high electrical performance offered by short I/O connections, has made these leadframe CSPs attractive for use in packaging RF circuits for cellphones and other wireless and portable product applications.

Many companies have migrated from SO-type packages to QFNs and DFNs and their popularity continues to spread as new advancements make QFNs/DFNs capable of handling a greater amount of circuitry and functionality.

# TSMC & Imagination to drive GPUs

IMAGINATION TECHNOLOGIES is working with TSMC to drive nextgeneration performance to new levels on Imagination's PowerVR GPUs.

Initial efforts have already achieved 25 percent overall performance improvements for the PowerVR Series6 GPU core, with key blocks demonstrating as much as 30 percent improvement compared to existing design flows. Imagination R&D teams working with TSMC are developing IP libraries and fully characterised reference system designs for Imagination's IP cores on TSMC's advanced processes including 28HPM and 16nm FinFET technologies. This collaboration will enable mutual customers to achieve significant performance gains for nextgeneration applications.

Imagination is tapping out an optimised next-generation multicore, multi-cluster PowerVR Series6 GPU design to characterise these performance improvements and plans to demonstrate a test chip later this year.

The resulting reference flow and optimised libraries will enable SoC designers to significantly accelerate time-to-market and increase performance for similar implementations of PowerVR Series6 GPUs.

Tony King-Smith, Imagination EVP marketing says, "The growing reliance on graphics processors to power the best user experiences means the GPU has become the new silicon process driver for the coming decade. It occupies as much as 50 percent or more of leading edge SoCs, and demands the highest performance memory bandwidth while always delivering high performance at low power. These characteristics are critical to defining the key device parameters of future generation processes.

# Samsung mass producing 20nm-class DDR4 memory chips

SAMSUNG ELECTRONICS is mass producing, what it claims, is the most advanced DDR4 memory chips, for enterprise servers in next-generation data centres. With the introduction of these high-density DDR4 modules, Samsung can better support the need for advanced DDR4 in rapidly expanding, large-scale data centres and other enterprise server applications.

Early market availability of the 4-gigabit (Gb) DDR4 devices, which use 20 nanometre (nm)-class process technology, will facilitate demand for 16-gigabyte (GB) and 32GB memory modules. This compares to conventional DRAM of which 8GB modules using a 30nm-class process technology are still commonplace.

"The adoption of ultra-high-speed DDR4 in next-generation server systems this year will initiate a push toward advanced premium memory across the enterprise," says Young-Hyun Jun, executive vice

president, memory sales & marketing, Samsung Electronics. "After providing cutting-edge performance with our timely supply of 16GB DDR3 earlier this year, we are continuing to extend the premium server market in 2013 and will now focus on higher density and added performance with 32GB DDR4, and contribute to even greater growth of the green IT market in 2014," he adds.

In next-generation enterprise servers, the use of higher speed DRAM raises system level performance and lowers overall power consumption significantly. By adopting DDR4 memory technology early, OEMs can minimise operational costs and maximise performance to provide more favourable returns on investments. Production of Samsung's 20nm-class 4Gb DDR4 follows the introduction of 50nm-class 2Gb DDR3 in 2008, culminating in a fully fledged transition to DDR4 for large-scale data centres and other enterprise applications in just five years.

Samsung says the 4Gb-based DDR4 has the fastest DRAM data transmission rate of 2,667 megabits per second - a 1.25fold increase over 20nm-class DDR3, while lowering power consumption by more than 30 percent. Based on Samsung's 20nm-class DRAM compact 4Gb DRAM chip, the company has now developed a new series of products tailored to applications from servers to mobile devices. This will provide global customers with the widest range of highly advanced low-power, high-performance green memory solutions.

# Process to improve 3D-IC / TSV packaging reliability revealed to industry

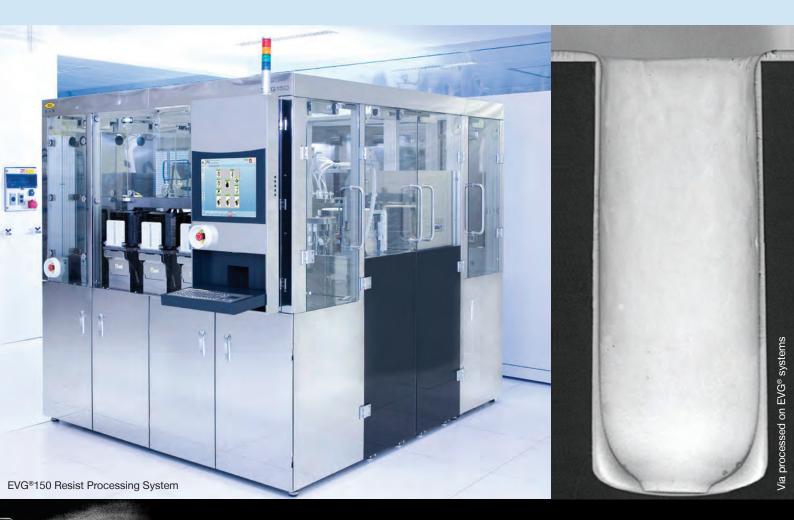

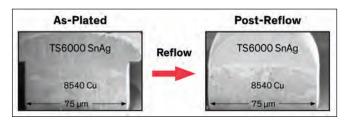

EV Group (EVG)has developed a new polymer via-filling process for 3D-IC/ through-silicon-via (TSV) semiconductor packaging applications.

Available on the EVG100 series of resist processing systems, the new NanoFill process provides void-free via filling of very deep trenches and high-aspect ratio structures, and is suitable for all common polymeric dielectrics-offering a highly flexible, low-cost and productionready via-fill platform for interposer development for 3D-integrated image sensors and other device types.

TSV interconnects are critical to the development of 3D-ICs since they enable through-chip communication between the vertically stacked device layers. Currently, most TSVs employ a solid copper via structure.

However, the mismatch in coefficient thermal expansion (CTE) between the copper via and the surrounding silicon can create a high amount of stress on the via structure, which results in long-term reliability issues.Replacing copper as the conducting material is not practical due to the general ease of use of the process. Also, the tooling infrastructure for copper is already well established.

However, replacing the solid copper via with a partial copper-plated via that is filled with a polymeric dielectric has been demonstrated to reduce CTE mismatch and stress, thus minimising reliability issues.

EVG's proprietary process and system enable simultaneous void-free via filling and dielectric redistribution layer (RDL) formation utilising a field-proven process technology that is compatible with all standard polymeric materials.

"3D packaging represents a fundamental change in the semiconductor industry that paves the way for continued advances in device performance and

cost reduction through 'More than Moore' approaches," states Markus Wimplinger, corporate technology development and IP director at EV Group.

"EV Group has made significant investments in our portfolio of wafer-level manufacturing solutions to add new products and capabilities, such as our NanoFill solution, to help our customers accelerate the commercialization of 3D-integrated devices."

### NEWS REVIEW

# ABI: Global semiconductor market to reach \$298 billion

THE WORLDWIDE semiconductor market is expected to grow 3 percent from 2012 to 2013. This is according to ABI Research's new "Worldwide Semiconductor Market -2Q13" Market Data report which tracks the market and market shares for the top 20 suppliers.

There has been sequential market growth from 1Q13 to 2Q13 and the vast majority of the top 20 vendors are expecting 3Q13 to experience revenue growth again.

"It has been a tough few years for the semiconductor industry. While we haven't seen a dramatic decline in overall revenues since the 2008/2009 period the market has been pretty stagnant since 2010," comments Peter Cooney, practice director.

He adds, "We will see some growth in 2013 as the wider economic environment improves but major market growth is not expected until later in 2014/early 2015."

Consolidation continues to be rife in the industry: a number of major mergers

and acquisitions are expected to take place in the second half of 2013; these include the merger of Fujitsu and Panasonic semiconductor divisions and the acquisition of Elpida by Micron. There have also been many smaller M&A transactions such as Intel's acquisition of ST-Ericsson GPS business and Broadcom's acquisition of Renesas Mobile's LTE assets as major vendors exit the mobile device semiconductor market.

"As the semiconductor market has been squeezed we have seen an increase in consolidation amongst the major players," adds Cooney. "Margins are falling and the competitive environment is tough - especially in the mobile device market - this is driving vendors to reevaluate their overall strategy and pull out of some of their once major markets."

He concludes, "We have seen a number of major vendors exit the mobile device market - Freescale, TI, STMicroelectronics, and Renesas and we expect there are more to come."

# Entegris & SEMATECH collaborate

Entegris and SEMATECH have partnered to move forward the development of advanced nanoscale particle removal processes and cleaning technologies for next-generation wafers and devices.

This collaboration will address some of the profound changes taking place in the semiconductor industry that are impacting fundamental aspects of process and equipment design as integration of new materials and process technology for sub-20nm node manufacturing, next-generation lithography requirements and the progression to 450mm wafers.

One key issue relates to the preparation of critical surfaces through the entire semiconductor manufacturing process. Entegris will work with experts from SEMATECH's Nanodefect Centre to develop new technologies and solutions to reduce nano-scale particle contamination during wafer processing. "We are pleased to partner with SEMATECH to provide early solutions for wafer surface cleaning," says Bertrand Loy, president and CEO of Entegris. "Our goal is to leverage our contamination control expertise to develop filtration and particle detection methods for the most advanced cleaning processes."

"SEMATECH's Nanodefect Centre aims to build industry participation in detecting, modelling, characterising, and providing solutions for defect issues as geometries shrink below the 10nm node," comments Michael Lercel, senior director of Nanodefectivity and Metrology.

"Our partnership with Entegris brings additional expertise to SEMATECH, and in turn will raise the level of our research efforts and further strengthen SEMATECH's commitment in identifying the challenges of future technology nodes."

# Finetech unveils high force bonder

FINETECH has developed a new high force configuration of its FINEPLACER pico ma platform targeting anisotropic conductive film (ACF) applications.

The tool achieves applied bonding forces of up to 700 N, which is critical to ensuring coherent and durable bonds between the chip and ACF to achieve higher signal densities and smaller overall packages.

Polymer-based ACF is used to create an electro-mechanical connection between two components. During ACF bonding, a combination of low temperature and high force is applied to the device, which activates the conductive spheres in the film.

ACF technology has traditionally been used in LCD or chip-on-glass (COG); additional target applications include flex-on-glass (FOG), flex-onboard (FOB), flex-on-flex (FOF), chipon-flex (COF) and chip-on-board (COB). "This new configuration showcases the continued flexibility of Finetech's FINEPLACER platform," says Neil O'Brien, Director, Finetech USA. "ACF bonding faces unique challenges, such as high density interconnects in an enlarged bond area combined with multi chip settings.

Addressing these requirements necessitates a system with a reinforced mechanical structure capable of applying high bonding forces. The new pico ma configuration increases the FINEPLACER's range of capabilities, further extending this modular bonding platform." The high force bonder integrates a novel 700 N bonding force module as well as a new multi-chip transfer station and precision z-hub positioning table for high forces. The transfer station allows up to 4 components to be placed simultaneously and bonded with defined distances.

MANDALAY BAY RESORT AND CONVENTION CENTER LAS VEGAS, NEVADA

# NEW IDEAS... For New Horizons

- TRUST in the expertise of IPC recognized worldwide as the leading standards organization for electronics manufacturing.

- EXPLORE emerging technologies and the latest innovations that will shape the future of our industry.

- COMPARE equipment, materials and supplies from more than 400 of our industry's top companies, in one location.

- LEARN about the latest research and processes that will advance your career and your company.

- BE INSPIRED with new ideas and approaches that will turn your vision into tomorrow's realities.

### REGISTER TODAY www.IPCAPEXEXPO.org

IPC APEX EXPO showed me innovative ideas in determining which technologies to use to improve operations.

David Souders Sr. Operations Product Transition Manager Rockwell Collins

DESIGN | PRINTED BOARDS | ELECTRONICS ASSEMBLY | TEST

# Taking **NANOSCALE** lithography into the third dimension

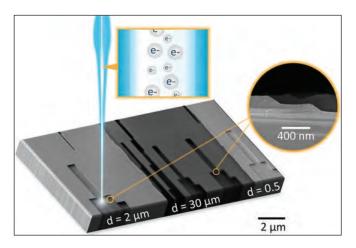

Using a combination of different techniques, researchers can etch trenches and other high aspect ratio structures with nanometre scale features without using masks.

ENGINEERS AT THE NIST CENTRE for Nanoscale Science and Technology (CNST) have developed a new technique for fabricating high aspect ratio three-dimensional (3D) nanostructures over large device areas. They used a combination of electron beam (e-beam) lithography, photolithography, and resist spray coating.

While it has long been possible to make complicated 3D structures with many mask layers or expensive grayscale masks, the new technique enables researchers to etch trenches and other high aspect ratio structures with nanometre scale features without using masks and in only two process stages. The fabrication of 3D semiconductor and dielectric structures that are patterned by exposing resist with varying intensity grayscale gradients has been essential to a broad range of applications such as digital lenses, micro-electromechanical systems, and fluidic medical devices.

Unlike devices that rely on conventional masks, which have areas that simply transmit or block light to form a pattern, the fabrication of these devices has typically relied on 3D grayscale masks which have varying levels of transparency and depend on the use of proprietary materials.

Because the chemistry is proprietary and because the masks are prepared using complicated processes best suited to small surface areas, they are often prohibitively expensive. The next generation of these devices requires lower costs, larger

surface areas, and ever-smaller feature sizes. The researchers' new approach capitalises on the high throughput capability of photolithography to generate large area grayscale structures with large processing flexibility and the ability of e-beam lithography to add grayscale features smaller than 200 nm. The first phase of this mix-and-match approach is to pattern a layer of photoresist by exposing it with a focused laser beam. By locally modulating the intensity of the light to form a grayscale gradient, varying levels of photoreaction in the photoresist are generated.

After the sample is immersed in the developer solution, material is dissolved in areas corresponding to the degree of induced photoreaction, leaving the photoresist layer with varying thicknesses matching the initial exposure pattern. The sample is exposed to a deep reactive ion etch (DRIE) which removes substrate material at varying depths that depend on the thickness of the photoresist, transferring the 3D photoresist pattern vertically into the substrate to form deep grayscale micro-structures. The second phase applies similar processing steps but with feature sizes ten times smaller.

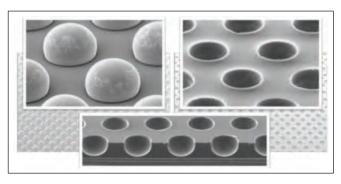

First, a high pressure e-beam resist spray coating is applied to obtain conformal coverage of the high-aspect ratio topography produced in the first phase. Then, by manipulating a high-energy e-beam with nanometre-scale resolution, patterned grayscale step heights are directly written in the e-beam resist in different locations. Finally, the resist is developed and the sample is exposed to DRIE as it was in the first step. The two stage process results in a vertical feature sizes of 45 ± 6 nm within a substrate structure that varies from 2  $\mu$ m to 30  $\mu$ m deep and with horizontal feature sizes of 100 nm to 200 nm and an overall pattern size potentially as large as a whole wafer.

The scanning electron micrograph (SEM) at the top of this article shows a top-view along with an SEM (inset) showing a cross-sectional view of grayscale structures fabricated using a combination of e-beam lithography, photolithography, and resist spray coating. The superimposed schematic illustrates e-beam direct writing of nanoscale vertical staircases (SEM inset) on a substrate with microscale grayscale topography. The initial grayscale patterns were generated on a laserwriter. After reactive ion beam etching, the patterns were simultaneously written into 2  $\mu$ m, 0.5  $\mu$ m, and 30  $\mu$ m deep features.

### **INDUSTRY** RESEARC

CNST NanoFab Process Engineer Liya Yu anticipates that the ability to fabricate high aspect-ratio grayscale nanostructures will expand the practical applications of grayscale lithography and dramatically widen the range of device structures available to device designers. This work is described further in the paper, "The evaluation of photo/e-beam complementary grayscale lithography for high topography 3D structure," by L. Yu et al in the Proceedings of SPIE 8682, 868212 (2013).

> © 2013 Angel Business Communications. Permission required.

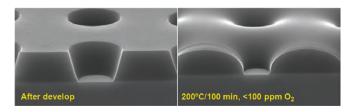

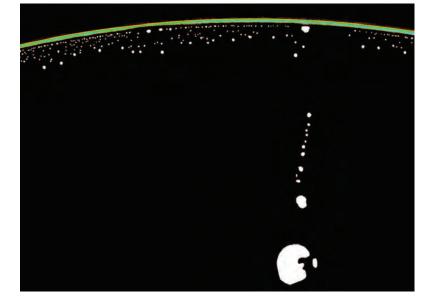

# Revolutionising CONSUMER electronics with nanotechnology

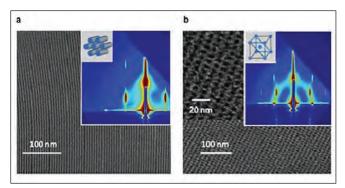

Nanopatterning, or self-assembling molecular materials, form an organised lithographic pattern on semiconductor crystals, for use as integrated circuits. Now newly developed materials, when integrated into electronics, will enable the development of ultra-lightweight, compact and efficient devices.

UNIVERSITY OF AKRON (UA) researchers have developed new materials that function on the nanoscale, which could lead to the creation of lighter laptops, slimmer televisions and crisper smartphone visual displays.

Known as "giant surfactants" - or surface films and liquid solutions - the researchers, led by Stephen Z.D. Cheng, dean of UA's College of Polymer Science and Polymer Engineering used a technique known as nanopatterning to combine functioning molecular nanoparticles with polymers to build these novel materials. Surfactants are compounds that lower the surface tension (or interfacial tension) between two liquids or between a liquid and a solid. Surfactants may act in a number of ways - as detergents, wetting agents, emulsifiers, foaming agents, or dispersants, to name a few.

The giant surfactants developed at UA are large, similar to macromolecules, yet they function like molecular surfactants on a nanoscale, Cheng says.

The outcome? Nanostructures that guide the size of electronic products.

Nanopatterning, or self-assembling molecular materials, is the genius behind the small, light and fast world of modern-day gadgetry, and now it has advanced one giant step thanks to the UA researchers who say these new materials, when integrated into electronics, will enable the development of ultra-lightweight, compact and efficient devices because of their unique structures.

During their self-assembly, molecules form an organised lithographic pattern on semiconductor crystals, for use as integrated circuits. Cheng explains that these self-assembling materials differ from common block copolymers (a portion of a macromolecule, comprising many units, that has at least one feature which is not present in the adjacent portions) because they organise themselves in a controllable manner at the molecular level.

"The IT industry wants microchips that are as small as possible so that they can manufacture smaller and faster devices," says Cheng, who also serves as the R.C. Musson and Trustees Professor of Polymer Science at UA. He points out that the current technique can produce the spacing of 22 nm only, and

cannot go down to the 10 nm or less necessary to create tiny, yet mighty, devices. The giant surfactants, however, can dictate smaller-scale electronic components.

"This is exactly what we are pursuing - self-assembling materials that organize at smaller sizes, say, less than 20 or even 10 nanometres," says Cheng, equating 20 nm to 1 /4,000th the diameter of a human hair.

An international team of experts from UA, Peking University in China, National Tsinghua University in Taiwan and McMaster University in Canada have shown how well-ordered nanostructures in various states, such as in thin films and in solution, offer extensive applications in nanotechnology. "These results are not only of pure scientific interest to the narrow group of scientists, but also important to a broad range of industry people," says Cheng, noting that his team is testing real-world applications in nanopatterning technologies and hope to see commercialisation in the future.

The team's study is highlighted in a pending patent application through the University of Akron Research Foundation and the

article, "Giant surfactants provide a versatile platform for sub-10nm nanostructure engineering" by Xinfei Yu et al, published in Proceedings of the National Academy of Sciences of the United States of America, 110, 10078-10083, 2013.

> © 2013 Angel Business Communications. Permission required.

Patterns of two giant surfactant samples in thin-film state

### **INDUSTRY** RESEARCH

# Simplifying MEMS pressure sensor technology

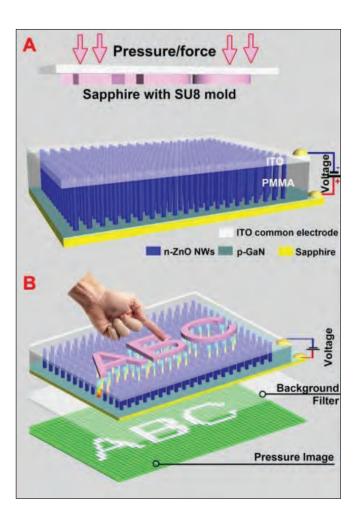

A new sensor incorporating gallium nitride and zinc oxide nanowires could provide an artificial sense of touch and be used in MEMS systems.

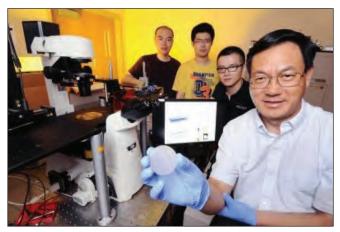

USING THOUSANDS OF nanometre-scale wires, researchers at the Georgia Institute of Technology have developed a sensor device that converts mechanical pressure - from a signature or a fingerprint - directly into light signals that can be captured and processed optically.

The sensor device could provide an artificial sense of touch, offering sensitivity comparable to that of the human skin. Beyond collecting signatures and fingerprints, the technique could also be used in micro-electromechanical (MEMS) systems and biological imaging. And ultimately, it could provide a new approach for human-machine interfaces.

"You can write with your pen and the sensor will optically detect what you write at high resolution and with a very fast response rate," says Zhong Lin Wang, Regents' professor and Hightower Chair in the School of Materials Science and Engineering at Georgia Tech. "This is a new principle for imaging force that uses parallel detection and avoids many of the complications of existing pressure sensors."

Individual zinc oxide (ZnO) nanowires that are part of the

Zhong Lin Wang holding the sensor device along with his research team in the background

device operate as tiny LEDS when placed under strain from the mechanical pressure. They allow the device to provide detailed information about the amount of pressure being applied. Known as piezo-phototronics, the technology - first described by Wang in 2009 - provides a new way to capture information about pressure applied at very high resolution: up to 6,300 dots per inch.

Piezoelectric materials generate a charge polarisation when they are placed under strain. The piezo-phototronic devices rely on that physical principle to tune and control the charge transport and recombination by the polarisation charges present at the ends of individual nanowires.

Grown on top of a gallium nitride (GaN) film, the nanowires create pixelled light emitters whose output varies with the pressure, creating an electroluminescent signal that can be integrated with on-chip photonics for data transmission, processing and recording.

"When you have a zinc oxide nanowire under strain, you create a piezoelectric charge at both ends which forms a piezoelectric potential," Wang explains. "The presence of the potential distorts the band structure in the wire, causing electrons to remain in the p-n junction longer and enhancing the efficiency of the LED.» The efficiency increase in the LED is proportional to the strain created.

Differences in the amount of strain applied translate to differences in light emitted from the root where the nanowires contact the GaN film. To fabricate the devices, a lowtemperature chemical growth technique is used to create a patterned array of ZnO nanowires on a GaN thin film substrate with the c-axis pointing upward.

The interfaces between the nanowires and the GaN film form the bottom surfaces of the nanowires. After infiltrating the space between nanowires with a PMMA thermoplastic, oxygen plasma is used to etch away the PMMA enough to expose the tops of the ZnO nanowires. A nickel-gold electrode is then used to form ohmic contact with the bottom gallium-nitride film, and a transparent indium-tin oxide (ITO) film is deposited on the top of the array to serve as a common electrode.

When pressure is applied to the device through handwriting, nanowires are compressed along their axial directions, creating a negative piezo-potential, while uncompressed nanowires have no potential.

A schematic showing a device for imaging pressure distribution by the piezo-phototronic effect is shown at the top of this article. It shows a nanowire-LED based pressure sensor array before (a) and after (b) applying a compressive strain. A convex character pattern, such as "ABC," molded on a sapphire substrate, is used to apply the pressure pattern on the top of the indium-tin oxide (ITO) electrode.

The researchers have pressed letters into the top of the device, which produces a corresponding light output from the bottom of the device. This output - which can all be read at the same time - can be processed and transmitted. The ability to see all of the emitters simultaneously allows the device to provide a quick response. "The response time is fast, and you can read a million pixels in a microsecond," says Wang.

When the light emission is created, it can be detected immediately with the optical fibre.

"The nanowires stop emitting light when the pressure is relieved. Switching from one mode to the other takes 90 milliseconds or less, Wang adds.

The researchers studied the stability and reproducibility of the sensor array by examining the light emitting intensity of the individual pixels under strain for 25 repetitive on-off cycles. They found that the output fluctuation was approximately 5 percent, much smaller than the overall level of the signal. The robustness of more than 20,000 pixels was studied.

A spatial resolution of 2.7  $\mu$ m was recorded from the device samples tested so far. Wang believes the resolution could be improved by reducing the diameter of the nanowires - allowing more nanowires to be grown - and by using a high-temperature fabrication process.

The researchers' study is described in detail in the paper, "High-

resolution electroluminescent imaging of pressure distribution using a piezoelectric nanowire LED array," by Caofeng Pan et al in Nature Photonics (2013), published online on 11th August 2013. DOI:10.1038/nphoton.2013.191

This research was sponsored by the U.S. Department of Energy's Office of Basic Energy Sciences, the National Science Foundation, and the Knowledge Innovation Program of the Chinese Academy of Sciences.

> © 2013 Angel Business Communications. Permission required.

When the light emission is created, it can be detected immediately with the optical fibre. The nanowires stop emitting light when the pressure is relieved. Switching from one mode to the other takes 90 milliseconds or less

# **Event Schedule**

Programs and Events: 7-10 October 2013 Exhibits: 8-10 October 2013 Messe Dresden, Germany

|                        | Expo                                           | TechARENA I                                                                                          | TechARENA 2                                                                                               | Со                                                                        |                                                    |

|------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------|

|                        | Ĕ                                              | Free Participation - Hall 1                                                                          | Free Participation - Hall 2                                                                               | MEMS                                                                      | Semico                                             |

| Monday<br>7 October    |                                                |                                                                                                      |                                                                                                           |                                                                           |                                                    |

|                        |                                                |                                                                                                      |                                                                                                           | International MEMS/MST<br>Industry Forum<br>Taking MEMS to the next level | 17 <sup>th</sup> Fab<br>Network                    |

| Tuesday<br>8 October   |                                                | <b>Packaging</b><br>Exhibitor Presentations                                                          | Emerging Research Materials<br>Session 1<br>Graphene and 2D                                               | International MEMS/MST<br>Industry Forum<br>Taking MEMS to the next level | <b>17<sup>th</sup> Fab</b><br>Wafer Fa<br>with inc |

| <b>u</b> 005           | Plastic Electronics<br>Exhibitor Presentations |                                                                                                      |                                                                                                           | novel en                                                                  |                                                    |

|                        | <b>Exhibition</b><br>10:00 – 17:00             | MEMS<br>Exhibitor Presentations                                                                      | Emerging Research Materials<br>Session 2                                                                  |                                                                           | <b>15<sup>th</sup> Euro</b><br>Test Cont           |

|                        |                                                | Secondary Equipment Session<br>- Invited Speakers<br>- Panel Discussion<br>- Exhibitor Presentations | New Trends in Epitaxy and<br>Atomic Layer Processing                                                      |                                                                           | A Reactiv                                          |

| Wednesday<br>9 October |                                                | Market Briefing                                                                                      | Silicon Photonics Session<br>Interconnecting at light speed                                               | MEMUNITY MEMS Testing<br>and Metrology Workshop                           | <b>15<sup>th</sup> Eur</b><br>Test Con             |

|                        | <b>tion</b><br>17:00                           |                                                                                                      |                                                                                                           |                                                                           | A Reacti                                           |

|                        | <b>Exhibition</b><br>10:00 – 17:00             | Test<br>Exhibitor Presentations                                                                      | <b>3D TSV Session:</b><br>The best of European 3D TSV                                                     | MEMUNITY MEMS Testing<br>and Metrology Workshop                           | <b>450mm</b><br>450mm:                             |

|                        |                                                | Best of APC Silicon Saxony                                                                           | Summit<br>- Invited Speakers<br>- Exhibitor Presentations                                                 |                                                                           | cooperat                                           |

|                        |                                                | Night of Knowledge                                                                                   |                                                                                                           |                                                                           |                                                    |

| Thursday<br>10 October |                                                | Lithography Session<br>- Invited Speakers<br>- Exhibitor Presentations                               | Workshop on Equipment<br>Assessment & Equipment<br>Performance Improvements<br>- Invited Speakers         |                                                                           | <b>450mm</b><br>450mm<br>cooperat                  |

|                        | <b>Exhibition</b><br>10:00 – 16:00             |                                                                                                      |                                                                                                           |                                                                           |                                                    |

| <b>Exh</b> i<br>10:00  | <b>Exhi</b> l<br>10:00 -                       |                                                                                                      | Process Control, Metrology,<br>Automation and Software<br>- Invited Speakers<br>- Exhibitor Presentations |                                                                           |                                                    |

|                        |                                                |                                                                                                      |                                                                                                           |                                                                           |                                                    |

| Sponsors:              |                                                | PLIED<br>ERIALS                                                                                      | Advanced<br>Technology Education                                                                          |                                                                           |                                                    |

| ferences                                                                      |                                                                                | Business & Market                                                                                                                                              | CONFERENCE                                                                                                                                                             | Standards Standards                            | Training    |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------|

| luctor & Test                                                                 | Packaging                                                                      |                                                                                                                                                                | www.plastic-electronics.org                                                                                                                                            | Free Participation                             |             |

| <b>anagers Forum</b><br>g Evening                                             |                                                                                |                                                                                                                                                                |                                                                                                                                                                        | PV Materials<br>PV Automation                  |             |

| anagers Forum<br>5 - Fit for the future<br>used flexibility and<br>gy concept |                                                                                |                                                                                                                                                                |                                                                                                                                                                        | Gases & Liquid Chemicals                       | echnology   |

| ean Manufacturing<br>ence (EMTC)<br>or Proactive Industry?                    | Advanced Packaging<br>Manufacturing Conference<br>The Power of Packaging       | Press Conference<br>7 <sup>th</sup> Executive Summit and<br>Reception<br>SAXONY! - Get Together                                                                | Plastic Electronics Conference<br>Plenary Session<br>Parallel Sessions<br>- OLED's for Displays and Lighting<br>- Flexible Photovoltaics<br>- Integrated Smart Systems | Gases & Liquid Chemicals<br>Silicon Wafer      | vanced Teo  |

| ean Manufacturing<br>ence (EMTC)<br>or Proactive Industry?                    | Advanced Packaging<br>Manufacturing Conference<br>The Power of Packaging       | Market Briefing<br>TechARENA 1                                                                                                                                 | Plastic Electronics Conference<br>Plenary Session                                                                                                                      | Equipment Automation<br>Compound Semiconductor | es in Ad    |

| <b>ssion</b><br>wards a global<br>n                                           | <b>3D TSV Session:</b><br>The best of European 3D TSV<br>Summit<br>TechARENA 2 |                                                                                                                                                                | Plastic Electronics Conference<br>Parallel Sessions<br>- OLED's for Displays and Lighting<br>- Flexible Photovoltaics<br>- Integrated Smart Systems<br>- Microdisplay  | Compound Semiconductor                         | Irone Cours |

| e <b>ssion</b><br>wwards a global<br>n                                        |                                                                                | SEMI Members and<br>Exhibitors Breakfast<br>EU Funding Opportunities<br>Workshop<br>What will the 10/100/20<br>strategy bring me?<br>Understanding upcoming EU | Plastic Electronics Conference<br>Parallel Sessions<br>- OLED's for Displays and Lighting<br>- Flexible Photovoltaics<br>- Integrated Smart Systems<br>Plenary Session | HB-LED<br>EHS                                  | CFI-Furo    |

|                                                                               |                                                                                | funding mechanisms                                                                                                                                             |                                                                                                                                                                        | HB-LED<br>Silicon Wafer                        |             |

Schedule is subject to change.

# Era of atomic-scale semiconductor devices

University develop new technique for creating high-quality semiconductor thin films at the atomic scale.

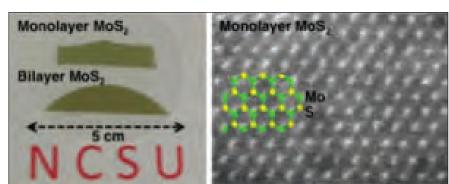

**RESEARCHERS AT NORTH CAROLINA** STATE UNIVERSITY have developed a new technique for creating high-quality semiconductor thin films at the atomic scale -- meaning the films are only one atom thick. The technique can be used to create these thin films on a large scale, sufficient to coat wafers that are two inches wide, or larger.

"This could be used to scale current semiconductor technologies down to the atomic scale -- lasers, lightemitting diodes (LEDs), computer chips, anything," says Dr. Linyou Cao, an assistant professor of materials science and engineering at NC State and senior author of a paper on the work. "People have been talking about this concept for a long time, but it wasn't possible. With this discovery, I think it's possible."

The researchers worked with molybdenum sulphide (MoS2), an inexpensive semiconductor material with electronic and optical properties similar to materials already used in the semiconductor industry.

However, MoS2 is different from other semiconductor materials because it can be "grown" in layers only one atom thick without compromising its properties. In the new technique, researchers place sulphur and molybdenum chloride powders in a furnace and gradually raise the temperature to 850 degrees Celsius, which vaporizes the powder. The two substances react at high temperatures to form MoS2. While still under high temperatures, the vapor is then deposited in a thin layer onto the substrate.

"The key to our success is the development of a new growth mechanism, a self-limiting growth," Cao says. The researchers can precisely control the thickness of the MoS2 layer by controlling the partial pressure and vapour pressure in the furnace.

Partial pressure is the tendency of atoms or molecules suspended in the air to condense into a solid and settle onto the substrate. Vapour pressure is the tendency of solid atoms or molecules on the substrate to vaporize and rise into the air.

To create a single layer of MoS2 on the substrate, the partial pressure must be higher than the vapour pressure. The higher the partial pressure, the more

Monolayer MoS, Monolayer MoS Bilayer MoS,

layers of MoS2 will settle to the bottom. If the partial pressure is higher than the vapour pressure of a single layer of atoms on the substrate, but not higher than the vapour pressure of two layers, the balance between the partial pressure and the vapour pressure can ensure that thin-film growth automatically stops once the monolayer is formed. Cao calls this "self-limiting" growth. Partial pressure is controlled by adjusting the amount of molybdenum chloride in the furnace -the more molybdenum is in the furnace, the higher the partial pressure.

"Using this technique, we can create wafer-scale MoS2 monolayer thin films, one atom thick, every time," Cao says. "We can also produce layers that are two, three or four atoms thick."

Cao's team is now trying to find ways to create similar thin films in which each atomic layer is made of a different material. Cao is also working to create field-effect transistors and LEDs using the technique. Cao has filed a patent on the new technique.

© 2013 Angel Business Communications. Permission required.

#### Journal Reference:

Yifei Yu, Chun Li, Yi Liu, Liqin Su, Yong Zhang, Linyou Cao.Controlled Scalable Synthesis of Uniform, High-Quality Monolayer and Few-layer MoS2 Films. Scientific Reports, 2013; 3 DOI: 10.1038/srep01866 North Carolina State University (2013, May 22). New technique may open up an era of atomic-scale semiconductor devices. ScienceDaily.

# Instrumental in change

# Leading plasma process innovation

Oxford Instruments Plasma Technology is turning smart science into world class products with its flexible systems for precise and repeatable etching, deposition and growth of micro and nano structures

Plasma Etch & Deposition

Atomic Layer Deposition

Ion Beam Etch & Deposition

Deep Silicon Etch

For more information, please contact Oxford Instruments Plasma Technology: **Tel:** +44 (0)1934 837 000 **Email:** plasma@oxinst.com

### www.oxford-instruments.com/plasma

**Transfer valve for 450 mm wafer technology** L-MOTION valve for corrosive high-end semiconductor applications

Real L-MOTION valve technology assures uniform seal compression

- Excellent gate seal lifetime