## SILICON SEMICONDUCTOR

Connecting the Silicon Semiconductor Community

Volume 36 Issue 2 2014

📴 @siliconsemi

www.siliconsemiconductor.net

### Directed self assembly

### Wafer cleaning legislation

Getting more out of graphene

Chip spending increases

MEMS microphones

## LITHOGRAPHY SOLUTIONS FOR HIGH-VOLUME MANUFACTURING

- Advanced Packaging for Logic and Memory

- Ultra-High Throughput and Productivity

- Mid-End and Back-End Interconnect Applications

## executiveVieW

by Rich Rogoff, Vice President and General Manager, Lithography Systems Group, Rudolph Technologies, Inc.

#### We must think "outside of the box" for new approaches in advanced packaging

AS SEMICONDUCTOR DEVICES have continued to shrink in size and grow in complexity, manufacturers have had to develop advanced packaging techniques to accommodate the rapidly increasing number and density of connections required to communicate with the outside world. Often these technologies have developed as adaptations of front-end methods. While there is certainly value to be found in using these well characterized processes, we must be careful not to carry along old baggage that may prove unnecessary in the

For instance, while front-end manufacturing has historically been tied to round silicon wafers, this may not be the ideal shape and material for advanced packaging substrates. Embedded die, fan-out and interposer based packages can often be manufactured more conveniently and efficiently on larger, rectangular substrates made of glass, molded or organic panels. Our ability to think "outside of the box" for new approaches in advanced packaging will enable economy of scale efficiency gains and cost savings in the future.

Moving from round wafers to rectangular substrates in backend advanced packaging saves corner space, delivering a roughly 10% improvement in surface utilization. In the case of lithography, the larger size of the substrate and the improved fit between the reticle and substrate can reduce the handling and processing overhead by a factor of five. These productivity improvements more than offset any potential reduction in throughput resulting from an increase in the number of alignment points required for these larger substrates.

The net result is a substantial reduction in lithography cost of ownership. Compared to a 1X stepper exposing round silicon wafers, processes based on rectangular substrates can reduce lithography cost per die by as much as 40%.

> Clearly, there are many aspects of these new processes that must be addressed before they gain broad acceptance. However, if we as an industry are able to think outside of the box, we will see that the potential economic benefits of rectangular substrate processing can be significant.

News Editor Dr. Su Westwater Director of SEMI Publishing Jackie Cannon

Senior Sales Executive Robin Halder

Sales Manager Shehzad Munshi

new application.

USA Representatives Tom Brun Brun Media

Janice Jenkins

Director of Logistics Sharon Cowley

Design & Production Manager Mitchell Gaynor

Circulation Director Jan Smoothy

suwestwater@angelbc.com iackie.cannon@angelbc.com +44 (0)1923 690205 robin.halder@angelbc.com +44 (0)2476 718109 shehzad.munshi@angelbc.com +44 (0)1923 690215 E: tbrun@brunmedia.com Tel: 724 539-2404 E: iienkins@brunmedia.com Tel: 724-929-3550 sharon.cowley@angelbc.com +44 (0)1923 690200 mitch.gaynor@angelbc.com +44 (0)1923 690214 jan.smoothy@angelbc.com +44 (0)1923 690200

Circulation & Subscriptions Assistant Annette Weatherilt

Chief Operating Officer Stephen Whitehurst

annette.weatherilt@angelbc.com +44 (0)1923 690220 stephen.whitehurst@angelbc.com +44 (0)2476 718970

Directors Bill Dunlop Uprichard - CEO, Stephen Whitehurst - COO, Jan Smoothy - CFO, Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal, Jason Holloway

Published by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford Herts WD17 1.IA LIK

T: +44 (0)1923 690200 F: +44 (0)1923 690201 E: ask@angelbc.com

Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road,

T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com

Silicon Semiconductor is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2014. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor (ISSN 1096-598X) is published four times a year for a subscription of \$198 by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Herts WD17 1JA, UK. Periodicals postage paid at Rahway, NJ. POSTMASTER: send address changes to: Silicon Semiconductor, c/o Mercury International Ltd, 365 Blair Road, Avenel, NJ 07001. Printed by: Pensord Press.

© Copyright 2014. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online).

## connecting the silicon semiconductor community

## features

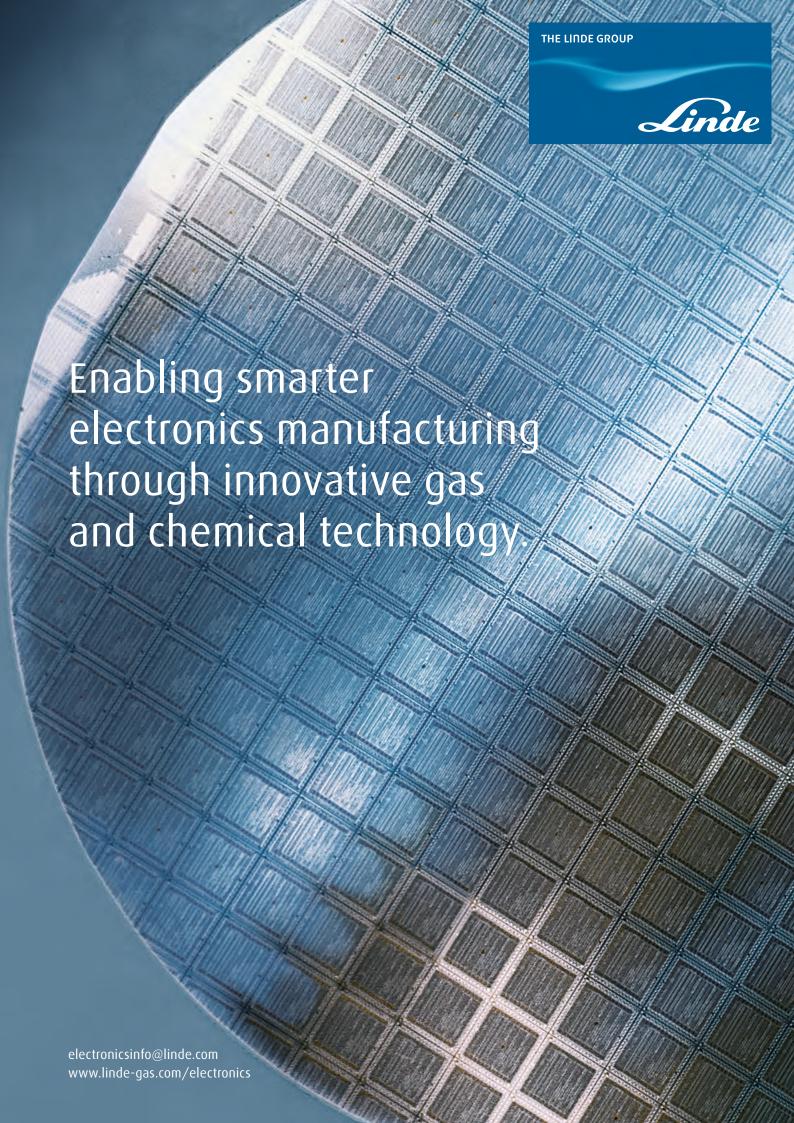

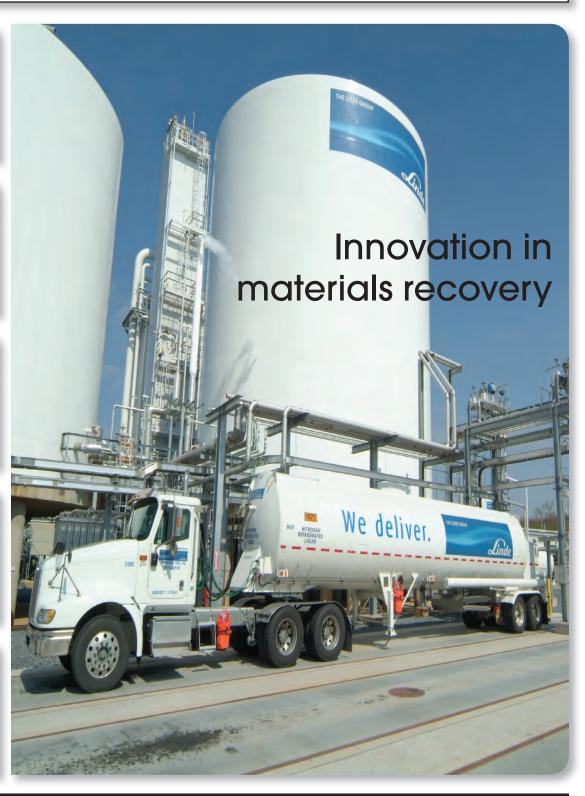

#### 26 Innovation in materials recovery

The Linde Group explores the complex procedures deployed to sustain a secure and reliable supply of material in the electronics Industry

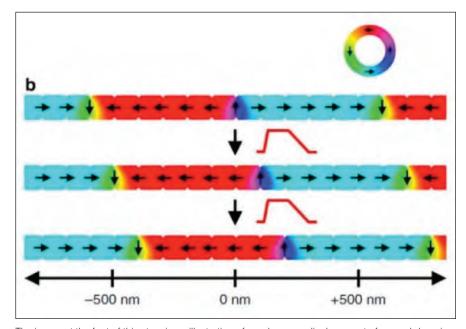

#### 30 DSA: the next-generation patterning technology?

Directed self-assembly or DSA has become an attractive technique for generating fine lithographic patterns in chip manufacturing processes. But is the technique ready for chip manufacturing? And will it ever replace conventional optical lithography?

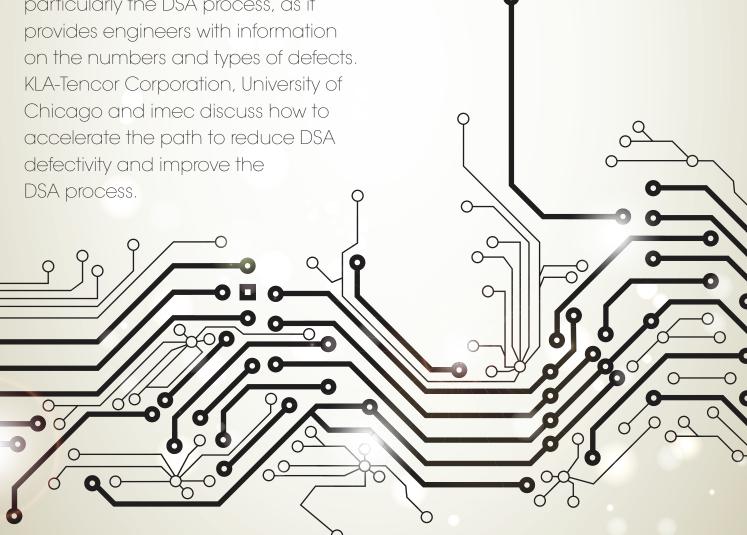

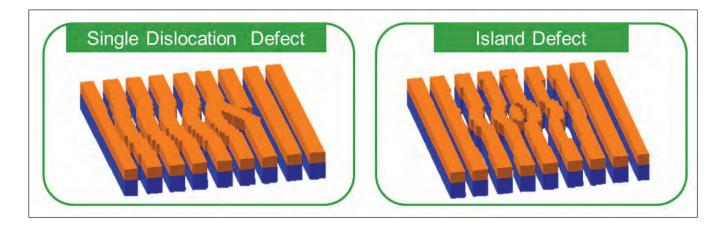

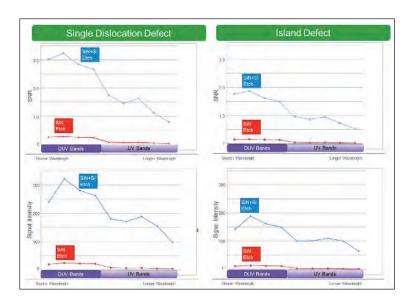

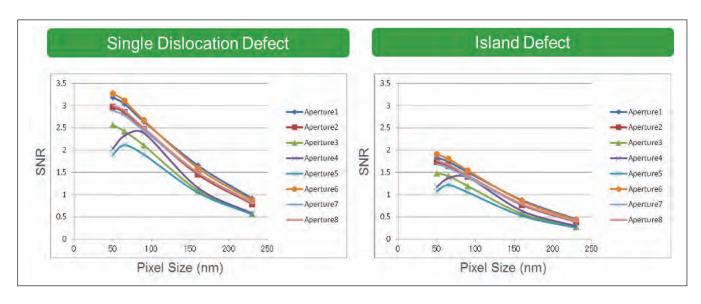

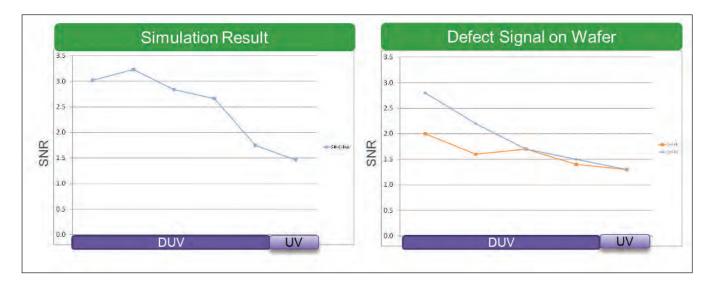

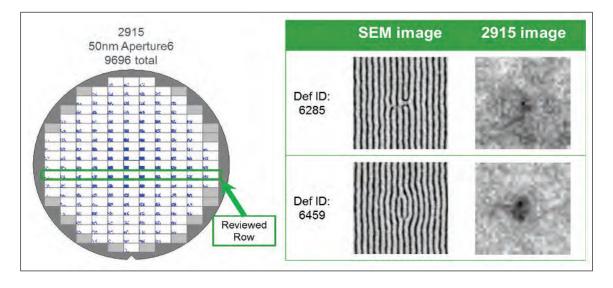

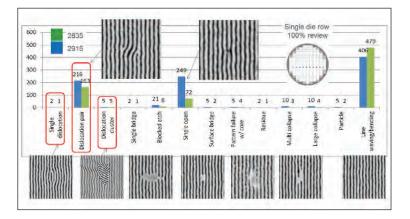

#### 34 Inspection of directed selfassembly defects

One of the challenges for translating DSA into high volume manufacturing is to achieve low defect density in the DSA patterning process. How can the path to reduce DSA defectivity and mprove the DSA process be accelerated?

#### 40 Wafer cleaning: the latest legislation and the options

As products are becoming increasingly complex and advanced, cleaning becomes more challenging: 3M tells us why the continued reduction in size components means contaminants can no longer be ignored

#### Industry analysis

- 12 Semiconductor market for vehicles to quadruple

- 14 Apple and Samsung top MEMS microphone buyers

- 16 Samsung, Intel & TSMC to top spending in CapEx

- 18 SEMI: Fab equipment spending recovering

- 20 Taiwan tops semiconductor equipment sales again

#### Industry research

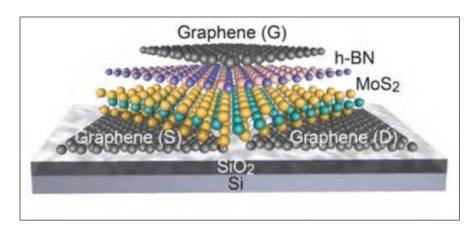

- 42 2D self-assembling material may produce transistors

- 44 2D transistors take on silicon to speed up electronics

- 45 Creating nanowires three atoms wide with electron

- 46 Domain walls in nanowires enhance data storage

#### MEMs review

- 22 PacTech doubles capacity in Asia

- 22 Plasma-Therm enhances NASA's fabrication capability

- 24 Automotive accelerometer can make emergency calls

- 24 DelfMEMS secures \$7.4 million funding

#### News

- 06 Three companies to accelerate 28-nm FD-SOI adoption

- 07 Samsung 32-layer 3D V-NAND flash first in production

- 08 Soitec and Simgui provide China with 200mm SOI wafers

- 10 AMAT Introduces big materials change

- 11 Brewer Science commercialises megasonic for MEMS

## Synopsys, ST and Samsung to accelerate 28-nm FD-SOI adoption

SYNOPSYS has extended its collaboration with STMicroelectronics to include Samsung Electronics, enabling broader market adoption of ST's 28-nm FD-SOI technology for SoC design.

Synopsys says its Galaxy Design Platform is production-proven on multiple designs based on ST's 28-nm FD-SOI technology. This collaboration extends the Galaxy design flow to Samsung in support of its strategic agreement to offer dual sourcing of ST's 28-nm FD-SOI technology.

Developed over a multiyear collaboration with ST, the design flow enables concurrent area, power and timing optimisations to enable engineers to optimise their designs for the ST 28-nm FD-SOI process.

"The close collaboration between ST design teams and Synopsys led to advanced silicon-proven design enablement solutions that fully leverage the performance and power promise of FD-SOI technology and provide the foundation needed to meet tight time

to market windows," says Philippe Magarshack, executive vice president, Design Enablement and Services, STMicroelectronics.

"Our close collaboration with Synopsys has already enabled many successful tapeouts with mutual customers using Synopsys' Galaxy Design Platform and Lynx Design System."

The Synopsys design flow for ST's 28-nm FD-SOI is compatible with the Lynx Design System, a full-chip design environment providing innovative automation and visualisation capabilities that enable higher designer productivity and faster design closure.

A technology plug-in using ST's 28nm FD-SOI Process Design Kit (PDK), standard cells and memories, adapts the production-proven Galaxy Design Platform-based RTL-to-GDSII flow for 28-nm FD-SOI SoC designs, accelerating project setup and execution.

Lynx automation simplifies and accelerates many critical implementation

and validation tasks, including back-bias management across the flow, special connection checks, In-Design physical verification for well connections and UPF supply set management for n-wells and p-wells.

Galaxy advanced design enablement features like the IC Compiler tool's concurrent clock and data optimization, layer-aware optimization, physical datapath and comprehensive support for hierarchical and low power design features can also be directly accessed by Lynx users for high-performance and low power CPU and GPU design.

"28-nm FD-SOI is an ideal solution for customers looking for extra performance and power efficiency at the 28-nm node without having to migrate to 20-nm," says Shawn Han, vice president of foundry marketing, Samsung Electronics.

"Our close collaboration with Synopsys and ST will enable designers to reduce risk, accelerate time-to-market, minimise power and maximise performance to expand 28-nm FD-SOI adoption."

#### Nordson MARCH unveils plasma tool for flexible substrates

NORDSON MARCH is introducing its new FlexVIA-Plus Plasma Treatment System that delivers single-stage plasma processing - including etchback and desmear - of up to 30 panels (panel size 500 x 813 mm/ 20 x 32 inch) per cycle.

This enables a rate of as much as 200 units per hour (UPH) for the manufacture of flexible electronic PCBs and substrates.

The FlexVIA-Plus System's advanced horizontal electrode design, with integrated rack, provides optimum material alignment for industry-leading plasma treatment uniformity. V

ersatile horizontal racks allow for processing of various flexible PCB sizes and make loading easy. The efficient design with its economical gas consumption and small footprint contributes to a low cost of ownership.

Specifically designed for the processing of flexible PCBs, the new FlexVIA-Plus Plasma System delivers patented, plasma technologies that provide excellent surface activation, etchback, and desmear process uniformity on both sides of the flex material.

The desmear and etchback technologies remove epoxies, polyimides, high Tg blends, mixed materials and other resins more effectively than traditional methods of etching and desmearing.

The descum capabilities effectively remove resist residue from inner layers and panels as well as residual solder mask bleed for better bonding and solderability. Temperature-controlled electrodes ensure consistent process repeatability.

"The new FlexVIA-Plus Plasma System performs similarly to our ProVIA system, but in a horizontal form-factor, which is ideal for processing flexible PCBs," says Jonathan Doan, director of marketing, Nordson MARCH. "This system meets the demands of today's high-throughput flexible circuit board manufacturing operations."

### Samsung 32-layer 3D V-NAND flash first in mass production

SAMSUNG has begun mass producing what it says is the industry's first threedimensional (3D) V-NAND Flash memory using 32 vertically stacked cell layers. This is the firm's second generation V-NAND offering.

The firm's 32-layer 3D V-NAND - or Vertical NAND - requires a higher level of design technology to stack the cell arrays than the previous 24-layer V-NAND, yet delivers much greater production efficiency. This is because Samsung can use essentially the same equipment it used for production of the first generation V-NAND.

In addition, Samsung has just launched a line-up of premium SSDs based on its 2nd generation V-NAND Flash memory with 128 gigabyte (GB), 256GB, 512GB and 1TB storage options. After introducing 3D V-NAND-based SSDs to data centres last year, Samsung is now extending its V-NAND SSD line-up to high-end PC applications, in expanding its market base.

"We increased the availability of our 3D V-NAND by introducing an extensive V-NAND SSD line-up that covers the PC market in addition to data centres,"

says Young-Hyun Jun, executive vice president, memory sales and marketing, Samsung Electronics. "Look for us to provide a consistent, timely supply of high-performance, high-density V-NAND SSDs as well as core V-NAND chips for IT customers globally, contributing to fast market adoption of 3D NAND technology."

The new 3D V-NAND-based SSDs have approximately twice the endurance for writing data and consume 20 percent less power, compared to planar (2D) MLC NAND-based drives. Later this year, Samsung will introduce additional premium 3D-based SSDs based on this 2nd generation V-NAND memory with even higher reliability and higher-density in satisfying a diversity of customer

#### Equipment spending soars 22.5 percent in April 2014

NORTH AMERICA-BASED manufacturers of semiconductor equipment posted \$1.44 billion in global orders in April 2014 and a book-to-bill ratio of 1.03, according to the April EMDS Book-to-Bill Report published by SEMI.

This was based on a three-month average. A book-to-bill of 1.03 means that \$103 worth of orders were received for every \$100 of product billed for the month.

The three-month average of worldwide bookings in April 2014 was \$1.44 billion. The bookings figure is 10.8 percent higher than the final March 2014 level of \$1.30 billion, and is 22.5 percent higher

than the April 2013 order level of \$1.17 billion. The three-month average of worldwide billings in April 2014 was \$1.40 billion. The billings figure is 14.1 percent higher than the final March 2014 level of \$1.23 billion, and is 28.7 percent higher than the April 2013 billings level of \$1.09 billion.

"Sales of semiconductor manufacturing equipment from North American producers continue to demonstrate strong sequential and year-over-year growth," says Denny McGuirk, president and CEO of SEMI. "The data through the first quarter reflects momentum in memory, foundry, and back-end spending."

Moscone Center, Booth 6260

#### **High precision** Die & Flip Chip Bonder

## PLUS

- Dual Bond Head system

- Die Attach & Flip Chip System

- Fully automatic System

- ± 2,5 µm Placement accuracy

- Cycle time < 3 seconds

- Working area up to 600 x 600 mm

- Large area FanOut capability

- · High bond force option for TCB application

Amicra Microtechnologies GmbH Wernerwerkstr. 4 D-93049 Regensburg, Germany Tel: +49- 941-208209 0 e-mail: sales@amicra.com www.amicra.com

**MORE THAN PRECISION**

### Soitec and Simgui to provide China with 200mm SOI wafers

SOITEC and Shanghai Simgui Technology Co., Ltd. (Simgui), a Chinese materials company, have formed an international partnership.

They will address both China's growing demand and limited worldwide production capacity for 200 mm siliconon-insulator (SOI) wafers used in fabricating semiconductors for radiofrequency (RF) and power applications. In addition to giving Soitec its first wafer production capability in China, the agreement boosts the industrial manufacturing capacity of SOI wafers to meet increasing worldwide usage and represents the first step in establishing a SOI ecosystem in China.

The newly signed deal includes a licensing and technology transfer agreement under which Simgui will manufacture Soitec's 200 mm SOI wafers using Soitec's proprietary Smart Cut technology. Simgui will establish a highvolume SOI manufacturing line to directly supply the Chinese market.

In addition, Simgui will manufacture Soitec's 200 mm SOI wafers for the global market outside China, expanding Soitec's supply to customers worldwide. Beyond this initial cooperation, the two companies plan to expand their collaborative efforts in the future to take advantage of their synergies.

"We are very pleased to announce this partnership with Simgui which amplifies the ecosystem using Soitec's technology and reinforces our competitive offer," says Paul Boudre, COO of Soitec. "While paving the way for future cooperation between our two companies, it also reinforces Soitec's global leadership position in SOI and immediately bolsters our presence in the Chinese market."

Commenting on the announcement, Bernard Aspar, general manager of Soitec's Communication and Power Business Unit, says, "In addition to Soitec's SOI product volume for the RF market doubling in the last two years, the products themselves are becoming the preferred solutions for RF switches embedded in smart phones and tablets. This collaboration with Simgui

will allow us to respond to the fastgrowing demand we are seeing from our customers."

"Considering that China takes over a 60 percent market share of the worldwide semiconductor market, to have a strategic collaboration with Soitec is very important to us," notes Xi Wang, Chairman of Shanghai Simgui Technology Co., Ltd. "This will enable us to grow our current SOI market share and address new opportunities as we help to develop China's SOI ecosystem." "The access to Soitec technology is an accelerator for Simgui to become a key player in thin SOI manufacturing," adds Feng Zhang, General Manager of Simgui. "On the other hand, this partnership will complete Simgui's capabilities such as Simbond, which will further strengthen both parties' SOI competitiveness."

This strategic partnership enables both Soitec and Simgui to strengthen their positions in the high-growth markets for RF and power semiconductors. While applications for power ICs include automotive electronics, lighting and power supplies, RF semiconductors are key drivers of 4G smart phones. China is the world's largest smart phone market. Soitec's RF-SOI products are already used in manufacturing by most of the leading RF foundries and have been adopted as the preferred substrates for 4G and LTE mobile computing and communication applications.

# Optimize the Thermal Performance of your Process Equipment.

Extensive computational tools enable product designs to be highly refined for ultimate performance.

Multi-zone circuit layouts in a polyimide construction are highly customized to deliver exacting performance up to 250°C.

EZ-ZONE® RM Multiloop controllers are fully scalable with up to 152 PID Loops and 256 monitor points per system. Atlow provides innovative solutions to help process tool manufacturers meet the needs of the semiconductor technology roadmap. Our approach is to work collaboratively to help solve complex thermal challenges associated with state-of-theart manufacturing processes; helping to improve yield, throughput and cost of ownership. This includes innovative heaters, controllers and sensors for use in front-end and back-end applications such as CVD, PECVD, Etch, Diffusion, Bonding, IC test and more.

ASSURANT™ gas and pump line heaters feature high temperature capabilities with low outgassing.

Contact Watlow® today for the latest thermal solutions for semiconductor applications.

European Technical Sales Offices

**Germany** +49 (0) 7253-9400-0

info@watlow.de

France +33 1 41 32 79 70 info@watlow.fr

Italy

+39 02 4588841 italyinfo@watlow.com

Spain +3

+34 91 675 1292 info@watlow.es

UK

+44 (0) 115-964-0777 info@watlow.co.uk

### AMAT Introduces big materials change

APPLIED MATERIALS, INC. has announced the Applied Endura Volta CVD Cobalt system, a tool capable of encapsulating copper interconnects in logic chips beyond the 28nm node by depositing precise, thin cobalt films. The two enabling applications, a conformal cobalt liner and a selective cobalt capping layer, provide enclosure of the copper lines. The introduction of cobalt, as a metal encapsulation film, marks the most significant materials change to the interconnect in over 15 years, the company says.

"The reliability and performance of the wiring that connects the billions of transistors in a chip is critical to achieve high yields for device manufacturers. As wire dimensions shrink to keep pace with Moore's Law, interconnects are more prone to killer voids and electromigration failures," said Dr. Randhir Thakur, executive vice president and general manager of the Silicon Systems Group at Applied Materials. "The Endura Volta system builds on Applied's precision materials engineering leadership by delivering CVD- based cobalt liner and selective cobalt capping films that overcome these yield-limiting issues to

enable our customers to scale copper interconnects to beyond the 28nm node."

The Endura Volta CVD system, with two new process steps, represents technology extension for copper interconnects beyond 28nm. The first step involves the deposition of a thin, conformal CVD cobalt liner to increase the gap fill window of copper in narrow interconnects. This process improves the performance and yield of the device by integrating the pre-clean, PVD barrier,

CVD cobalt liner and copper seed processes under ultra-high vacuum on the same platform. The second step, a new "selective" CVD cobalt capping step, is deposited after CMP\* to encapsulate the copper lines for enhanced reliability performance.

Complete envelopment of copper lines with cobalt creates an engineered interface that demonstrates over 80x improvement in device reliability the company says.

#### Breakthrough defect reductions in EUV mask blanks

SEMATECH has announced that researchers have reached a significant milestone in reducing tool-generated defects from the multi-layer deposition of mask blanks used for extreme ultraviolet (EUV) lithography, pushing the technology another step toward readiness for high-volume manufacturing (HVM).

Following a four-year effort to improve deposition tool hardware, process parameters and substrate cleaning techniques, technologists at SEMATECH have, for the first time, deposited EUV multilayers with zero defects per mask at 100 nm sensitivity (SiO2 equivalent). Eliminating these large "killer" defects is essential for the use of EUV in early product development. These results were achieved on a 40 bi-layer Si/Mo film stack and measured over the entire mask blank quality area of 132×132 mm<sup>2</sup>.

In addition, by subtracting out, incoming substrate defects, SEMATECH has demonstrated that the multilayer deposition process itself can achieve zero defects down to 50 nm sensitivity. Coupled with novel improvements to the mask substrate cleaning process to remove incoming defects, this represents the capability to both extend EUV to future nodes by eliminating smaller "killer" defects, and as a step to reducing smaller defects (which can be mitigated) to a level where improved yield and mask cost make EUV a more costeffective HVM technology. Defects are generally created by the deposition process or formed by decoration of substrate defects during the multilayer deposition process. These types of defects have prevented the quality of mask blanks from keeping pace with roadmap requirements for the production of pilot line and high-volume manufacturing EUV reticles. Reducing defects in the EUV mask blank multilayer deposition system is one of the most critical technology gaps the industry needs to address to enable cost-effective insertion of this technology at the 16 nm

"A low defect density reflective mask blank is considered to be one of the top two critical technology gaps for the commercialization of EUV," said Frank Goodwin, manager of SEMATECH's Advanced Mask Development program. "Through sophisticated defect analysis capabilities and processes, the goal of our work is to enable model-based prediction and datadriven analysis of defect performance for process improvement and component learning. We then use these models to feed into the new deposition tool design."

SEMATECH's Advanced Mask Blank Development program is located at the SUNY College of Nanoscale Science and Engineering (CNSE) in Albany, New York to develop defect-free EUV blanks.

### Brewer Science commercialises megasonic developer for MEMS

BREWER SCIENCE has announced the first commercial placement of a Cee 300MXD megasonic developer. This innovative developer was commissioned by MicroChem Corp.

The Brewer Science Cee 300MXD megasonic developer applies uniform acoustic energy to spinning substrates to gently dissolve and remove films and residues without damaging fragile device structures.

This precision handling results in stable dimensional control of vertical profiles uniformly across the wafer surface, enabling fabrication of highaspect-ratio structures for the MEMS, display, compound semiconductor, and advanced packaging markets. Applications include radio-frequency (RF) power, MEMS, sensors, and acoustic wave devices used for wireless communication.

"MicroChem is very pleased to team with Brewer Science on what we believe could be an enabling technology for the future," said Michael Stan, Applications

Engineering Manager for MicroChem Corp. "As the MEMS industry and integrated packaging technology continue to demand higher-aspectratio structures for TSV and RDL layers, enhanced development techniques will

likely become mainstream. The costeffective approach being pioneered by Brewer Science gives a supplier such as MicroChem Corp. the advantage of being able to rapidly prototype formulations and processes to meet these demands," he added.

"The Cee 300MXD developer features state-of-the-art technology that creates a viable pathway for our customers to decrease process cycle times, reduce cost of ownership, and accelerate time to market," said Justin Furse, Brewer Science Equipment Technology

The Cee 300MXD megasonic developer gives customers an ideal bridge from the lab to production by allowing them to avoid significant capital investment.

Our semi-automated equipment delivers quality and precision comparable to automatic multimillion-dollar tools and is suitable for low-volume prototyping with a seamless transition to high-volume manufacturing.

#### AlT unveils advanced 20 micron die-attach film

AI TECHNOLOGY (AIT) says it has solved one of the technically more challenging problems in wafer level semiconductor packaging.

The company says it can achieve conductive die-attach film adhesive (DAF) of 20 microns (µm) thickness. While die-attach film adhesive (DAF) at the wafer level is becoming more prevalent in die-attach for memory modules in precision bonding and thin packages, thermally conductive and electrically conductive die-attach film is more limiting because of the challenging handling and performance issues for the thinner conductive DAF.

The picture shows 20 µm thick conductive DAF used for high power devices and concentrated solar die-attach applications. AIT's conductive DAF is built on the same self-supporting dieattach film (DAF) adhesive technology

that the company pioneered in the 1990's. AIT is now able to produce ESP8660-HK in 20µm thickness for power devices from microprocessors to concentrated solar die-attach modules. This new thickness marks an improvement over AIT's 50µm thick ESP8660-HF which was first produced in 2005.

ESP866-HF can be produced in wafer-shape die-cut format and prelaminated on dicing tape (DDAF) format up to widths of 450mm and lengths of 100 metres in AIT's clean room manufacturing environment housed in the company 's 16 acres facilities in Princeton Junction, New Jersey. Not only is ESP8660-HK available in 20µm thickness, it is also developed for high glass transition requirements to facilitate faster wire-bonding at temperatures as high as 250 C. ESP8660-HK is also molecularly

engineered to reduce stress and ultimately improve the reliability of multi-chip module (MCM) and system in package (SIP) devices. In addition to achieving one of the lowest thermal resistances with thermal conductivity of over 8 W m/ K, ESP8660-HK maintains its bond strength after 85%RH/85 C and demonstrates reliability test results after thermal cycling an d shock that are not common even for traditional paste dieattach adhesives.

Semiconductor market for

## vehicles

to quadruple

THE GLOBAL SEMICONDUCTOR MARKET for active-control systems in the autonomous vehicle will grow nearly fivefold in just seven short years, according to a new report from IHS Technology. This expansion will be driven by an increasing shift from cars simply providing alerts in hazardous situations to direct intervention in order to avoid accidents.

WORLDWIDE REVENUE for active-control systems in vehicles is set to reach \$883.9 million in 2020, up from \$187.3 million last year. The increase of nearly \$700 million from 2013 to 2020 equates to a compound annual growth rate of 25 percent for the seven-year period. This year alone, revenue is projected to climb a robust 31 percent to \$246.1 million, as shown in the attached table.

Active-control mechanisms can be distinguished from their passive-warning counterparts - older systems that have been around much longer - by the degree of driver involvement in both systems.

"Passive mechanisms in the autonomous vehicle help identify potentially hazardous conditions, but the driver is still fully responsible for avoiding an incident," says Akhilesh Kona, analyst for automotive semiconductors. "In active-control systems, however, the mechanism takes over if the driver does not react to warnings so that the vehicle can avoid an accident or minimise the impact of a collision."

An example of a passive mechanism is lane-departure warning, which monitors the lane markings on a roadway and alerts a driver when a car starts veering out of its lane if the turn signals are not being used. In this case, the driver must still take control of the car and steer the vehicle back to its proper lane.

But in an active-control mechanism such as lane-keep assist, the car acts in more proactive fashion: if the driver does not respond after an initial warning from the car, the car itself typically takes action to keep the vehicle from drifting.

Another example of an active-control mechanism is automatic emergency braking (AEB), which uses forward-looking radar and video systems to detect the relative speeds of vehicles to determine if a collision is imminent. If a potential collision is detected, the vehicle applies full or partial braking power to stop the car or slows it down significantly in order to mitigate the severity of the collision.

"Overall, active-control systems are growing faster than passivewarning mechanisms. Compared to the phenomenal growth of the active-control semiconductor market, the chip market for passive-warning systems is projected to grow at a less furious pace from 2013 to 2020," notes Luca DeAmbroggi, principal analyst for automotive semiconductors at IHS.

"The semiconductors used for active-control systems need to be compliant with stringent safety certifications, such as Automotive Safety Integrity Level (ASIL), or ISO 26262," DeAmbroggi adds. "Since safety considerations are of paramount importance to active-control semiconductors throughout their life cycle, ASIL systems will require compliant chips that will typically cost more than the standard ASIL counterparts used in passive systems."

ASIL-compliant microcomponents (MCU) will enjoy even faster growth than overall semiconductors for active-control systems, with ASIL revenue growing to \$450 million in 2020 from \$70 million in 2013. These findings are contained in the report, "ADAS Semiconductor Market Tracker H1-14," from the Automotive & Transportation research area of IHS. Automotive radar sensors are highly effective in implementing active-control functions such as AEB or automatic cruise control, but an alternative approach is also possible through the use of optical sensors along with powerful processors. Ultimately, the vehicle manufacturer's preference is the deciding factor for the type of sensor used in the application.

In general AEB can be implemented with just one type of sensor, but implementation also depends on the ASIL targeted for the system deployed. For higher levels of ASIL certification, the preferred solution is a radar sensor, backed by an optical sensor as a redundant approach. AEB is likely to be promoted in the near future as a mandatory feature for light vehicles, which would provide a higher level of protection in affordably priced cars.

In Europe, the New Car Assessment Program (NCAP) is encouraging car makers to implement AEB for pedestrian detection and to help vehicles avoid collisions with other vulnerable road users, including cyclists and animals. Vehicle manufacturers are already planning for their cars to support AEB systems, with the aim of obtaining a five-star rating from the European program. Based in Brussels, Belgium, the NCAP is patterned after the American model created by the U.S. National Highway Traffic and Safety Administration, evaluating new vehicle designs for safety and performance threats.

Given the European program's call to action, global semiconductor revenue for pedestrian-detection systems is projected to climb as well in the coming years, rising from just \$2 million in 2013 to \$400 million in 2020. The next 20 years will require an entire ecosystem for autonomous vehicles to be in place in order to be successful, IHS believes. Specifically, mandates, regulations and legislations will need to be shared among different countries, and infrastructure surrounding vehicles must also figure into the equation.

#### Apple and Samsung top MEMS

## microphone

**buyers**

Microelectromechanical systems (MEMS) microphones, used in best-selling devices like Apple's iPhone, face a resonant future as the market keeps climbing in the coming years, according to a new report from IHS Technology.

GLOBAL REVENUE FOR MEMS microphones is forecast to reach \$1.04 billion this year, up a robust 24 percent from \$836.9 million in 2013.

Less than a decade was needed for the MEMS microphone market to cross the billion-dollar threshold. While this year continues the galloping growth the industry has seen during the last few years, the rate of expansion is slowing as revenue has expanded.

Even so, the next few years will continue to yield solid results for the business, and revenue by 2017 will amount to a projected \$1.37 billion, equivalent to a

five-year compound annual growth rate (CAGR) of 18 percent from 2012 to 2017. Shipments at the end of the forecast window will equal 5.4 billion units, up from 1.9 billion in 2012.

"The MEMS microphone segment has successfully capitalised on the value delivered by audible improvements in microphones to propel the industry forward," says Marwan Boustany, senior analyst for MEMS & sensors at IHS. "Especially in an age in which devices are increasingly uniform, sound can be a real and important differentiator, in features such as voice command or crystal-clear audio in high-definition

#### **INDUSTRY** ANALYSIS

videoqualities that are possible only through high-performance MEMS microphones."

Handsets and tablets account for the majority of MEMS microphone consumption, and Apple and Samsung are the biggest buyers at present, Boustany noted. These findings are contained in the report, "MEMS and Sensors Report - Microphones - 2014," from the Semiconductors & Components service of IHS.

Two of the main measures for MEMS

microphone quality are signal-to-noise ratio (SNR) and the maximum soundpressure level (SPL). These define the lowest and highest sound levels, respectively—or dynamic range—that can be gauged by a microphone with a linear response. The measures apply to both analog and digital MEMS microphones, and have been used as the basis for microphone quality in marketing by firms such as Nokia and

At the top performance level, very-high-SNR microphones feature a signal-tonoise ratio level of greater than, or equal to, 64 decibels. These

> are the microphones projected to have the greatest growth in the coming years, with an estimated five-year CAGR of 40 percent from 2012 to 2017, IHS analysis shows.

In the past, low-SNR microphones, featuring a signal-to-noise ratio of less than 60 decibels, were the standard device in many handsets. Acceptable for phone calls, low-SNR microphones have shown their limitations in performance, as in cases where there is some distance between the source of the recorded sound and the microphone, such as for video recording and voice commands. In such instances, low-SNR microphones can miss out on lower volume elements of the sound, which can result in a loss of data important for voice commands and a degradation of the richness in recorded sounds for video.

Low-SNR microphones are also not up to the task of ambient-noise cancellation, in which the microphones help to neutralize surrounding noise levels in order to better focus on the immediate sound intended for transmission or reception. Here, better-SNR microphones are the key factor as well to an improved listening experience, Boustany

> Very-high-SNR microphones were first used in 2012 by Apple in the iPhone 5, and subsequent generations of the popular smartphone continued to utilize these MEMS microphones. After Apple, Samsung joined in,

using very-high-SNR MEMS microphones in its S4 and Note 3 flagship handsets. Together the two brands made up 96 percent of revenue for the very-high-SNR MEMS microphone market in 2013.

Another advantage of very-high-SNR microphones is enhanced support for voice commands, helpful for Apple's Siri or Google Now. The Motorola Moto X, for instance, includes multiple very-high-SNR microphones that improve the handset's ability to capture voice commands.

Between the very-high-SNR and low-SNR categories sits a third class of MEMS microphones, the high-SNR devices with a signal-to-noise ratio between 59 and 64 decibels, which will be what lower midrange devices may choose to transition from low-SNR microphones. Growth of this segment during the next few years will be lower than that of very-high-SNR types, but higher than in the low-SNR segment that is headed for decline.

MEMS microphones are deployed the most in handsets and tablets, which last year accounted for 93 percent of revenue in very-high-SNR microphones. Apple and Samsung each have up to three microphones for their handsets that could possibly climb to four, and the multiple numbers no doubt help increase overall revenue for MEMS suppliers.

The rapidly growing tablet space is also a vigorous market driver, with the Apple iPad product line now outfitted with two microphones and with Samsung also adding multiple microphones to some of its tablets.

Very-high-SNR microphones are making inroads into hearing aids, too. The ReSound LiNX, for instance, uses two such devices, for noise cancellation and improved performance, with an additional beneficial capability that ties in Bluetooth connectivity with an iPhone - enabling the hearing aid to act as a headset as well.

High-performance MEMS microphones will also become increasingly prominent in the automotive space, helping support voice commands and hands-free calling. Harman has announced the use of two MEMS microphones for such use in Germany's Daimler vehicles, to start in

## Samsung, Intel & TSMC

to top spending in CapEx

ACCORDING TO IC Insights Samsung and Intel are both forecast to spend at least \$11.0 billion this year, and TSMC slightly less than \$10.0 billion on capex. Collectively the three companies are forecast to account for 51.8 percent of total semiconductor industry capex this year.

As amazing as that number is, it is a decrease from the 55.5 percent share these three companies held in 2013. Among the top 10, six companies are forecast to spend at least \$3.0 billion in 2014, and nine suppliers are forecast to spend more than \$1.0 billion. After keeping their combined spending essentially flat in 2013, the top 10 spenders are forecast to boost capex spending by 10 percent in 2014.

After chopping its capital spending by 28 percent in 2012 and 12 percent in 2013, SanDisk is forecast to show the largest capital spending percentage increase (86 percent) among the top 10. The company stated that this large increase is needed to expand production of advanced 3D NAND flash memory with its manufacturing partner Toshiba.

While SanDisk's capital spending level is expected to be much higher than in 2013, this increased spending is not expected to result in a significant boost to its NAND Flash capacity levels. It is worth noting that the combined capex spending increase of Toshiba and SanDisk (on account of their joint venture partnership to build flash memory) is forecast to be \$1.06 billion in 2014.

Capital spending budgets are forecast

to increase by \$1.0 billion or more at two companies. Micron is expected to be very aggressive by increasing its spending \$1.12 billion in 2014.

Still, this 58 percent jump in spending is forecast to be less than the 88 percent jump in sales revenue the company logged in 2013 (after the inclusion of Elpida's sales).

Also, pure-play foundry GlobalFoundries is expected to increase its semiconductor

capital spending by \$1.0 billion as well this year. SK Hynix is expected to display an 18 percent increase in spending in 2014. However, given the company's excellent sales performance in 2013 (43 percent growth) and its aggressive rebuilding program for its fire-damaged China DRAM fab, IC Insights believes there is potential upside to this estimate.

Some of the most eye-catching numbers are the massive amounts of spending expected by Samsung and Intel over the

2012-2014 time period.

Over this three-year period, Samsung is forecast to spend \$35.3 billion, with about 60 percent of this amount targeting memory production.

Intel is forecast to be second to Samsung in total outlays over this same time with \$32.6 billion in dedicated to capital expenditures.

These huge levels of spending are enough for each company to construct

and equip eight or nine \$4.0 billion leading-edge 300mm wafer fabs. Nine of the top 10 semiconductor industry capital spenders are expected to increase their semiconductor capital expenditures in 2014. In contrast, only four of the top 10 capital spenders increased their spending levels in 2013.

Meanwhile, capex spending among "other" suppliers is expected to grow at a much slower 3 percent rate this year, but that is a marked improvement from

the 15 percent decline registered by the "other" segment in 2013.

In the long run, IC Insights believes that "other" companies will likely increase their spending at a lower rate, or decrease their spending at a higher rate, as compared to the top 10 companies as they implement the fabless or "fab-lite" business models for their IC production.

## **SEMI:** Fab equipment spending recovering

AFTER TWO YEARS OF DECLINE in terms of equipment spending, 2015 may reach or even surpass historic record year 2011 (about US \$39.8 billion).

For the May 2014 SEMI World Fab Forecast publication, SEMI tracked more than 200 major projects involving equipment spending for new equipment or upgrades, as well as projects to build new facilities or refurbish existing facilities. In the last three months, 265 updates were made to the database. The latest data is shown in the table below.

In 2014, the three largest regions for fab equipment spending will be Taiwan with over US \$10.3 billion, the Americas with over US \$6.8 billion, and Korea with over US \$6.3 billion. In 2015, these same regions will lead in spending. Taiwan is anticipated to spend over US \$11 billion, Korea over US \$8 billion, and the Americas almost US \$7 billion. Although in sixth in regional equipment spending this year, the Europe/Mideast region will show the strongest rate of growth, about 79 percent compared to the previous year. The same region will continue to grow fast in 2015, with an increase of about 20 percent.

Worldwide installed capacity is very low for both 2014 and 2015 and the SEMI data does not suggest that this will change over the next four years. Because of the increased complexity of leading-edge nodes, such as more process steps and multiple patterning, fabs experience a decline in capacity as the same fab space produces less.

Worldwide, installed capacity grew by less than 2 percent in 2013 and is expected to grow just 2.5 percent in 2014

and 3 percent in 2015. SEMI's detailed data predict that Foundry capacity continues to grow at 8 to 10 percent yearly (a steady pace since 2012) and Flash is up 3 to 4 percent for 2014. Although DRAM equipment spending is expected to grow by 40 percent in 2014 as many fabs upgrade to a leading-edge process, installed capacity for DRAM is expected to stay flat or even drop 2 percent.

SEMI's reports also cover capacity changes for other product segments: MPU, Logic, Analogue/Mixed signal, Power, Discretes, MEMS, and LED and Opto.

The SEMI World Fab Forecast uses a bottom-up approach methodology, providing high-level summaries and graphs, and in-depth analyses of capital expenditures, capacities, technology and products by fab. In addition, the database provides forecasts for the next 18 months by quarter. These tools are invaluable for understanding how the semiconductor manufacturing will look in 2014 and 2015, and learning more about capex for construction projects, fab equipping, technology levels, and products.

The SEMI Worldwide Semiconductor Equipment Market Subscription data tracks only new equipment for fabs and test and assembly and packaging houses. The SEMI World Fab Forecast and its related Fab Database reports track any equipment needed to ramp fabs, upgrade technology nodes, and expand or change wafer size, including new equipment, used equipment, or in-house equipment.

| 2014F<br>Rank | Company            | 2012<br>(\$M) | 2013<br>(\$M) | 13/12%<br>Change | 2014F<br>(\$M) | 14/13 %<br>Change | 2012-2014F<br>(\$M) |

|---------------|--------------------|---------------|---------------|------------------|----------------|-------------------|---------------------|

| 1             | Samsung            | 12,225        | 11,560        | -5%              | 11,500         | -1%               | 35,285              |

| 2             | Intel              | 11,000        | 10,611        | -4%              | 11,000         | 4%                | 32,611              |

| 3             | TSMC*              | 8,341         | 9,709         | 16%              | 9,750          | 0%                | 27,800              |

| 4             | GlobalFoundries    | 3,800         | 4,500         | 18%              | 5,500          | 22%               | 13,800              |

| 5             | SK Hynix           | 3,363         | 3,146         | -6%              | 3,700          | 18%               | 10,209              |

| 6             | Micron             | 2,184         | 1,935         | -11%             | 3,050          | 58%               | 7,169               |

| 7             | Toshiba            | 1,137         | 1,630         | 43%              | 1,950          | 20%               | 4,717               |

| 8             | SanDisk            | 979           | 859           | -12%             | 1,600          | 86%               | 3,438               |

| 9             | UMC*               | 1,770         | 1,098         | -38%             | 1,200          | 9%                | 4,068               |

| 10            | SMIC*              | 499           | 651           | 30%              | 880            | 35%               | 2,030               |

| -             | Top 10 Total       | 45,298        | 45,699        | 1%               | 50,130         | 10%               | 141,127             |

| -             | Others             | 13,742        | 11,731        | -15%             | 12,100         | 3%                | 37,573              |

| -             | Total Cap Spending | 59,040        | 57,430        | -3%              | 62,230         | 8%                | 178,700             |

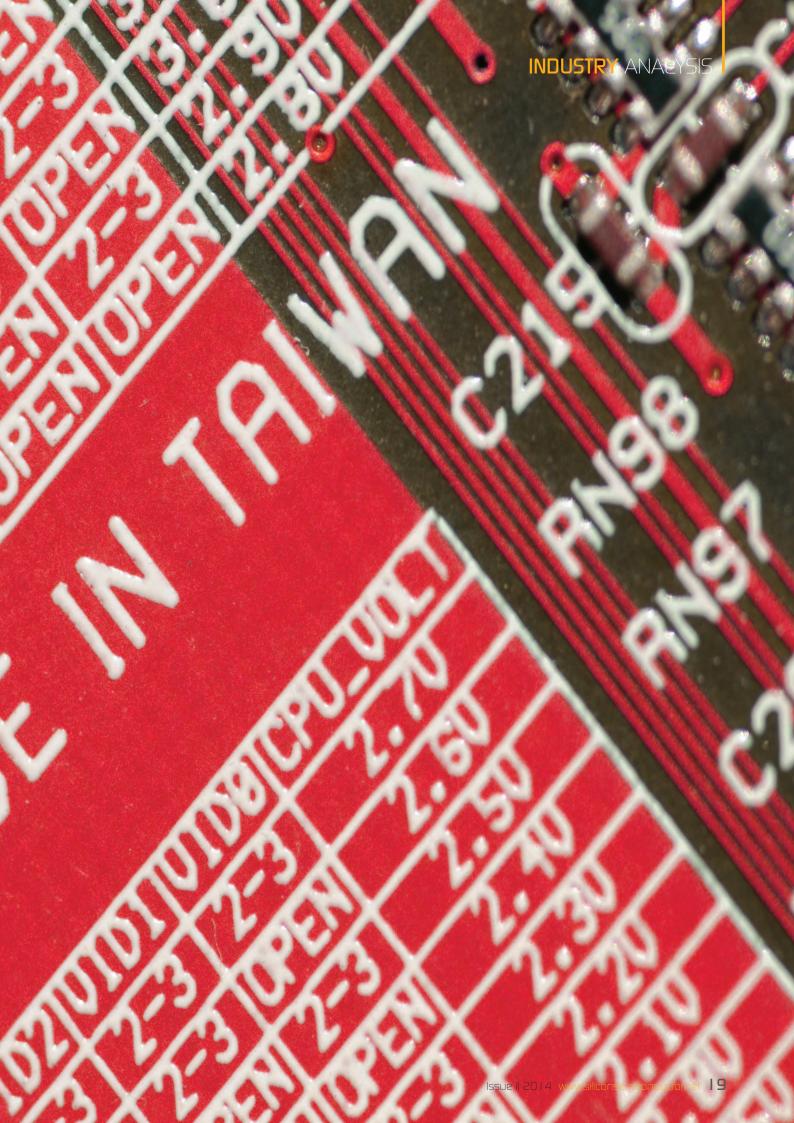

## Taiwan tops semiconductor equipment sales again

SEMI has reported that worldwide sales of semiconductor manufacturing equipment hit \$31.58 billion in 2013 compared to \$36.93 billion in sales posted in 2012. This represents a year-over-year decrease of 14 percent. This is cited in the "Worldwide Semiconductor Equipment Market Statistics (SEMS) Report," by SEMI. Categories covered include wafer processing, assembly and packaging, test, and other front-end equipment. Other front-end includes mask/reticle manufacturing, wafer manufacturing, and fab facilities equipment.

Spending rates declined for all the regions tracked in the WWSEMS report, except for China and Taiwan. For the second year in a row Taiwan remained the region with the highest

amount of spending with \$10.57 billion in equipment sales. The North American market surpassed South Korea to claim the second place with \$5.26 billion in sales; South Korea fell to the third position with a regional decrease of 41 percent.

The global other front end equipment segment decreased 34 percent; the assembly and packaging segment decreased 26 percent; total test equipment sales decreased 24 percent; and the wafer processing equipment market segment decreased by 11 percent.

#### **IR Vacuum Reflow Soldering/RT**

over 400 worldwide over 100 in USA

**IR Vacuum Reflow** Table Top System 450°C / 700°C

dispenser, tester, repair

450°C 1100°C

200 mm ø

Hot Plates/Chucks 450°C IGBT/DCB prozessing

sealing with Getter activation

Email: ATV@bsetplasmas.com • Antioch, CA, USA • Phone: 925-755-2300 • www.bsetplasmas.com/atv.html • www.atv-tech.com

#### Transfer valves, inserts & doors **L-MOTION**

#### For semiconductor production systems

#### Valve Series 04.3 **Insert Series 05.3**

for load lock and process chamber isolation

- Virtually particle-free

- Fast and smooth operation

- Long lifetime of the gate seal

- Service cover for easy gate maintenance

- High purity version

- «Zero» particles on wafer

- Optimized processes to meet ultra clean vacuum requirements

- Highest yield performance from the first wafer

**Door Series 05.3**

for load lock chamber isolation on the atmospheric side

For 200, 300 & 450 mm wafers

#### PacTech doubles capacity in Asia

PACTECH GMBH has announced that subsidiary PacTech Asia (Penang, Malaysia) is now doubling capacity for electroless Ni/Au and Ni/Pd wafer level plating services. The additional clean room area is now ready for installation of a new PacLine 300 automatic electroless plating system.

Manufactured by PacTech, the PacLine 300, pictures above, is suitable for both aluminium and copper pads on 200mm & 300mm wafers, and creates additional capacity of 20,000 to 30,000 wafers per month

Thorsten Teutsch, President and COO of PacTech USA and COO of PacTech Asia comments, "We are experiencing huge success in MOSFET, RFID, LED, MEMS, and other key product areas with both major IDM's and fabless customers. PacTech Asia and PacTech USA work closely together to insure their mutual success! Over 80 percent of the volume demand results from our successful qualifications and product transfers from PacTech USA to PacTech Asia.

Additionally, PacTech Asia continues to invest in more automation, inspection and test capabilities, including wafer back metal services growing to 10,000 wafers per month."

PacTech USA's Silicon Valley facility located in Santa Clara, California is not only PacTech's Equipment Sales and Demonstration Centre for the Americas,

but also provides support on new designs and early production volume demands.

Expedited chip design cycles on first silicon and multi-project wafers are critical to successful design wins with key end customers. Once proven, customers are ready to ramp up production volumes, and rely on their Asia-based external foundry management teams. The "Copy Exact" process transfer from PacTech USA to PacTech Asia intends to insure the seamless transition handover. Heinrich Lüdeke, CEO of PacTech - Packaging Technologies GmbH says, "We continue to commit more investments in 2014 - 2015, supporting both our advanced equipment

manufacturing unit and foundry services operations. Plans include electroplated copper capabilities, embedded die packaging solutions, and next generation high-speed solder jetting machines, as well as laser-assisted bonding equipment."

He concludes, "With over 800 production machines in the field and over 115 patents granted, the combination of PacTech's technologies allows our three locations to provide the widest product offering in the industry; servicing the ASIC, Foundry, Government, Medical, Aerospace, Consumer, Telecommunication, Memory, MEMS, Probe Card, and Hard Disc Drive industries."

#### Plasma-Therm tool enhances NASA's fabrication capability

Plasma-Therm's VERSALINE Deep Silicon Etch system was recently installed at NASA's Jet Propulsion Laboratory (JPL) to expand its silicon deep-etching resources.

The new etching system targets silicon-based applications that include MEMS, sensors, and resonators. JPL's Microdevices Laboratory (MDL) serves users with many different requirements, and the system's mask selectivity, uniformity, vertical profiles, sidewall smoothness, and silicon-on-insulator capabilities will be used to meet their device fabrication needs.

The tool will complement JPL's existing suite of Plasma-Therm equipment, which has been used to make mission-critical components for NASA explorations.

JPL scientists utilised Plasma-Therm systems to help fabricate sensors for the Planck and Hershel missions to map infrared and sub-millimetre cosmic radiation and the spectrometer grating installed on the moon-mapper to detect water.

Tuneable diode lasers to sense methane and other metabolic products from possible past life forms, part of the planetary exploration project involving the Mars Rover, were also made with the assistance of Plasma-Therm technology.

A recent report describes new cosmic microwave background polarization measurements, providing strong confirmation of the Big Bang theory and insight into the first moments of a rapidly expanding universe. The low-noise, superconducting and bolometer-based detectors were fabricated using Plasma-Therm systems that are part of the key process tool set at MDL.

"It is inspiring knowing that Plasma-Therm systems are used not only to develop sensors and optical devices for observing our terrestrial world, but also to contribute to the exploration of our solar system, other galaxies, and the early universe," says David Lishan, Plasma-Therm Principal Scientist and Director, Technical Marketing.

## WET BATCHSPRAY™ TECHNOLOGY

#### **APPLICATIONS:**

IIIII Etch

IIIII Clean

**IIIII** Resist Strip

www.siconnex.com

SICONNEX OFFICES/REPRESENTATIONS:

AUSTRIA (HQ), FRANCE, SINGAPORE, MALAYSIA, AMERICA, RUSSIA

## Instrumental in change

#### Leading plasma process innovation

Oxford Instruments Plasma Technology is turning smart science into world class products with its flexible systems for precise and repeatable etching, deposition and growth of micro and nano structures

Plasma Etch & Deposition

Atomic Layer Deposition

Ion Beam Etch & Deposition

Deep Silicon Etch

For more information, please contact Oxford Instruments Plasma Technology: **Tel:** +44 (0)1934 837 000 **Email:** plasma@oxinst.com

www.oxford-instruments.com/plasma

The Business of Science®

## STMicro automotive accelerometer can make emergency calls

STMICROELECTRONICS says it has added another "world's first" device to its portfolio of motion sensors.

The new device targets automotive telematics, black box, and emergency calling.

The firm claims the new AIS3624DQ, a 3-axis accelerometer with digital output, is the first to provide a full-scale range of ± 24g (acceleration of gravity) while meeting the automotive industry's demanding AEC-Q100 reliability stress

Automotive suppliers are developing an important application to automatically contact emergency services in the event of a collision or vehicle problem. The application can supply potentially life-saving details such as the location of the vehicle and the estimated severity of the problem or accident to emergency service operators. Examples of these services include Onstar (USA), eCall (Europe), and ERA Glonass (Russia).

"In addition to all of the amazing safety innovations already built into today's vehicles, this tiny sensor may play a vital role in protecting the car's

occupants," says Fabio Pasolini, General Manager of the Motion MEMS Division, STMicroelectronics. "ST's long-standing interest in augmenting peoples' lives and our leadership in Micro-Electro-Mechanical Systems (MEMS) have again come together in an important sensor that could potentially help consumers."

The major parameters in estimating the severity of a collision include the decelerations that occurred in all three

dimensions at the moment of impact; for instance, the ERA Glonass specification for the Russian market requires that longitudinal accelerations up to  $\pm$  24g must be measurable with sufficient accuracy. The AIS3624DQ brings all the benefits of ST's stacked-chip technology to the automotive market. STMicroelectronics solution is based on its 8" manufacturing of MEMS products and offers a more competitive solution than the others who produce on 6".

#### DelfMEMS secures \$7.4 million funding

DELFMEMS has secured 5.4M€(\$7.4M) in round C funding for the development of RF MEMS switches. bpifrance Investissement, Iris Capital, Capitalaria, VIVES as well as previous investors (A2D Invest, Finovam, Rhône-Alpes-Création, Eurekap!, Helea Financiere and business angels) have participated to this round C of funding.

The new investment will be used to support the company's growth in the next generation, wireless front-end modules for mobile devices such as smart phones and tablets that need multi-standard, multi-mode mobile telephony.

The move to multiple wireless standards to meet the requirement of always on data access creates the need for high speed RF switching. DelfMEMS technology uses a new, integrated, micro-mechanical building block that is based on a strong, totally new, IP portfolio that includes seven major patents.

The switch is an anchorless and push-pull mechanical device that is deflected by electrostatic forces to switch RF signals based on the principle of current electro-mechanical relays/

switches. It solves past issues and substantially improves insertion loss, linearity, integration, hot switching behaviour, switching time and power consumption to simplify RF architectures. The benefits of DelfMEMS RF MEMS switches are claimed to include improved receiver sensitivity leading to fewer dropped calls and better call quality together with optimal carrier aggregation switching for massively improved data rates.

Combined with high levels of RF integration, this also results in a lower bill of materials cost for the RF Front-End module, and significantly longer battery life by reducing the power consumption of the RF module by up to 20 percent.

Guillaume d'Eyssautier, DelfMEMS CEO, says, "The progress that we have made in turning RF MEMS switches into reality has really impressed our investors. The test silicon has shown that we have cracked the problems that have caused many MEMS companies to fall by the roadside. This is creating a lot of interest in the industry especially as we will have samples for customers to evaluate in a few weeks. This latest round of financing will be used to consolidate the organisation and be ready for production ramp-up by the end of 2014."

## Innovation in materials recovery

Paul Stockman, Technology Manager at The Linde Group explores the complex procedures deployed to sustain a secure and reliable supply of material in the electronics Industry.

THE UNMATCHED TECHNOLOGICAL PROGRESS demonstrated in the semiconductor manufacturing industry has ultimately been made possible through an industry norm of constant technical and engineering innovation.

In this fiercely competitive and diverse market, the constant drive for progress has driven manufacturing complexity. Production of semiconductor devices such as microprocessors and memory is becoming increasingly sophisticated, requiring manufacturers to optimise process performance with increasing levels of resolution and accuracy. For materials suppliers, the portfolio of materials required continues to grow, and as a result, so does the supply chain complexity and quality requirements.

This pressure is exacerbated by a number of factors: a scarcity of key materials, such as the well documented reduction in the supply of helium and complex supply chains. To stay ahead of the curve and reduce operating costs, ensuring a secure and reliable supply of materials is vital.

In fact, it is becoming increasingly important to consider exactly where materials are coming from to ensure consistent quality, stable supply and ultimately the lowest overall cost of ownership. Electronics manufacturing plants are not always located in the optimum position for material supplies, making it vital to think about how materials could potentially be recovered, purified and re-used on site, saving both shipping costs and reducing logistics risks.

#### **Three Recovery Options**

To meet current industry demands we presently operate three main types of materials recovery solutions - tailored to individual customer requirements. Firstly, there is the on-site, closed loop approach where waste materials are recovered and returned into the customer manufacturing process via purification and quality control systems.

This solution can be used for materials such as helium and argon. Another alternative is on-site, open loop recovery. In this case, materials are recovered on-site but then removed and re-used for other applications - for substances like sulphuric acid. The final option is off-site recovery, which is mainly used for high cost materials. Here, the materials are recovered before shipping off-site for recovery and purification, for example, in the case of xenon.

All types of recovery can offer numerous benefits including cost reduction, supply chain security and a lower carbon footprint. Let's now take a look at these three options in more detail, and in relation to helium, sulphuric acid and xenon which are so vital to electronics manufacturing.

#### Helium: Finite resource and specialised recovery

Firstly, let's take Helium which is recovered via the on-site, closed loop approach.

Even though helium is an abundant element in the observable universe, on earth it is a relatively rare and nonrenewable resource, found in the ground and co-located with some natural gas deposits.

In electronics manufacturing, helium is used at hundreds of points in the fab for cooling, plasma processing, and leak detection - however, its recovery is not straightforward. Helium is recovered as part of the natural gas extraction process and is not economically viable to be produced on its own.

To combat this issue, we have been closely involved in the design and manufacture of equipment to

#### MATERIALS INNOVATION

separate, purify, and liquefy helium to a temperature of -269°C. Only in its pure, liquid state can helium be economically transported across the globe. By combining several core technologies, we have created a hybridized plant design to extend helium recovery to electronics applications, where the waste streams are often more dilute and contaminated.

Consequently, groups of large fabs clustered in one major site will be able to receive the real benefits of this helium recovery system, benefitting in terms of cost.

#### Sulphuric acid: Fresh water and logistics

The recovery of Sulphuric acid falls under the second category of materials recovery: on-site, open loop recovery. The drivers for sulphuric acid recovery are very different from that of the previously discussed Helium. The benefits here are reduction of disposal costs and associated demands for fresh water and waste water volumes.

Sulphuric acid is used in electronics manufacturing to remove sacrificial materials, to dissolve stray particles, and to otherwise clean semiconductors. Disposing of the used acid involves first neutralizing and then diluting the waste until it is acceptable for general waste water discharge to local standards.

The Linde Group joint venture, AUECC, is recovering sulphuric acid from the waste material, reducing costs and community waste flows. Using proprietary exchange technology enables the recovery of a high percentage of sulphuric acid from a customer's waste material each time. The material can be purified for re-use in the electronics or other industries.

At the largest semiconductor sites, the logistics of delivering fresh sulphuric acid and removing liquid waste can lead to congestion of delivery vehicles and large storage facilities. Therefore, by moving in acid recovery, the logistics traffic and facilities can be significantly eased. The result: reduced disposal costs, lower environmental impact, lighter traffic.

#### Xenon: Rarity and recovery

Finally, let's turn to Xenon, which is recovered off-site. Xenon is a particularly rare gas, with approximately only one part in 10 million in the atmosphere.

In electronics manufacturing, xenon is used in small amounts in lithography lasers, and in higher amounts and concentrations in etch applications. In fact, sometimes xenon is used as itself in plasma etching, and alternatively as the fluorinated compound XeF,.

Xenon is obtained from large ASUs as a 1:13 crude mixture with krypton and this mixture is then separated, purified, and packaged at one of our global rare gas manufacturing centres. Due to the low starting concentration, only about 10 million litres of Xe are made each year.

So, how does the process work? Xenon is captured in proprietary vessels, shipped back to the global rare gas centres for re-purification. The original customer receives a credit for the xenon recovered at their site.

Recovering xenon in this way can have real tangible results. Ultimately, being able to recover molecules of xenon enables expansion of supply for customers, and stabilises the cost of the material for larger users.

#### Processes for a sustainable future

In a world dependent upon manufacturing processes requiring the use of limited resources, coupled with an ever increasing demand for electronic goods, finding innovative solutions to increase the sustainability of manufacturing is not an easy feat.

The responsibility falls on companies within the manufacturing industries to employ technologies that reduce waste, increase productivity, recycle and purify, and lift the strain on natural resources.

These are now being achieved in ways that contribute towards lower costs, provide flexible logistical solutions, and benefit the environment for a sustainable manufacturing future.

## SEMICON® West2014

July 8–10 Moscone Center San Francisco

From cutting-edge equipment, processes, and materials, to solutions for today's design and manufacturing challenges, SEMICON West connects you to the people, products, and technologies advancing the future of microelectronics.

## Discover Innovation and Ideas Without Limits at SEMICON® West 2014!

- NEW—Semiconductor Technology Symposium (STS)

The STS is a comprehensive technology and business conference addressing the key issues and trends driving the future of semiconductor manufacturing and markets.

- Silicon Innovation Forum (SIF)—The SIF connects innovative, early-stage companies with prospective investors and showcases the next-generation of entrepreneurs in microelectronics.

- PLUS—TechXPOTs, Market Data, Standards, and More!

Access more than 20 hours of FREE technical sessions at the TechXPOTs on the show floor!

Register online through May 9 for your FREE exhibits badge (a \$150 onsite value) www.semiconwest.org

DIRECTED SELF-ASSEMBLY or DSA is an alternative patterning technology which promises to extend conventional lithography beyond its current limits. Traditionally, the semiconductor industry uses optical lithography to pattern structures on a silicon wafer.

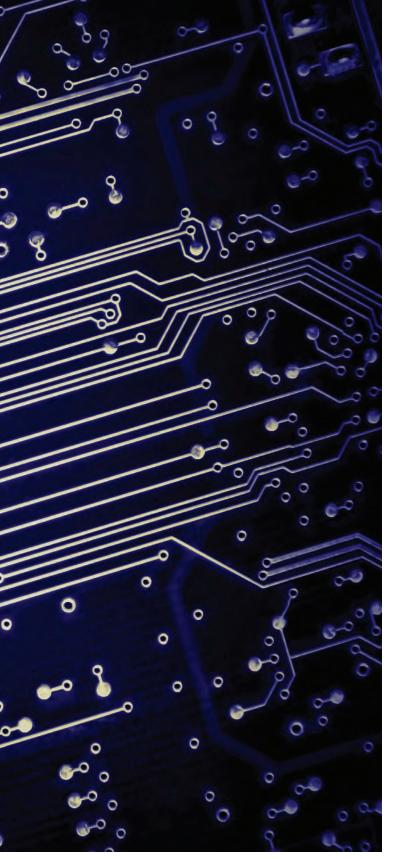

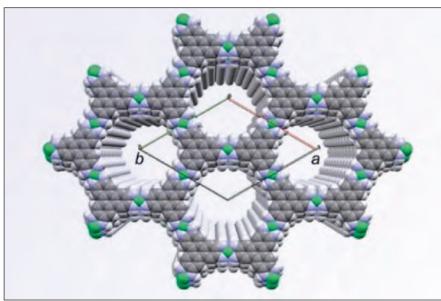

By decreasing the wavelength of light used for exposure and/ or by increasing the numerical aperture of the equipment, the litho community succeeded in printing ever smaller features. In recent years, we saw the introduction of 365nm lithography, 248nm lithography, 193nm lithography, 193nm immersion lithography and finally extreme ultraviolet (EUV, 13.5nm) lithography. Recently there has been a growing interest in using DSA as a means to further reduce the pitch of the final printed structure. The concept of DSA is different from what we are used to. DSA is a bottom up technology that relies on the self-assembly of block copolymers (BCPs). A BCP is a special kind of a copolymer, made up of blocks of different polymerized monomers (A and B). When a thin film of such a BCP is coated on a wafer, a phase separation on the microscopic (or

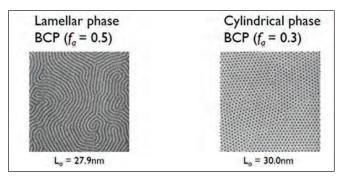

assembling parallel or perpendicular to the substrate) can be influenced by controlling the surface properties of the wafer. To guide the patterns in the desired direction, we make use of pre-patterns. Two different approaches are used for creating these pre-patterns: grapho-epitaxy and chemo-epitaxy. Graphoepitaxy makes use of topographic features (e.g. trenches pre-formed by conventional lithography) to guide the orientation of the BCP microdomains. Chemo-epitaxy employs a surface with a chemically heterogeneous pattern (e.g. hydrophobic and hydrophilic) to align the BCP pattern through surface-polymer interactions. The dimension (for grapho-epitaxy) or periodicity (for chemo-epitaxy) of the pre-pattern should equal an integral time the periodicity of the BCP - a condition which is called commensurability.

#### What are the disadvantages of using DSA compared to optical lithography?

With DSA, pattern parameters such as pitch, critical dimension (or CD, i.e., the dimension of the smallest feature which can be formed) and uniformity are no longer dependent on the lithographic tool conditions, but on the polymer material itself. This holds both an advantage and a disadvantage. A major advantage is the superior uniformity that can be achieved. And, by choosing the right polymer, a phenomenally small resolution can be reached. In academia 6nm pitch (or 3nm half pitch) has already been demonstrated.

But the dependence of pattern parameters on the material properties also holds a disadvantage. Once you have your BCP, you cannot adjust the dimensions of your structures. If your supplier gives you a BCP with slightly different properties, you have to close down the whole process. This will impose new requirements to the way quality control is carried out at the material supplier. Therefore, a close collaboration with our suppliers is extremely important.

#### Will DSA ever replace conventional lithography?

In my opinion, DSA will never be a competitor to advanced optical lithography, EUV lithography or e-beam lithography: they will be complementary. True, DSA will be the champion when it comes to resolution. And it will be very suitable for making large

more precisely: nanoscopic) level occurs between the two components. This results in different morphologies, depending on the volume fraction of components A and B. For patterning, two morphologies are of interest: lamellae (volume fraction 50/50) and cylinders of the minority block in a matrix of the majority block (30/70).

To be useful for making electronic circuits, these structures must be oriented and put in a location where we want them: directed self-assembly. The orientation of the structures (e.g.,

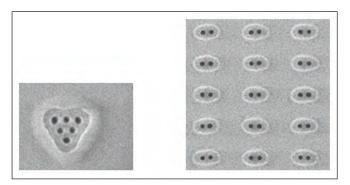

Fig 1: Examples of BCP structures: lamellar phase and cylindrical phase.

#### CHIP MANUFACTURING

Fig 2: Schematic of grapho-epitaxy for pre-pattern generation.

regular patterns. But generating random patterns will be more difficult. This is more easily done with conventional lithography and EUV. In chip manufacturing, we will need both regular and random patterns. Also, the availability of EUV for generating pre-patterns would be very advantageous to DSA; and DSA would help to push the resolution of EUV even further, or could improve its uniformity. So, if the technology becomes mature for chip manufacturing, we will use DSA in combination with projection lithography.

#### What are the challenges to implement DSA in a chip manufacturing process?

I see two major challenges. First, there is the design aspect: how to design a chip that will be patterned by using DSA? It will need appropriate software. This work is currently in progress and is not expected to cause any major problems. We know how to do it. Secondly, for widespread DSA implementation, lower defect levels of DSA structures are required.

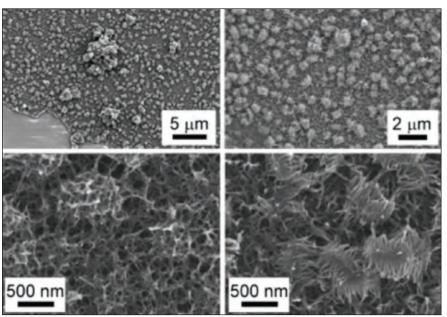

For chip manufacturing, very few errors are allowed on a wafer. For DSA, this translates into a defectivity level that is about two orders of magnitude lower than what we have today. Therefore, we need the right metrology to measure 3D structures in a BCP

Fig 3: The SEM images demonstrate how different arrangements of hole patterns may be achieved.

and to quantify defects over a relative large distance (order of centimetres). Also, we need a dedicated defect reduction strategy. Although there is still a lot of work to do, we are making significant progress. Every six months, we have consistently reached about a tenfold reduction in defectivity.

Fortunately, the introduction of the polymer material itself does not pose any contamination issues. Polymers have been used in chip manufacturing since the very beginning. The most widely studied BCP material for DSA, poly(styrene-block-methyl methacrylate) (PS-PMMA), is comprised of monomers that are similar to the backbone material for chemically amplified resists.

#### When can we expect the first application of DSA?

Ongoing developments are progressing at a rapid rate. At imec, we are working towards including DSA into the 7nm logic technology node. Last year at the SPIE Advanced Lithography Symposium, we demonstrated the first electrical functional via chains made with DSA. In this work, we used blended polymer systems to shrink pre-patterned contact holes.

Contact holes are among the most difficult structures to resolve through traditional lithographic means. With our approach, we were able to shrink from ~53nm post-lithography CD to ~20nm holes after transfer into siliconoxide..

This year at SPIE Advanced Lithography, we reported progress on DSA material and process optimization, defect mitigation, defect metrology and inspection, and design decomposition. We also presented a 7nm compatible fin patterning technology using DSA. The fin layer of an invertor test cell based on a 4 fin, 3 gate test cell was patterned successfully.

The DSA community is working hard to prepare DSA for preproduction. Without further roadblocks, this can be expected by the end of this year or at the beginning of 2015. The first application will most probably be the patterning of contact holes by shrinking prepatterns. This is the most simple application for which we don't need a whole new design approach.

#### What is imec's contribution to the DSA developments?

Certainly our work on defectivity is one of our strengths. We started working on DSA four years ago, after it was claimed that DSA was ready to move from lab to fab. The potential of DSA has been studied for a long time in the academic world and defectivity has always been unknown. Universities do not always have the right metrology to gather defect information over larger areas, which is needed for chip manufacturing.

So we needed to make the processes that have been developed in universities compatible with a manufacturing environment. At imec, we have specialized equipment to study defectivity, and we set up a dedicated process.

Another of our strengths is the ability to combine DSA with immersion lithography and EUV. With this unique toolset, we can make rapid progress in DSA development.

At this moment, we have a team of 15 researchers who work on DSA, several of them are students. And we have a unique partnership with the group of Prof. Paul Nealey from the University of Chicago. From the beginning, we had a very close collaboration and they helped us to speed up our DSA developments. We also closely collaborate with other partners, like AZ Electronic Materials, Tokyo Electron, and KLA-Tencor.

> © 2014 Angel Business Communications. Permission required.

|                    | Pst-Litho | Pst-Hardbake | Pst-DSA<br>+ Wet Dev |

|--------------------|-----------|--------------|----------------------|