## SILICON SEMICONDUCTOR

Connecting the Silicon Semiconductor Community

Volume 37 Issue 1 2015

www.siliconsemiconductor.net

#### Memory Roadmap

#### Foldable displays

## Nanoparticle silver ink

#### **Growth forecast**

#### Lab productivity

## Nanoparticle silver ink

Genes'Ink and KELENN Technology improve manufacturing process

## **GEMINI®FB XT**

BREAKTHROUGH FUSION WAFER BONDING SYSTEM

- 3X Improvement in Wafer-to-Wafer Bond Alignment Accuracy

- XT Frame Platform for up to 50% Throughput Increase

- Enabling High-Volume Production of 3D Devices such as Stacked DRAM, Memory-on-Logic and Future CMOS Image Sensors

## executiveview

by Bertrand Loy, CEO, Entegris, Inc

## Acquisition brings broader solutions for solving difficult challenges in semiconductor and electronics manufacturing

LAST YEAR, Entegris, Inc. completed its acquisition of ATMI, Inc., bringing together two industry-leading companies with complementary technologies; Entegris is a provider of a wide range of products for purifying, protecting and transporting critical materials used in processing and manufacturing in semiconductor and other high-tech industries, while ATMI develops and manufactures advanced materials and materials protection/delivery systems for semiconductor manufacturing. This marriage of materials expertise and handling/filtration technologies is unique to the industry and was driven by the need for innovative and integrated solutions that can solve a new wave of yield issues.

Process control and purity requirements are becoming more critical as manufacturers continue to develop increasingly complex processes to produce next-generation technologies. This applies to a variety of markets, including compound semiconductor, data storage, PV/solar and life sciences.

Solving these technical challenges is requiring new, more holistic innovations in materials science and an ability to translate these discoveries more quickly than ever before into real-world solutions.

With its increased scale and unique combination of technologies, Entegris is now well-suited to address these

challenges. As a larger business, it can sustain investments in both fundamental materials science and new products and chemistries. This is evidenced by the opening this year of the i2M (Ideas to Market) Center for Advanced Materials Science in Bedford, MA. This \$55 million facility is dedicated to researching, developing and manufacturing the world's most advanced filtration membranes and coatings technologies. Yet, technology innovation is only one piece of the puzzle.

The pressure of time-to-yield and the costs of downtime are leading the world's prominent manufacturers to demand more specialized technical applications support on a local level. As a combined entity, the new Entegris is continuing to invest to support its customers.

For example, Entegris has new and ongoing investments in Asia, specifically in Taiwan and Korea, for additional analytical services, product and materials development and manufacturing capabilities.

For suppliers like Entegris, investing in added capabilities is a strategic priority. Solving the next generation of yield challenges will not be easy, but now, as one of the industry's largest providers of yield-enhancing process solutions, Entegris is excited to meet these challenges and to continue making meaningful contributions to the industry.

Publishing Editor Jackie Cannon Senior Sales Executive Robin Halder Sales Manager Shehzad Munshi USA Representatives Tom Brun Brun Media Janice Jenkins

Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor Circulation Director Jan Smoothy Chief Operating Officer Stephen Whitehurst

+44 (0)1923 690205 jackie.cannon@angelbc.com robin.halder@angelbc.com +44 (0)2476 718109 shehzad.munshi@angelbc.com +44 (0)1923 690215 E: tbrun@brunmedia.com +001 724 539-2404 E: jjenkins@brunmedia.com +001 724-929-3550 +44 (0)1923 690200 sharon.cowley@angelbc.com +44 (0)1923 690214 mitch.gaynor@angelbc.com +44 (0)1923 690200 jan.smoothy@angelbc.com stephen.whitehurst@angelbc.com +44 (0)2476 718970

Directors Bill Dunlop Uprichard - CEO, Stephen Whitehurst - COO, Jan Smoothy - CFO, Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal, Jason Holloway

Published by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Herts WD17 1JA, UK, T; +44 (0)1923 690200 F; +44 (0)1923 690201 E; ask@angelbc.com

Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com

Silicon Semiconductor is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/€158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2015. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor (ISSN 1096-598X) is published four times a year for a subscription of \$198 by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Herts WD17 1JA, UK. Periodicals postage paid at Rahway, NJ. POSTMASTER: send address changes to: Silicon Semiconductor, c/o Mercury International Ltd, 365 Blair Road, Avenel, NJ 07001. Printed by: Pensord Press. © Copyright 2015. ISSN 2050-7798 (Print) ISSN 2050-77801 (Online).

### features

#### 14 Nanoparticle silver ink to improve manufacturing

Genes'Ink and KELENN Technology spoke to Mark Andrews and explained how their system can improve printed electronics manufacturing.

#### 28 The memory roadmap: a paradigm shift from 2D to 3D

For a long time, experts have predicted that emerging memories, such as STT-MRAM, resistive RAM and phase-change memory, all resistance based, would replace the common DRAM and Flash technologies in the Terabit era.

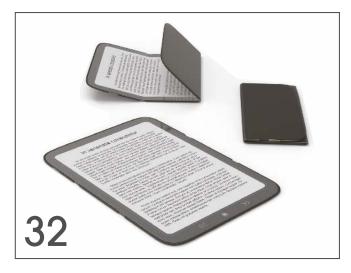

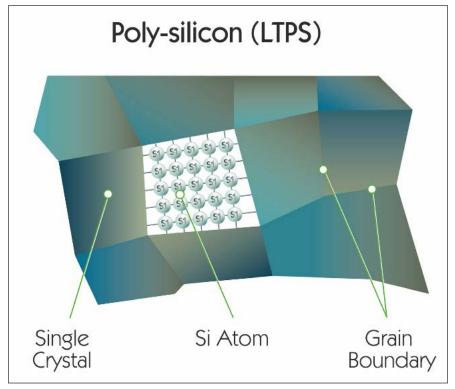

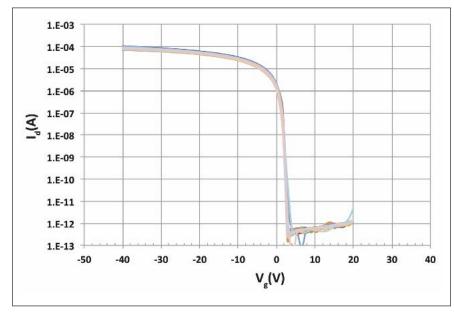

#### 32 Beyond the curve to foldable displays

Over the past couple of years interest in flexible displays that meet these needs has increased significantly, with the market for this flexible display technology predicted to expand to more than \$21billion by 2020.

#### 36 Industry overview

Indicators continue to point towards a robust 2015. Updated 2014 tallies show global Fab spending jumped nearly 20 percent. Forecasters predict semiconductor surges of nearly 10 percent this year.

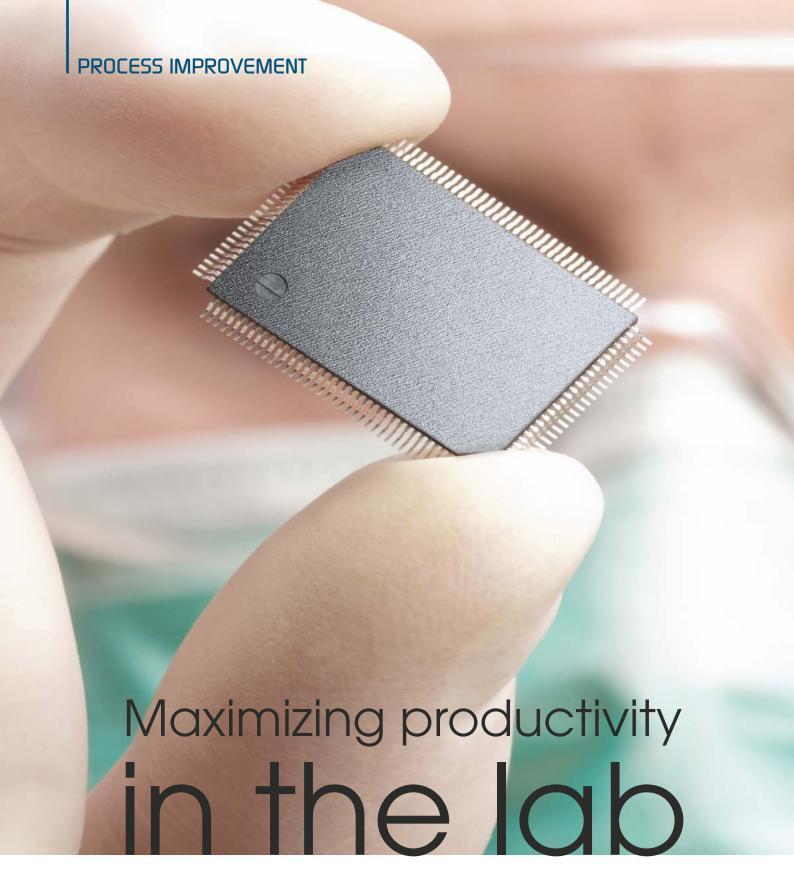

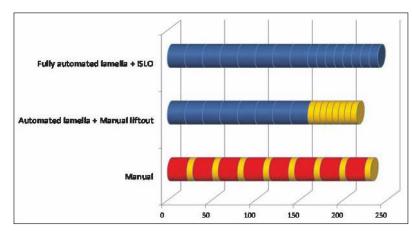

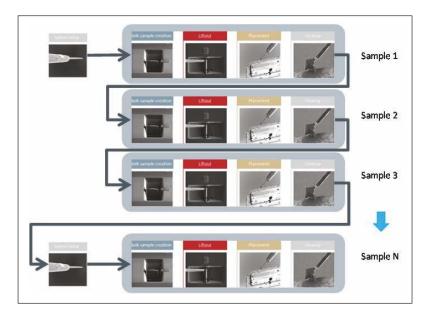

#### 42 Maximising productivity in the lab

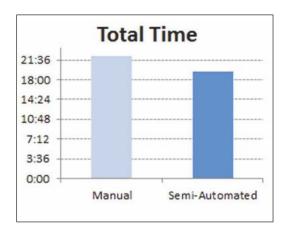

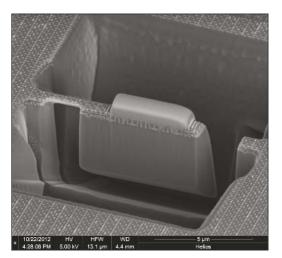

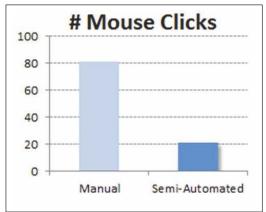

Failure analysis labs typically involve lots of manual tasks performed by highly skilled operators. However, failure analysis labs are now adopting practices from the fab, such as increased automation. The FEI Company present some of the practices and efficiencies that can be gained through automation in the modernised lab.

#### news

- 06 NXP and Freescale announce \$40 billion merger

- 07 Globalfoundries joins imec to develop RF solutions for IOT applications

- 08 Gartner predicts a 5.4 percent increase in sales in 2015

- 10 Strong fab equipment spending expected in 2015

- 11 Global semiconductor industry posts record sales

- 12 Cool silicon sets international standards

- 13 Tronics seize submicron MEMS opportunities

#### industry research

- 18 A new step using graphene in electronic applications

- 20 Breakthrough promises secure communications and faster computers

- 22 New solder for semiconductors creates technological possibilities

- 24 Laser-induced graphene 'super' for electronics

- 26 Patented process builds better semiconductors, improve electronic devices

#### **NEWS REVIEW**

## NXP and Freescale in \$40 billion merger

NXP SEMICONDUCTORS N.V. and Freescale Semiconductor, Ltd have entered into a definitive agreement under which NXP will merge with Freescale in a transaction which values the combined enterprise at just over \$40 billion. The merger creates a high performance mixed signal semiconductor industry leader, with combined revenue of greater than \$10 billion. The merged entity will become the market leader in automotive semiconductor solutions and the market leader in general purpose microcontroller (MCU) products. The combined company will capitalize on the growing opportunities created by the accelerating demand for security, connectivity and processing.

"Today's announcement is a transformative step in our objective to become the industry leader in high performance mixed signal solutions. The combination of NXP and Freescale creates an industry powerhouse focused on the high growth opportunities in the Smarter World. We fully expect to continue to significantly out-grow the overall market, drive world-class profitability and generate even more cash, which taken together will maximize value for both Freescale and NXP shareholders," said Richard Clemmer, NXP Chief Executive Officer. Mr. Clemmer will continue to be the President and Chief Executive Officer of the merged company.

"We believe this merger, which combines two highly successful and complementary companies, will create significant value for Freescale's and NXP's shareholders, customers and employees. Both companies have built leadership positions and have a sharp focus on delivering superior value to customers. Our combined scale, size and global reach will position our new company to deliver sustainable above market growth. It will also serve to accelerate the strategic plans both companies have invested in, enabling us to deliver more complete solutions to customers," said Gregg Lowe, Freescale Semiconductor President and Chief Executive Officer.

The transaction is expected to be

accretive to NXP non-GAAP earnings and non-GAAP free cash flow. NXP anticipates achieving cost savings of \$200 million in the first full year after closing the transaction, with a clear path to \$500 million of annual cost synergies. Under the terms of the agreement, Freescale shareholders will receive \$6.25 in cash and 0.3521 of an NXP ordinary share for each Freescale common share held at the close of the transaction. The purchase price implies a total equity value for Freescale of approximately \$11.8 billion (based on NXP's closing stock price as of February 27, 2015) and a total enterprise value of approximately \$16.7 billion including Freescale's net debt.

The transaction is expected to close in the second half of calendar 2015. NXP intends to fund the transaction with \$1.0 billion of cash from its balance sheet, \$1.0 billion of new debt and approximately 115 million NXP ordinary shares. Post transaction, Freescale shareholders will own approximately 32 percent of the combined company.

Dale Ford, VP of IHS Technology commented "From a buy side perspective this definitely has important implications. When Renesas and NEC merged, many companies were left looking for another second source supplier, and they turned to Freescale and NXP. Now with the merger of these two companies there are pluses and minuses - first - the combined company should have greater resources to devote to support the significant pick-up of customers they took from Renesas / NEC when they went looking for another second source. But, second, the industry consolidation just became that much greater meaning there are fewer viable alternatives of major suppliers for vendors to choose from.

The new company will become the 7th largest semiconductor supplier overall based on preliminary market share data for 2014. Both companies started to outperform the overall market in the past 2 years prior to the merger announcement (2013 to 2014). Before that growth for each company was below overall market growth since 2008."

#### Lattice Semiconductor closes acquisition of Silicon Image

LATTICE SEMICONDUCTOR CORPORATION, a provider of programmable connectivity solutions, has announced the close of its acquisition of Silicon Image, Inc., a leading provider of wired and wireless connectivity solutions, and the results of the related tender offer.

For the first time in the semiconductor industry, a single company now combines the design flexibility and time to market benefits of FPGAs, with the highly integrated, function and cost optimization benefits of ASSPs. The all-cash acquisition, valued at approximately \$606.6 million (or approximately \$466.6 million on an enterprise value basis), is expected to be immediately accretive to EPS on a non-GAAP basis.

Darin G. Billerbeck, Lattice Semiconductor's President and Chief Executive Officer, said, "Today marks an exciting day for Lattice, as we close our transformative acquisition of Silicon Image. We have significantly expanded our Company's capabilities, with the addition of MHL, HDMI and 60 GHz Intellectual Property, enhanced our business prospects and financial profile, and further diversified our global customer base. We will move forward quickly in order to realize the compelling revenue and operating synergies created by our increased economies of scale.

Our team has put in place a well thought through, comprehensive consolidation plan for an efficient integration and the achievement of our targeted cost synergies. We plan to work relentlessly over the coming years to rapidly deleverage through our increased free cash flow, and to achieve the full benefits of this major acquisition for our customers, shareholders and employees."

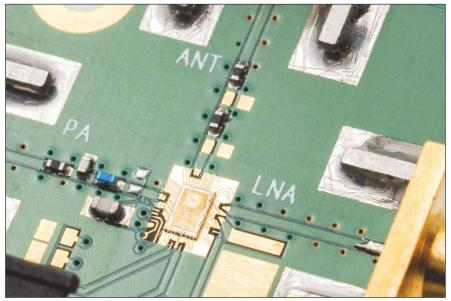

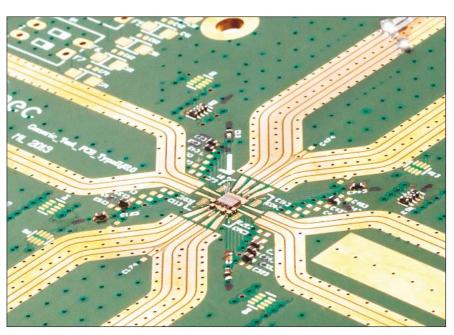

## Globalfoundries joins imec to develop RF Solutions for IOT applications

GLOBALFOUNDRIES, a provider of advanced semiconductor manufacturing technology has announced a partnership with imec, a leading nanoelectronics research center, for joint research on future radio architectures and designs for highly integrated mobile devices and IoT applications.

A key challenge for next-generation mobile devices is controlling the cost and footprint of the radio and antenna interface circuitry, which contain all of the components that process a cellular signal across the various supported frequency bands. Today, a typical mobile device must support up to 28 bands for worldwide 2G, 3G, 4G, LTE network connectivity, and more complex carrier aggregation schemes and additional frequency bands are expected for future generations.

These challenges are driving the need

for an agile radio that integrates many of the separate components into one piece of silicon, including power amplifiers, antenna switches, and tuners and provides a solution which is both flexible and low cost.

Globalfoundries will closely collaborate with technical experts from imec to investigate low-power and compact high-performance agile radio solutions that will enable a broad range of radio architecture design--targeting improvements in area, performance and power consumption. Globalfoundries will also partner with imec to develop innovative ultra-low power IC design solutions leveraging Globalfoundries' CMOS technology to address the demanding requirements of tomorrow's IoT devices. Ultimately, the partnership aims to build a technology and design infrastructure that will enable future RF architectures while minimizing critical

interface requirements for radio power consumption and performance.

"This collaboration expands our relationship with imec, and we're eager to leverage their R&D expertise in RF technology to accelerate time-to-volume of designs and deliver leading-edge RF technology to our customers," said Peter Rabbeni, director RF Segment Marketing at Globalfoundries . "This relationship further reflects our commitment to find RF design implementations that will efficiently extend the range of wireless communication applications without increasing the form factor or cost."

"There are advanced chip technology challenges the industry needs to address to enable a higher level of integration and lower power consumption for future wireless communication," said Harmke de Groot, senior director Perceptive Systems for the Internet of Things.

Samsung introduces 128-Gigabyte universal flash storage, for smartphones

SAMSUNG ELECTRONICS CO., LTD., a pioneer in advanced memory technology, has announced it is mass producing the industry's first 128-gigabyte (GB) ultra-fast embedded memory based on the much-anticipated Universal Flash Storage (UFS) 2.0 standard for nextgeneration flagship smartphones. The new embedded memory's UFS 2.0 interface is the most advanced JEDEC-compliant, next-generation flash memory storage specification in the world.

"With our mass production of ultra-fast UFS memory of the industry's highest capacity, we are making a significant contribution to enable a more advanced mobile experience for consumers," said Jee-ho Baek, Senior Vice President of Memory Marketing, Samsung Electronics.

"In the future, we will increase the proportion of high-capacity memory solutions, in leading the continued growth of the premium memory market." UFS memory utilizes "Command Queue," a technology that accelerates the speed of command execution in SSDs through a serial interface. significantly increasing data processing speeds compared to the 8-bit parallel-interface-

based eMMC standard.

As a result, Samsung UFS memory conducts 19,000 input/output operations per second (IOPS) for random reading, which is 2.7 times faster than the most common embedded memory for highend smartphones today, the eMMC 5.0. It also delivers a sequential read and write performance boost up to SSD levels, in addition to a 50 percent decrease in energy consumption. In addition, the random read speed is12 times faster than that of a typical high-speed memory card

(which runs at 1,500 IOPS), and is expected to greatly improve system performance.

In the future, Samsung anticipates that UFS will support high-end mobile market needs, while eMMC solutions remain viable for the mid-market, value segments.

For random writing of data to storage, the blazingly fast UFS embedded memory operates at 14,000 IOPS and is 28 times as fast as a conventional external memory card, making it capable of supporting seamless Ultra HD video playback and smooth multitasking functions at the same time, enabling a much improved mobile experience. Samsung's new UFS embedded memory comes in 128GB, 64GB and 32GB versions, which are twice the capacity of its eMMC line-up, making it today's optimal memory storage solution for high-end mobile devices.

#### **NEWS REVIEW**

## Gartner predicts 5.4 percent increase in 2015

WORLDWIDE semiconductor revenue is forecast to reach \$358 billion in 2015, a 5.4 percent increase from 2014, but down from the previous quarter's forecast of 5.8 percent growth, according to Gartner Inc. The market is being driven by strong growth in applicationspecific standard products (ASSPs) in smartphones, along with DRAM and NAND flash in ultramobiles and solidstate drives (SSDs).

"Semiconductor revenue growth in 2015 is expected to slow from the 7.9 percent growth experienced in 2014 as DRAM returns to more traditional price reductions and the industry burns off excess holiday inventory,' said Jon Erensen, research director of Gartner. "DRAM pricing was unusually firm in 2014 due to short supply, which propelled DRAM to be the fastestgrowing device type in 2014 with 31.7 percent revenue growth.

DRAM supply and demand will be in line in 2015, driving bit pricing down a more traditional 16.8 percent and reducing annual DRAM revenue growth to 7.7 percent."

From an application point of view, smartphones, SSDs and ultramobiles will see the largest dollar increases. In 2015, compute applications will continue to be the largest market for semiconductors, followed by wireless and consumer applications. Combined, these three device categories represent more than two-thirds of total semiconductor revenue and have the most influence on the overall strength of the semiconductor market.

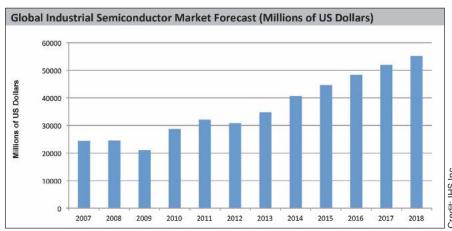

However, in 2015, the industrial electronics segment is expected to outperform overall semiconductor market growth and other electronic application categories with revenue growth of 9.1 percent. The growth will be driven mainly by LED lighting applications for industrial and residential purposes and smart city projects. In addition, the Internet of Things (IoT) will continue to drive very strong unit growth in 2015 and beyond.

Following industrial applications, wireless applications — driven mainly by mobile phones — will be the next biggest growth market for semiconductors in

2015. However, the 2015 revenue growth forecast for wireless applications, and specifically mobile phones, remains the same as the previous quarter's forecast.

"While mobile phone semiconductor sales will remain robust, driven by the accelerating shift to smartphones and 4G Long Term Evolution, there is concern that weak sell-through for other electronic equipment categories will result in higher inventory levels and drag down semiconductor sales in the first quarter of 2015," Erensen said.

#### Ghent University, imec and collaborators extend the spectrum of frequency comb light sources

SCIENTISTS from Ghent University and imec have joined forces with the Max Planck Institute in Garching to realise a frequency comb light source in the mid-IR wavelength band. These frequency comb light sources with an extended spectrum can be used for real-time, extremely high resolution spectroscopy, e.g. to measure the presence and concentration of gas molecules in analytes.

A frequency comb source is a light source with a spectrum containing thousands of laser lines. The development of these sources has been revolutionary for fundamental science. It has allowed the construction of a link between the optical part of the electromagnetic spectrum and the radio frequency part. As such, it has allowed researchers to determine optical frequencies with an unprecedented

precision. Amongst others, frequency comb light sources have been used in optical clocks enabling precise time keeping. The enormous impact of frequency comb light sources on science was highlighted in 2005, when the Nobel Prize for physics was awarded to Prof. T. Haensch and Prof J. Hall for their work on optical frequency metrology using frequency combs.

Lately, frequency combs have been used to target more real life applications. In several experiments, it has been shown that the specific properties of the sources can be used to do fast, high-resolution spectroscopy over a broad spectrum. However, traditional comb sources are not at the right wavelength spectrum for doing spectroscopy.

Ghent University, imec, the Max Planck Institute for Quantum Optics in Garching and the Auckland University in New Zealand have developed mid-infrared frequency combs, working in the midinfrared molecular fingerprinting region of the electromagnetic spectrum. In this wavelength region, many molecules have specific absorption bands that can be used in spectroscopy to determine the presence and concentration of these molecules in samples.

The researchers successfully realized the broad frequency combs, by combining the strong light-matter interaction in silicon with its broad transparency window. By fabricating so-called nanowire silicon photonics waveguides to confine the light in a very small area waveguide, they further enhanced the strong light-matter interaction allowing them to broaden the spectrum of the frequency combs into the mid-infrared.

# Optimize the Thermal Performance of your Process Equipment.

Extensive computational tools enable product designs to be highly refined for ultimate performance.

Multi-zone circuit layouts in a polyimide construction are highly customized to deliver exacting performance up to 250°C.

EZ-ZONE® RM Multiloop controllers are fully scalable with up to 152 PID Loops and 256 monitor points per system. Atlow provides innovative solutions to help process tool manufacturers meet the needs of the semiconductor technology roadmap. Our approach is to work collaboratively to help solve complex thermal challenges associated with state-of-theart manufacturing processes; helping to improve yield, throughput and cost of ownership. This includes innovative heaters, controllers and sensors for use in front-end and back-end applications such as CVD, PECVD, Etch, Diffusion, Bonding, IC test and more.

ASSURANT™ gas and pump line heaters feature high temperature capabilities with low outgassing.

Contact Watlow® today for the latest thermal solutions for semiconductor applications.

European Technical Sales Offices

**Germany** +49 (0) 7253-9400-0

info@watlow.de

France +33 1 41 32 79 70 info@watlow.fr

Italy

+39 02 4588841 italyinfo@watlow.com

Spain

+34 91 675 1292 info@watlow.es

UK

+44 (0) 115-964-0777 info@watlow.co.uk

#### **NEWS REVIEW**

## Strong fab equipment spending expected in 2015

SEMI has announced an update of the SEMI World Fab Forecast report which updates outlooks for 2015 and 2016. The SEMI report reveals that fab equipment spending in 2014 increased almost 20 percent and will rise 15 percent in 2015, increasing only 2-4 percent in 2016. Since November 2014, SEMI has made 270 updates on its World Fab Forecast report, which tracks fab spending for construction and equipment, as well as capacity changes, and technology nodes transitions and product type changes by fab.

The SEMI World Fab Forecast and its related Fab Database reports track any equipment needed to ramp fabs, upgrade technology nodes, and expand or change wafer size, including new equipment, used equipment, or in-house equipment and spending on facilities for installation.

Fab spending, such as construction spending and equipment spending, are fractions of a company's total capital expenditure (capex). Typically, if capex shows a trend to increase, fab spending will follow. Capex for most of the large semiconductor companies is expected to increase by 8 percent in 2015, and grow another 3 percent in 2016.

These increases are driven by new fab construction projects and also ramp of new technology nodes. Spending on construction projects, which typically represents new cleanroom projects, will experience a significant -32 percent decline in 2015, but is expected to rebound by 32 percent in 2016.

Comparing regions across the world, according to SEMI, the highest fab equipment spending in 2015 will occur in Taiwan, with US\$ 11.9 billion, followed by Korea with US\$ 9 billion.

The region with third largest spending, the Americas, is forecast to spend about US\$ 7 billion. Yet growth will decline in

the Americas, by 12 percent in 2015, and decline by 12 percent in 2016 again.

Fourth in spending is China, with US\$ 4.7 billion in 2015 and US\$ 4.2 billion in 2016. In other regions, Japan's spending will grow by about 6 percent in 2015, to US\$ 4 billion; and 2 percent in 2016, to US\$ 4.2 billion. The Europe/ Mideast region will see growth of about 20 percent (US\$ 2.7 billion) in 2015 and over 30 percent (US\$ 3.5 billion) in 2016. South East Asia is expected to grow by about 15 percent (US\$ 1.3 billion) in 2015 and 70 percent (US\$ 2.2 billion) in

2015 is expected to be the second consecutive year in equipment spending growth. SEMI's positive outlook for the year is based on spending trends tracked as part of our fab investment research. The "bottom's up" company-by-company and fab-by-fab approach points to strong investments by foundries and memory companies driving this year's growth.

## Global semiconductor industry posts record sales

THE Semiconductor Industry Association (SIA), has announced that the global semiconductor industry posted record sales totalling \$335.8 billion in 2014, an increase of 9.9 percent from the 2013 total of \$305.6 billion. Global sales for the month of December 2014 reached \$29.1 billion, marking the strongest December on record, while December 2014 sales in the Americas increased 16 percent compared to December 2013. Fourth quarter global sales of \$87.4 billion were 9.3 percent higher than the total of \$79.9 billion from the fourth quarter of 2013.

Total sales for the year exceeded projections from the World Semiconductor Trade Statistics (WSTS) organization's industry forecast. All monthly sales numbers are compiled by WSTS and represent a three-month moving average.

"The global semiconductor industry posted its highest-ever sales in 2014, topping \$335 billion for the first time thanks to broad and sustained growth across nearly all regions and product categories," said John Neuffer, president and CEO, Semiconductor Industry Association. "The industry now has achieved record sales in two consecutive years and is well-positioned for continued growth in 2015 and beyond."

Several semiconductor product segments stood out in 2014. Logic was

the largest semiconductor category by sales, reaching \$91.6 billion in 2014, a 6.6 percent increase compared to 2013. Memory (\$79.2 billion) and micro-ICs (\$62.1 billion) - a category that includes microprocessors - rounded out the top three segments in terms of sales revenue. Memory was the fastest growing segment, increasing 18.2 percent in 2014. Within memory, DRAM performed particularly well, increasing by 34.7 percent year-over-year. Other fast-growing product segments included power transistors, which reached \$11.9 billion in sales for a 16.1 percent annual increase, discretes (\$20.2 billion/10.8 percent increase), and analog (\$44.4 billion/10.6 percent increase).

Annual sales increased in all four regional markets for the first time since 2010. The Americas market showed particular strength, with sales increasing by 12.7 percent in 2014. Sales were also up in Asia Pacific (11.4 percent), Europe (7.4 percent), and Japan (0.1 percent), marking the first time annual sales in Japan increased since 2010.

"The U.S. market demonstrated particular strength in 2014, posting double-digit growth to lead all regions," continued Neuffer. "With the new Congress now underway, we urge policymakers to help foster continued growth by enacting policies that promote U.S. innovation and global competitiveness."

#### SBA 458 Nemesis

New Seebeck instrument to measure thermoelectric materials

New SBA 458 Seebeck Coefficient Analyzer Find out more: www.netzsch.com/n23122

#### The benefits of a clever measurement setup

- A Measurement Setup for Varied Sample Geometries

- Quick Start to Measurements Convenient Sample Change

- Integrated Quality Check Outstanding Two-Heater System

- Highly Reliable & Rugged Design Avoiding Diffusion Problems

- No Distance Determination Required

NETZSCH-Gerätebau GmbH Wittelsbacherstraße 42 95100 Selb Germany

#### **NEWS REVIEW**

## Cool silicon sets international standards

RESEARCH RESULTS from a collaborative project between NaMLab (TU Dresden), the Fraunhofer Institute for Photonic Micro Systems (IPMS) and GLOBALFOUNDRIES are being included in the current version of 'The International Technology Roadmap for Semiconductors', the technical guide for the semiconductor branch.

The development project was achieved at 'Cool Memory', a sub-project of Cool Silicon, the leading edge cluster for energy efficient micro-andnanoelectronics funded by the Federal Ministry for Education and Research. Based on doped Hafniumoxide, the team has developed a cost-effective, energyefficient ferroelectric non-volatile memory chip that requires low write voltage, can be produced at small structural width and whose production can easily be integrated in common semiconductor manufacturing processes.

Dr. Thomas Mikolajiick, Professor for Nanoelectronic Materials and Director of the NaMLab at TU Dresden, as well as the coordinator for Cool Silicon says the project's inclusion in the International Technology Roadmap is a confirmation of the success of the team's innovative

"For an innovation made in Dresden to become part of the International Technology Roadmap guidelines, is certainly not commonplace," Dr. Mikolajiick says. "We are very proud of this accomplishment because the roadmap is followed closely by members of the international semiconductor industry."

The new technology is a result of the Cool Silicon sub-project called 'Cool Memory', developed by participating partners searching for innovative ways to manufacture non-volatile memory.

"Typical technologies currently used for non-volatile memory are based on the principle of charge-storage," Mikolajick says. "This has several disadvantages. Writing, for instance, requires high voltage and is very energy intensive. Due to the high voltage, certain circuit parts for controlling memory cannot be

reduced to desired sizes, which renders such memory inefficient for small and medium storage densities."

Therefore, the Dresden scientists rely on a different technology. They store data in ferroelectrics, a material that can be brought into two different polarization states by means of electric charge and switching requires very little energy.

"This is nothing fundamentally new," Mikolajick says. "The approach has been used since the 1950s. Up until now, the problem has been that manufacturing required complicated materials like lead zirconium titanate (PZT).

For chip manufacture, this has posed two challenges: manufacturing requires measures that are very intrusive to typical semiconductor processes; and scaling below 120 nanometers is impossible."

In order to realize the dream of a scalable and cost-effective ferroelectric memory chip, Cool Memory relies on hafnium oxide, a material which is already standard in the 28-nanometer production in the factories of project partner GLOBALFOUNDRIES where it is used as a high-k-material (high-k-dielectric). Using doping, the Dresden scientists were able to turn hafnium oxide ferroelectric and they achieved it using conventional manufacturing processes.

Now, the Saxon Leading Edge Cluster is able to produce non-volatile memory chips that enable more energy efficient writing and require lower voltage than chips currently available. They are also much easier to integrate into CMOS (Complementary Metal-Oxide-Semiconductor) processes than conventional ferroelectrics. (CMOS is a technology for constructing integrated circuits.) Doped hafnium oxide makes manufacturing at very small structural width possible.

"The fact that this innovation is being included into the ITRS shows us how large the interest is especially from the industry," Mikolajick says. "We are delighted that the work of the Leading Edge Cluster Cool Silicon has found such great international resonance."

#### ASE shares get a boost from Apple Watch launch

SHARES of Advanced Semiconductor Engineering Inc. (ASE), the world's largest integrated circuit packaging and testing services provider, jumped after Apple Inc. unveiled its Apple Watch. Because ASE is believed to be the sole IC packaging and testing services supplier for the Apple Watch, many expect the new device to bolster ASE's shipments, especially after the global semiconductor sector climbs out of its first quarter doldrums.

In a news conference held in San Francisco, Apple CEO Tim Cook unveiled the Apple Watch, saying that the Apple Watch is "the most personal device we have ever created."

The gadget is a miniature computer consumers can wear on their wrists, but the product requires an iPhone to be fully functional.

The Apple Watch is scheduled to go on sale on April 24 in select countries, such as the United States, Japan, Hong Kong and China, and Apple will start taking pre-orders online on April 10.

"Many market analysts expect Apple to ship about 20 million Apple Watches in the first year. Shipments could double in the second year. ASE is the sole IC packaging and testing service provider and will no doubt become one of the major beneficiaries," Hsu said.

### Tronics seize submicron MEMS opportunities

Tronics is capitalizing on the growing number of submicronic MEMS devices opportunities to expand its equipment and process base. Tronics has been manufacturing MEMS for 15 years with an emphasis on SOI, WLP.

Over the last 2 years, Tronics acquired advanced equipment and allocated significant resources to the development of submicron MEMS processes, which combine traditional MEMS structures and advanced Nanotechnology parts. There are a growing number of opportunities for submicronic MEMS devices in optical applications, but also in inertial and microfluidics applications.

Tronics acquired a 0.25 i-line stepper to address some of these opportunities. In the world of MEMS, this is high resolution. The stepper allows the patterning of the very small geometries necessary for many applications, such as piezoresistive inertial MEMS based on silicon nano-wires (M&NEMS), or micro mirrors for telecommunication applications. This machine is also needed to manufacture moving structures requiring very tight alignment.

Tronics also acquired equipment for nanoimprint lithography (NIL) This technique allows the creation of structures with superior resolution, as small as 50 nanometers, by embossing a resist with a stamp. This technology is cost effective for patterning large areas, once the processes have been properly developed and validated.

Tronics was one of the first European companies to bring NIL to industrial production, and is now using nanoimprint to define high-density structures on both silicon and glass substrates. With a total investment in excess of 2 million Euros in this field over the last 18 months, Tronics has demonstrated its commitment to the submicronic MEMS business. The new equipment is fully operational at Tronics and is being used for product deliveries to customers.

More than ten thousand wafers have already been processed and delivered. The range of applications requiring such tight alignment or submicronic patterns is broad and growing. Some

examples are submicronic optical gratings, spectrometers, fluidic filters, piezo-resistive inertial sensors based on silicon nano-wires, micromirrors, gas sensors based on resonant silicon nanocantilivers, and there are many others.

Pascal Langlois, CEO of the Tronics group said: "Tronics is committed to further developing the know-how required to address these opportunities, and to expanding its equipment and process portfolio. Tronics will continue to build on its solid MEMS engineering background and its ability to solve difficult MEMS manufacturing challenges, and plans to remain a leader in specialty MEMS processes."

## Nanoparticle silver ink

## to improve manufacturing

Genes'Ink and KELENN Technology spoke to Mark Andrews and explained how their system can improve printed electronics manufacturing.

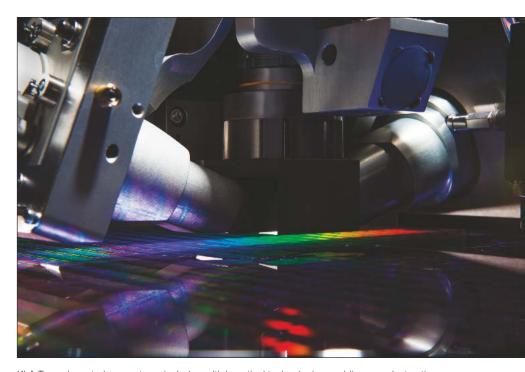

GENES'INK and KELENN Technology recently announced co-development of a new proprietary nanoparticle silver ink for KELENN's new high speed printer, the KSCAN PE300. According to both companies, these new technologies can radically accelerate production and efficiency of printed electronics for RFID antennas, capacitors, OLED active layers and many other applications. We asked Genes'Ink and KELENN Technology to detail how their system can improve printed electronics manufacturing.

Speed appears a central attribute of the new KSCAN PE300, moving at 'several meters per minute' compared to only 'a few centimeters per hour' in existing systems -How do you achieve such a performance leap?

A Such performance is achieved thanks to a combination of innovations and technologies. KELENN Technology and Genes'Ink have worked together to create an industrial digital silver ink that can be used with KELENN Technology's proprietary high speed piezo jetting modules. KELENN Technology has redesigned the architecture, electronics and fluid management to be able to properly handle approximately 30 key parameters, in relation with printed electronics, such as rheology, nozzle clogging and many others.

Has speed been an impediment to more widespread adoption of inkjet printing of electronic circuits in the overall marketplace?

A Yes. Actually 90 percent of printed electronics is handled by screen printing. Companies are focusing on prototyping circuit design and ink formulation with low speed table top inkjet printers. However, the whole work has to be done once again when moving into industrial production scale. For the industry, before the KSCAN PE300 was announced, it was safer to put the emphasis on screen printing for production.

The partnership between Genes' Ink and KELENN Technology seems a natural outgrowth of a conductive ink maker working with a developer of improved electronic circuit printing technology – How do (ink and printer) complement one another to offer a better solution?

A To be able to print at fast speed, the volume of ink per droplets must be reduced compared to traditional methods. This matches perfectly with nanoparticle silver

#### **COVER STORY**

ink, which requires less quantities for a given conductivity compared to traditional silver ink. From a consumable cost point of view, KELENN Technology's printer (uses) less ink for a given conductivity compared to screen printing. So the customer benefits from two major cost areas: improved productivity and reduced consumable costs.

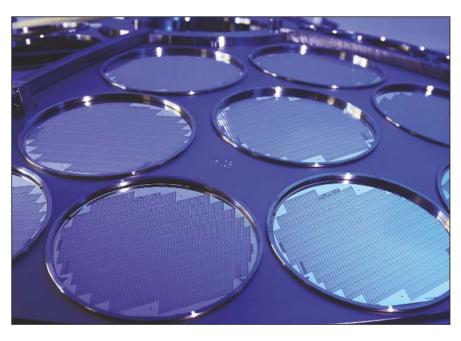

Genes'Ink cites several applications of the new technology - active layers in OLEDs, RFID antennas, production capacitor printing. Can the technology also be used for printing the silver bus bars, lattice fingers or other elements in photovoltaic cells (printing on polysilicon wafers)?

Yes, for example, in a very interesting case study, we have demonstrated that one litre of ink could produce approximately 1 million patterns.

Line accuracy seems another advantage of the new technology – Is this a benefit of the new nanoparticle ink, the printer itself, or both?

A Both technologies bring their advantages. The Nano ink specific formulation can be jetted very precisely. The printer has a native resolution of 1200 dpi with a positioning precision of the print head of up to  $2 \mu m$ . But mostly, the precision is due to a number of innovations in the design of inkjet deposition that are brought to the market by KELENN Technology.

A lnk silver content reduction (50 percent less) in your new system is another clear advantage - Can you elaborate about what enables the new printer and ink to use so much less silver?

${\sf A}$  The (ink) formulation is a key feature. Nanoparticles of silver have the ability to coalescence and show conductivity with a very limited amount of ink and at low

temperature. Reliability of inkjet deposition is a key feature as well; we are looking for a first pass yield of 95 percent. The quantity of ink waste per job has been greatly reduced by KELENN Technology compared to screen printing or other inkjet (systems).

The new technology mentions usage of photonic annealing in a controlled environment with a specialised atmosphere – Is the vacuum system and gas supply control self-contained, or does the manufacturer need to have out-board vacuum and gas delivery/evacuation?

A Yes, the whole technical environment is self-contained to facilitate installation and commissioning. The KSCAN PE300 is fitted with carbon filters for exhaust. In basic configurations, these filters can cope with small to medium productions. For volume production, or a more complex configuration, it is best to add external filters and output.

What have we not covered that is an additional benefit of the new system?

A software package is included with the KSCAN PE300 to manage job productions; it interfaces with standard CAD electronics output vector files such as GERBER and simple image files such as TIFF, BMP and JPG. The KSCAN PE300 can also be fitted with a feeder and a stacker.

Oo you believe the new system (ink + printer) offer decisive advantages?

This system is opening the printed electronics market to industrial printers, not only electronics people. It is easy to use and they already use this kind of system in their plants.

> © 2015 Angel Business Communications. Permission required.

## **SEMICON<sup>®</sup> Southeast Asia** 2015

**APRIL 22-24** SPICE Arena Penang, Malaysia

#### ADVANCING SEMICONDUCTOR DEVELOPMENT THROUGH TECHNOLOGY INNOVATION AND DESIGN

Be a part of the inaugural SEMICON® Southeast Asia in Penang, Malaysia!

- See products and engage technical experts from more than 150 international companies

- Access information and learn about the latest developments and trends shaping the future of semiconductors, including IoT

- *Find solutions* to your critical manufacturing challenges from more than 150 companies and at technical sessions covering:

- Assembly and Packaging Yield Methodologies

- Product and System Test High-brightness LEDs

- Engage technologists, researchers, executives, and *peers*—find new partners, collaborate, and connect to more than 6,000 expected attendees

Register Early for Your Chance to Win Special Lucky Draw Prizes!

**Register Now** and Save on Programs!

Register before March 20 and Save

www.semiconsea.org

Organized by

Official Airline

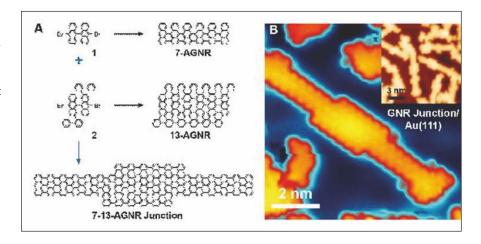

## A new step towards using

## graphene

in electronic applications

A team at the University of Berkeley and the Centre for Materials Physics (CSIC-UPV/EHU) has managed, with atomic precision, to create nanostructures combining graphene ribbons of varying widths

#### INDUSTRY RESEARCH

FEW MATERIALS have received as much attention from the scientific world or have raised so many hopes with a view to their potential deployment in new applications as graphene has. This is largely due to its superlative properties: it is the thinnest material in existence, almost transparent, the strongest, the stiffest and at the same time the most strechable, the best thermal conductor, the one with the highest intrinsic charge carrier mobility, plus many more fascinating features.

Specifically, its electronic properties can vary enormously through its confinement inside nanostructured systems, for example. That is why ribbons or rows of graphene with nanometric widths are emerging as tremendously interesting electronic components. On the other hand, due to the great variability of electronic properties upon minimal changes in the structure of these nanoribbons, exact control on an atomic level is an indispensable requirement to make the most of all their potential. The lithographic techniques used in conventional nanotechnology do not yet have such resolution and precision.

In the year 2010, however, a way was found to synthesise nanoribbons with atomic precision by means of the so-called molecular self-assembly. Molecules designed for this purpose are deposited onto a surface in such a way that they react with each other and give rise to perfectly specified graphene nanoribbons by means of a highly reproducible process and without any other external mediation than heating to the required temperature.

In 2013 a team of scientists from the University of Berkeley and the Centre for Materials Physics (CFM), a mixed CSIC (Spanish National Research Council) and UPV/EHU (University of the Basque Country) centre, extended this very concept to new molecules that were forming wider graphene nanoribbons and therefore with new electronic properties.

This same group has now managed to go a step further by creating, through this self-assembly, heterostructures that blend segments of graphene nanoribbons of two different widths.

The forming of heterostructures with different materials has been a concept widely used in electronic engineering and has enabled huge advances to be made in conventional electronics. "We have now managed for the first time to form heterostructures of graphene nanoribbons modulating their width on a molecular level with atomic precision.

What is more, their subsequent characterisation by means of scanning tunnelling microscopy and spectroscopy, complemented with first principles theoretical calculations, has shown that it gives rise to a system with very interesting electronic properties which include, for example, the creation of what are known as quantum wells," pointed out the scientist Dimas de Oteyza, who has participated in this project.

This work, the results of which are published in the journal Nature Nanotechnology, therefore constitutes a significant success towards the desired deployment of graphene in commercial electronic applications.

Dr Dimas G. de Oteyza, who was previously at Berkeley and at the CFM, is currently working at the Donostia International Physics Center (DIPC) as a Fellow Gipuzkoa.

The Fellows Gipuzkoa programme, funded by the Chartered Provincial Council of Gipuzkoa, is in fact devoted to bringing back young researchers with solid post-doctoral training in internationally prestigious groups and centres, by offering them a platform for reincorporation through contracts with a duration of up to five years, which enables them to compete in the best of conditions to obtain tenured positions as researchers in our country.

© 2015 Angel Business Communications. Permission required.

#### Bibliographical reference

Bandgap Engineering of Bottom-Up Synthesized Graphene Nanoribbons by Controlled Heterojunctions. Y.-C. Chen, T. Cao, C. Chen, Z. Pedramrazi, D. Haberer, D. G. de Oteyza, F. Fischer, S. Loiue, M. F. Crommie, Nature Nanotechnology (2015) DOI: 10.1038/ nnano.2014.307.

## Breakthrough promises

secure communications and faster computers

Scientists develop microscopic component small enough to fit onto a standard silicon chip that can generate a continuous supply of entangled photons.

#### INDUSTRY RESEARCH

UNLIKE BILBO'S MAGIC RING, which entangles human hearts, engineers have created a new micro-ring that entangles individual particles of light, an important first step in a whole host of new technologies.

Entanglement - the instantaneous connection between two particles no matter their distance apart - is one of the most intriguing and promising phenomena in all of physics. Properly harnessed, entangled photons could revolutionize computing, communications, and cyber security.

Though readily created in the lab and by comparatively large-scale optoelectronic components, a practical source of entangled photons that can fit onto an ordinary computer chip has been elusive. New research, reported in The Optical Society's (OSA) new journal Optica, describes how a team of scientists has developed, for the first time, a microscopic component that is small enough to fit onto a standard silicon chip that can generate a continuous supply of entangled photons.

The new design is based on an established silicon technology known as a micro-ring resonator. These resonators are actually loops that are etched onto silicon wafers that can corral and then reemit particles of light. By tailoring the design of this resonator, the researchers created a novel source of entangled photons that is incredibly small and highly efficient, making it an ideal on-chip component.

"The main advantage of our new source is that it is at the same time small, bright, and silicon based," said Daniele Bajoni, a researcher at the Università degli Studi di Pavia in Italy and co-author on the paper. "The diameter of the ring resonator is a mere 20 microns, which is about one-tenth of the width of a human hair. Previous sources were hundreds of times larger than the one we developed." From Entanglement to Innovation Scientists and engineers have long recognized the enormous practical potential of entangled photons. This curious manifestation of quantum physics, which Einstein referred to as "spooky action at a distance," has two important implications in real-world technology.

First, if something acts on one of the entangled photons then the other one will respond to that action instantly, even if it is on the opposite side of a computer chip or even the opposite side of the Galaxy. This behaviour could be harnessed to increase the power and speed of computations. The second implication is that the two photons can be considered to be, in some sense, a single entity, which would allow for new communication protocols that are immune to spying.

This seemingly impossible behaviour is essential, therefore, for the development of certain next-generation technologies, such as computers that are vastly more powerful than even today's most advanced supercomputers, and secure telecommunications.

Creating Entanglement on a Chip To bring these new technologies to fruition, however, requires a new class of entangled photon emitters: ones that can be readily incorporated into existing silicon chip technologies. Achieving this goal has been very challenging.

To date, entangled photon emitters which are principally made from specially designed crystals -- could be scaled down to only a few millimetres in size, which is still many orders of magnitude too large for on-chip applications. In addition, these emitters require a great deal of power, which is a valuable commodity in telecommunications and computing.

To overcome these challenges, the researchers explored the potential of ring resonators as a new source for entangled photons. These well-established optoelectronic components can be easily etched onto a silicon wafer in the same manner that other components on semiconductor chips are fashioned. To "pump," or power, the resonator, a laser beam is directed along an optical fiber to the input side of the sample, and then coupled to the resonator where the photons race around the ring. This creates an ideal environment for the photons to mingle and become entangled.

As photons exited the resonator, the researchers were able to observe that a remarkably high percentage of them exhibited the telltale characteristics of entanglement.

"Our device is capable of emitting light with striking quantum mechanical properties never observed in an

Drawing of the silicon ring resonator with its access waveguide. The green wave at the input represents the laser pump, the red and blue wavepackets at the output represent the generated photon pairs, and the infinity symbol linking the two outputs indicates the entanglement between the pair of photons.

integrated source," said Bajoni. "The rate at which the entangled photons are generated is unprecedented for a silicon integrated source, and comparable with that available from bulk crystals that must be pumped by very strong lasers."

#### Applications and future technology

The researchers believe their work is particularly relevant because it demonstrates, for the first time, a quintessential quantum effect, entanglement, in a well-established technology.

"In the last few years, silicon integrated devices have been developed to filter and route light, mainly for telecommunication applications," observed Bajoni. "Our micro-ring resonators can be readily used alongside these devices, moving us toward the ability to fully harness entanglement on a chip." As a result, this research could facilitate the adoption of quantum information technologies, particularly quantum cryptography protocols, which would ensure secure communications in ways that classical cryptography protocols cannot. According to Bajoni and his colleagues,

#### Further reading

Paper: D. Grassani, S. Azzini, M. Liscidini, M. Galli, M. J. Strain, "A micrometer-scale integrated silicon source of time-energy entangled photons," Optica, 2, 1, 88-94 (2015) doi: http://dx.doi. org/10.1364/OPTICA.2.000088

## New solder

## for semiconductors creates technological possibilities

Scientists have demonstrated how semiconductors can be soldered and still deliver good electronic performance.

A RESEARCH TEAM led by the University of Chicago's Dmitri Talapin has demonstrated how semiconductors can be soldered and still deliver good electronic performance.

"We worked out new chemistry for a broad class of compositions relevant to technologically important semiconductors," said Talapin, a professor in chemistry.

Semiconductors sit at the heart of most electronics. From computer chips to solar cells, these materials conduct electricity and make it possible to generate and control electrical current. The compounds that Talapin and his associates have developed can be used to join pieces of semiconductor. Researchers and engineers have long struggled with joining together semiconducting surfaces, which are very sensitive to impurities and structural

"If you put two pieces of semiconductor next to each other, each joint will be unique and in most cases will block transport of charges," Talapin said. "You will not be able to make a reasonably good electronic circuit by simply taking different semiconductor pieces and pressing them against each other as you could do with metals."

Talapin and his associates from UChicago, Argonne National Laboratory, and the Illinois Institute of Technology published their findings in the Jan.

23, 2014, issue of Science. They have developed compounds of cadmium, lead, and bismuth that can be applied as a liquid or paste to join two pieces of a semiconductor by heating them to several hundred degrees Celsius, which is mild by industry standards.

"Our paste or our liquid converts cleanly into a material that will be compositionally matched to the bonded parts, and that required development of new chemistry," Talapin said. "We had to design special molecules that fulfill this requirement so that they do not contaminate the material." After application as a liquid or paste, they decompose to form a seamless joint.

#### **Diverse applications**

"Dr. Talapin's work is exciting because its applications are so diverse," said Eric Ginsburg, assistant director at UChicagoTech, the University's Center for Technology Development and Ventures. "We expect it to be used soon by manufacturers who need to join semiconductor parts, but it could also create new markets in the growing semiconductor industry. For example, it would enable 3-D printing of semiconductors and create possibilities for new technologies."

Ginsburg and Cristianne Frazer, UChicagoTech project manager, have previously helped Talapin to license his technologies. They are working closely with Talapin, industry contacts, and investors to determine a strategy for developing the new solder material.

Use of the U.S. Department of Energy's Advanced Photon Source at Argonne was critical to the project's success. "The classical, top-down manufacturing process in the silicon industry does not require soldering," Talapin said. Instead, industry engineers make a large silicon crystal, then cut, carve and etch it into the desired shapes.

Semiconductor soldering is unlikely to have a major impact on today's mainstream silicon technology, but could lead to the development of less expensive, solution-processed semiconductors needed for entry into new markets. Among these markets are printable electronics, 3-D printing, flat panel display manufacturing solar cells and thermoelectric heat-to electricity generators for the Internet of Things (IoT).

Printable electronics requires assembly of semiconductors from small pieces, putting tiny grains together like Legos. "It's like what people call additive manufacturing, when you add things and build from pieces," Talapin said. "If you want to assemble pieces, you need a solder or glue or connectors."

3-D printing is an exponentially growing market, Talapin noted. "We can 3-D print, to my knowledge, almost any class of materials, but not semiconductors." His new solder may change that. A tiny transistor operates each pixel in current-generation flat-screen televisions. These transistors currently

#### INDUSTRY RESEARCH

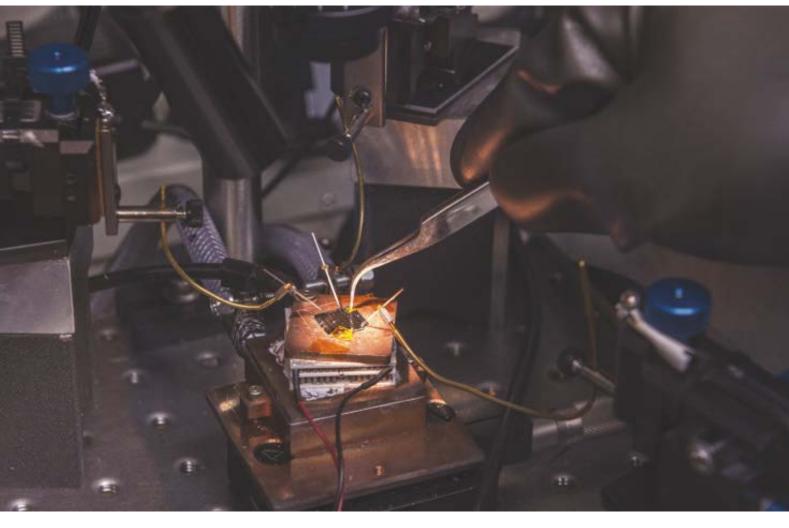

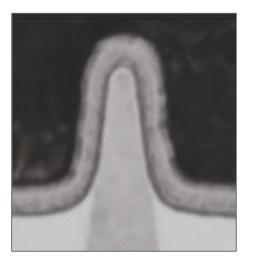

Semiconductor devices like this one now can be joined electronically with a new solder developed by chemistry Professor Dmitri Talapin's research group at the University of Chicago. Credit: Rob Kozloff, University of Chicago.

are manufactured via vacuum methods, but industry experts expect that to change to printing and other less expensive solution-based manufacturing techniques.

#### Internet of Things

The Internet of Things is a growing network of everyday objects -- traffic lights and cars, for example -- that can communicate automatically via miniature web servers. Tiny sensors will be integrated in buildings and bridges to immediately report a crack or other structure failure. Semiconductors will be needed to convert sunlight or heat to electrical currents used to receive, process and transmit information within such a network.

"That requires very inexpensive semiconductors for electronic circuits and devices that come essentially at the price of a postage stamp," Talapin said. Printing electronics in a way similar to

printing postage stamps. It is a chemistry problem to find the right "inks" for this purpose, he said. "Right now postcards and magazines are simply colourful, but there's nothing that precludes them from being colourful and electronically active, so that as ink dries it forms a film that can conduct charges. It's not sci-fi these days."

Solar cells also represent an increasingly lucrative, highly competitive, multibilliondollar annual market, one that fuels the quest for improved solutionprocess manufacturing methods for semiconductors.

"Solution-processed semiconductors is a huge field. We definitely have hundreds of competitors, both in academic settings and in companies," Talapin said. "It's a very competitive area because it's now on the final approach to big money." The Science article mentioned in passing that their semiconductor

soldering approach set a new record for electron mobility in solution-processed semiconductors, a measure for how quickly electrons move through the materials. The new record is almost 10 times faster than the old one. "It's mind-blowing," Talapin said. Funding: II-VI Foundation, Department of Energy, National Science Foundation, and the Keck Foundation.

© 2015 Angel Business Communications. Permission required.

#### **Further reading**

#### INDUSTRY RESEARCH

THE RICE LAB of chemist James Tour discovered last year that firing a laser at an inexpensive polymer burned off other elements and left a film of porous graphene, the much-studied atom-thick lattice of carbon. The researchers viewed the porous, conductive material as a perfect electrode for supercapacitors or electronic circuits.

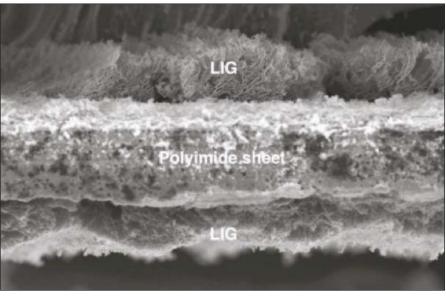

An electron microscope image shows the cross section of laser-induced graphene burned into both sides of a polyimide substrate. The flexible material created at Rice University has the potential for use in electronics or for energy storage.

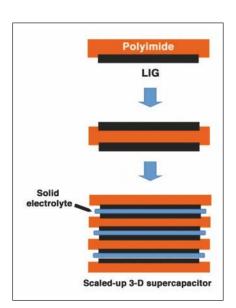

To prove it, members of the Tour group have since extended their work to make vertically aligned supercapacitors with laser-induced graphene on both sides of a polymer sheet. The sections are then stacked with solid electrolytes in between for a multilayer sandwich with multiple microsupercapacitors.

The flexible stacks show excellent energy-storage capacity and power potential and can be scaled up for commercial applications. LIG can be made in air at ambient temperature, perhaps in industrial quantities through roll-to-roll processes, Tour said. The research was reported in Applied Materials and Interfaces.

A schematic shows the process developed by Rice University scientists to make vertical microsupercapacitors with laser-induced graphene. The flexible devices show potential for use in wearable and next-generation electronics. Credit: Tour Group/Rice University

An electron microscope image shows the cross section of laser-induced graphene burned into both sides of a polyimide substrate. The flexible material created at Rice University has the potential for use in electronics or for energy storage. Credit: Tour Group/Rice University. Courtesy of the Tour Group.

Capacitors use an electrostatic charge to store energy they can release quickly, to a camera's flash, for example. Unlike chemical-based rechargeable batteries, capacitors charge fast and release all their energy at once when triggered. But chemical batteries hold far more energy. Supercapacitors combine useful qualities of both -- the fast charge/discharge of capacitors and high-energy capacity of batteries -- into one package.

LIG supercapacitors appear able to do all that with the added benefits of flexibility and scalability. The flexibility ensures they can easily conform to varied packages -- they can be rolled within a cylinder, for instance -- without giving up any of the device's performance.

"What we've made are comparable to microsupercapacitors being commercialized now, but our ability to put devices into a 3-D configuration allows us to pack a lot of them into a very small area," Tour said. "We simply stack them up.

"The other key is that we're doing this very simply. Nothing about the process requires a clean room. It's done on a commercial laser system, as found in routine machine shops, in the open air." Ripples, wrinkles and sub-10-nanometer pores in the surface and atomic-level imperfections give LIG its ability to store a lot of energy. But the graphene retains

its ability to move electrons quickly and gives it the quick charge-and-release characteristics of a supercapacitor. In testing, the researchers charged and discharged the devices for thousands of cycles with almost no loss of capacitance.

To show how well their supercapacitors scale up for applications, the researchers wired pairs of each variety of device in serial and parallel. As expected, they found the serial devices delivered double the working voltage, while the parallels doubled the discharge time at the same current density. The vertical supercapacitors showed almost no change in electrical performance when flexed, even after 8,000 bending

Tour said that while thin-film lithium ion batteries are able to store more energy, LIG supercapacitors of the same size offer three times the performance in power (the speed at which energy flows). And the LIG devices can easily scale up for increased capacity.

"We've demonstrated that these are going to be excellent components of the flexible electronics that will soon be embedded in clothing and consumer goods," he said.

© 2015 Angel Business Communications. Permission required.

## Patented process builds better semiconductors, improves electronic devices

THROUGH a surprise research discovery, a Kansas State University chemical engineer has found the icing on the cake for electronic devices.

Jim Edgar, university distinguished professor of chemical engineering, has received a patent for his invention "Off-axis silicon carbide substrates," which is a process for building better semiconductors. The research may help improve electronic devices and

could benefit the power electronics industry and manufacturers of semiconductor devices.

Electronics are made of semiconductors crystals that must be layered perfectly for the electronic device to work.

"It's like a stacked cake separated by layers of icing," Edgar said. "When the layers of semiconductors don't match up very well, it introduces defects. Any

time there is a defect, it degrades the efficiency of the device."

Edgar's research has developed a better way to build semiconductors and layer them to minimize potential defects -- an important discovery for manufacturers. Edgar describes the research discovery as serendipitous. Several years ago, when Yi Zhang, a 2011 doctoral graduate in chemical engineering, was working in the laboratory, she found a

substrate sample that was very smooth. Collaborative researchers at the State University of New York at Stony Brook and the University of Bristol in the United Kingdom later confirmed the layer's presence and proved that it had fewer defects than on the standard substrate.

"We have applied this process to other systems," Edgar said. "We are working on materials we started with, but that it can be applied to a lot of different materials."

Some of Edgar's latest research focuses on two different boron compounds: boron phosphide and icosahedral phosphide. The researchers received support from the National Science Foundation.

© 2015 Angel Business Communications. Permission required.

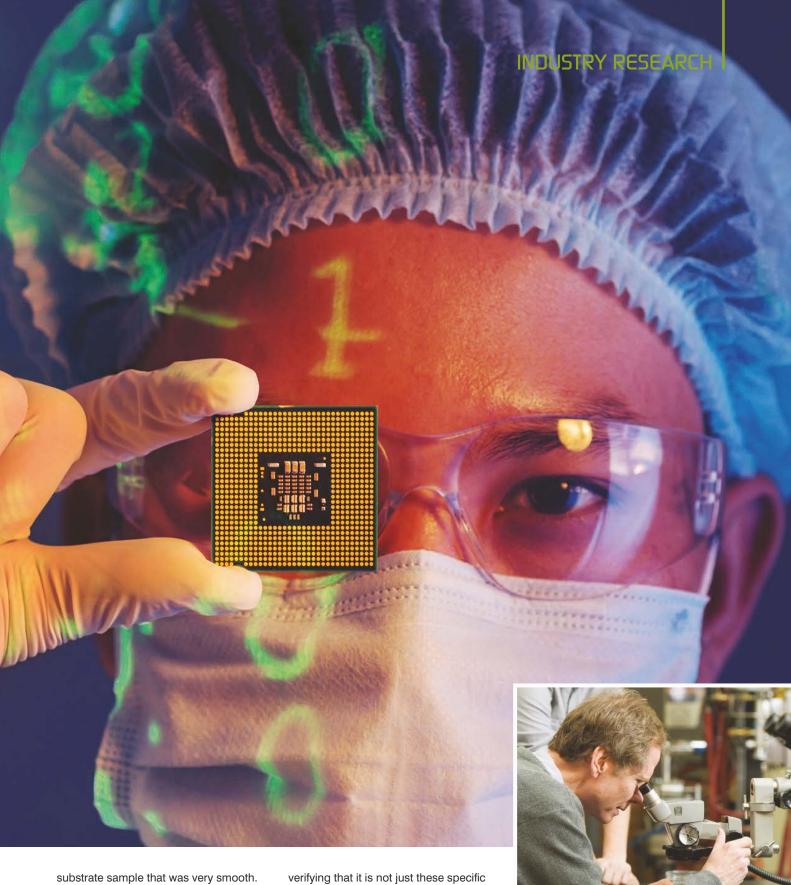

Jim Edgar, university distinguished professor of chemical engineering at Kansas State University, has received a patent for his process that can build better semiconductors and improve electronic devices. Credit: Image courtesy of Kansas State University

## THE MEMORY ROADMAP:

## a paradigm shift from 2D to 3D

"There will never be enough memory": this idea has driven the continuous scaling of memory technologies. Today, DRAM and Flash, both charge-based memory concepts, represent the largest memory markets. For a long time, experts have predicted that emerging memories, such as STT-MRAM, resistive RAM and phasechange memory, all resistance based, would replace the common DRAM and Flash technologies in the Terabit era. According to Jan Van Houdt, Chief Scientist at imec and IEEE Fellow, we will first witness a paradigm shift from planar towards 3D technologies, rather than from charge-based to resistance-based memory.

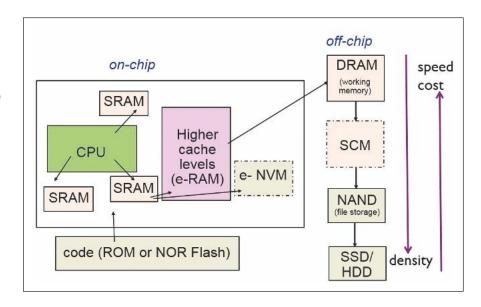

IN TODAY'S ELECTRONIC SYSTEMS, a large part of the system area is consumed by memories. Jan Van Houdt: "Let's take a closer look at CPU (or central processing unit) centric systems, used in for example personal computer and server applications. Close to the CPU, on-chip, static random access memories (or SRAMs) are the dominant memories. These embedded SRAMs are volatile and excel in speed. But they

consist of 6 transistors, and are therefore rather big and have a large cost per bit. Also on chip, less fast and somewhat denser, are higher cache memory levels, mostly made in SRAM or embedded DRAM technology. Off chip, farther away from the CPU, you find ROM (read only memory) or NOR Flash memories for code execution, DRAM chips for the working memory, and non-volatile Flash NAND memory chips for storage. In

general, memories located farther away from the CPU are cheaper, slower, denser and less volatile."

The ever increasing performance of computation platforms and the consumer's hunger for storing and exchanging ever more data drive the need to keep on scaling memory technologies. For a long time, memory experts have been dreaming of one

#### **MEMORY - ROADMAP**

unified memory, a scalable memory concept that would replace all the different memories. Jan van Houdt: "This idea has meanwhile been abandoned. Electronic systems require ever more different memories with different sizes and specifications. For the terabit era, we expect that the memory hierarchy becomes even more complex. We will soon witness the introduction of two new memory classes: storage class memory

(or SCM) and embedded non-volatile memory (or e-NVM). With SCM, we fill up the gap between DRAM and Flash. It will provide an intermediate step between high-density Flash and high-performance DRAM in terms of latency, speed and cost. SCM will mainly serve the server market: Google, Yahoo, Facebook... they will benefit from this new class of memories which do not necessarily require 10 years of retention. Another

newcomer, embedded non-volatile memory, is today only present in some particular applications (microcontrollers and smart cards). Current non-volatile technologies like Flash are too complex to embed in high-end CMOS technology. Especially for mobile applications, there is growing interest in a new embedded non-volatile memory technology."

#### DRAM and Flash memories: scaling issues

Today, the memory market is dominated by DRAM and Flash memories. DRAM chips are now available up to 8GB densities in a 25nm technology node, while Flash has ended up at 16nm half pitch dimensions, yielding 128GB on a single chip with 2 or even 3 bits per cell. Both memories are charge based, and this generates some particular scaling issues.

Jan Van Houdt: "DRAM is structurally a very simple type of memory. It consists of one transistor and one capacitor that can be either charged or discharged. However, upon further scaling, this concept runs out of steam. One of the problems is related to periodic DRAM refreshment. Today, a DRAM memory is being refreshed about 16 times per second to deal with the slow discharge of the capacitor. When further scaled, the capacitor has to be refreshed even more frequently, hindering the performance of the memory. Scaling the capacitor not only increases the leakage, but also the aspect ratio, which has already increased to 35 for conventional double-sided crown capacitors. A new architecture, the one-pillar architecture, with new electrode materials and higher-k dielectrics, partly solves this problem. But even this pillar capacitor cannot be scaled down below 15nm." Nevertheless, DRAM scaling can continue, but not in the classical way. Jan Van Houdt: "An interesting way to scale on performance and power, is 3D stacking: stacking different DRAM dies and connecting them by using through-Si vias (TSVs).

#### MEMORY - ROADMAP

This leads to the so-called hybrid memory cube, which also allows to take many logic functions off-(memory-) chip and optimize the chip system as a whole. A disadvantage of this solution is cost, since TSV technology is still a quite expensive technology."

With Flash, the problem is more complicated. Flash memory stores information in an array of memory cells, mostly made from floating-gate transistors. While in traditional devices, each cell stores one bit of information, more advanced concepts store 2 or even 3 bits per cell. Jan Van Houdt: "Today, a NAND Flash cell in a 4F2 cell layout provides the smallest dimension. But when we decrease the half pitch of the cell array, the threshold voltage shift associated with the tunneling of one electron towards the floating gate, dramatically increases towards several 100mV's. This limits programming accuracy dramatically at the 10nm technology node, and unless new smart ways around this 'single electron limit' are found, this could very well be the end of planar NAND technology. So, we are running out of electrons. The most attractive solution is to go 3D. Not by die stacking, as in DRAM, but by stacking vertical cells by using a charge trap Flash architecture. Following this 'bit cost scaling' (or BiCS) concept, the memory cell transistors are placed vertically on the chip in order to increase the density even further. This way, up to 32 cells have already been stacked in a functional device, and first products are on the market."

#### What about the emerging memory technologies: STT-MRAM, PCM and RRAM?

In the past years, experts have predicted that new memory technologies, mainly resistance-based, would replace 'old'

The classical (server-based) memory hierarchy.

DRAM and Flash technologies in the years to come. At first, it was believed that phase change memory (or PCM) could replace NOR Flash, while resistive RAM (or RRAM) would replace NAND Flash. Spin-torque transfer memory was identified as the only technology that could potentially replace DRAM due to its high endurance.

Jan Van Houdt: "Recently, more and more experts believe that these new memory technologies may first end up in embedded applications and in storage class memory. Take STT-MRAM, for example. The core element of STT-MRAM is a magnetic tunnel junction in which a thin dielectric layer, usually 4 to 5 atomic mono-layers, is sandwiched between a magnetic fixed layer and a magnetic free layer. Writing of the memory cell is performed by switching the magnetization of this free magnetic layer. STT-MRAM is a very promising memory concept because of

its non-volatility, high-speed, low-voltage switching (<1V) and almost unlimited read/write endurance. But there are some disadvantages. The memory is too large for Flash replacement, and cannot (yet) be used in a 3D configuration. Also, STT-MRAM is current driven, ending up with a high write power and large peripheral devices. The technology could potentially replace DRAM, but can at the moment not compete with the low cost of DRAM technology. Eventually, if (3D) DRAM has finally hit the wall, and STT-MRAM is able to shrink its size, this would become a possibility. On a shorter term, I expect STT-MRAM to replace embedded SRAM in higher caching levels (L3)."

Another resistance-based technology is PCM, which is based on the melting and (re-)crystallization of chalcogenide material. Jan Van Houdt: "PCM is a reasonably mature technology with a high endurance (on cell level), large programming window and non-

Recently, more and more experts believe that these new memory technologies may first end up in embedded applications and in storage class memory

#### MEMORY - ROADMAP

destructive read. The technology writes reasonably fast at low voltage. However, due to its large programming power and issues with material (in)stability, PCM is currently seen as a replacement for the declining market of NOR Flash technology."

And then there is RRAM, which relies on the formation of a conductive filament in an insulating layer. Jan Van Houdt: "Typically, an RRAM device consists of two electrodes that sandwich a thin dielectric layer. This layer serves as the ion transport and storage medium. The ionic movements and structural changes in this medium, caused by e.g. an electric field, cause a measureable change of the device resistance. RRAM comes in several flavors: oxide RAM (or OXRAM), conductive bridging RAM (or CBRAM) and vacancy modulated conductive oxide (or VMCO). In general, the concept is low cost, low voltage and can be realized with 'standard materials', like TaO<sub>x</sub>. But although the resistive switching structures show excellent memory characteristics, implementation of high-density RRAM arrays lags behind, mainly due to sneak current issues.