Volume 37 Issue V 2015

🕒 @siliconsemi

www.siliconsemiconductor.net

#### Lab productivity

#### Nanoparticle silver ink

Taking charge of change

2015 A year of merger mania in semiconductor manufacturing

inside SISSILICON SEMICONDUCTOR

Features, News Review, Industry Analysis, Research News and much more. <u>Free Weekly E Ne</u>ws round up , go to <u>www.siliconsemiconductor.net</u>

## Optimize the Thermal Performance of your Process Equipment.

Extensive computational tools enable product designs to be highly refined for ultimate performance.

Multi-zone circuit layouts in a polyimide construction are highly customized to deliver exacting performance up to 250°C.

EZ-ZONE<sup>®</sup> RM Multiloop controllers are fully scalable with up to 152 PID Loops and 256 monitor points per system. Watlow provides innovative solutions to help process tool manufacturers meet the needs of the semiconductor technology roadmap. Our approach is to work collaboratively to help solve complex thermal challenges associated with state-of-theart manufacturing processes; helping to improve yield, throughput and cost of ownership. This includes innovative heaters, controllers and sensors for use in front-end and back-end applications such as CVD, PECVD, Etch, Diffusion, Bonding, IC test and more.

WATLOV

ASSURANT<sup>™</sup> gas and pump line heaters feature high temperature capabilities with low outgassing.

#### Contact Watlow<sup>®</sup> today for the latest thermal solutions for semiconductor applications.

| Europear | Technical Sales Offices               | Italy |

|----------|---------------------------------------|-------|

| Germany  | +49 (0) 7253-9400-0<br>info@watlow.de | Spain |

| France   | +33 1 41 32 79 70<br>info@watlow.fr   | UK    |

+39 02 4588841 italyinfo@watlow.com +34 91 675 1292

+44 (0) 115-964-0777 info@watlow.co.uk

info@watlow.es

## executiveview

by Mark Andrews, Technical Contributor

### The journey continues

MOVIE CHARACTERS are memorable if they're larger than life. Like a movie, the ever-changing face of semiconductor technology has its own characters that keep us watching as the storyline unfolds.

2015 started enthusiastically. Early analyst predictions foresaw 7 percent growth. But even as TSMC and other major chip makers reported strong 2014 earnings, clouds crept into forecasts. The real storm would not appear for months, so as they always do, new products came to market including advances such as ever-shrinking SoC devices, wearable's, flexible and printable electronics, sensors, radar and moves toward realising IoT expansion.

By mid-2015 the year that looked so promising shifted to a picture of something gained/something lost – when good news came, a 'Grinch' would turn gentle breezes into gales. We saw exciting new products and technologies in one hand / shrinking chip revenue in the other. And so it went.

In July the plot line followed a path signaled earlier: China's continual expansionist ambitions were overtaken by reality. Growth slowed and analysts clamored that they had, '...seen it coming for years.' Companies supplying China, buying from China or hoping for a future there inhaled sharply and forecasts slipped.

As the final days of 2015 tick away, many are looking for a happy ending. Take heart—there is one in the works. Semiconductor technology remains an industry that powers global economic optimism, even as some hoping for 7 percent

Publishing Editor Jackie Cannon Senior Sales Executive Robin Halder Sales Manager Shehzad Munshi USA Representatives Tom Brun Brun Media Janice Jenkins Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor Circulation Director Jan Smoothy Chief Operating Officer Stephen Whitehurst

+44 (0)1923 690205 iackie.cannon@angelbc.com +44 (0)2476 718109 robin.halder@angelbc.com shehzad.munshi@angelbc.com +44 (0)1923 690215 E: tbrun@brunmedia.com +001 724 539-2404 E: iienkins@brunmedia.com +001 724-929-3550 sharon.cowley@angelbc.com +44(0)1923690200mitch.gaynor@angelbc.com +44 (0)1923 690214 +44 (0)1923 690200 ian.smoothv@angelbc.com stephen.whitehurst@angelbc.com +44 (0)2476 718970

growth will likely see less. Semiconductor researchers, designers and manufacturers deliver the products and technologies that consumers embrace every day. Whether it's wearable sensors, autonomous vehicles, IoT, new mobile computing solutions or renewable energy to thwart climate change, semiconductors deliver the solutions that our global community wants and needs.

The reality of semiconductors' role in the 21st century – unlike a movie plot – should give you optimism that if not today, then tomorrow the industry will see solid growth. Yet remember that all expansion reverses, just as reversals are themselves turned around.

Directors Bill Dunlop Uprichard – CEO, Stephen Whitehurst – COO, Jan Smoothy – CFO, Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal, Jason Holloway.

Published by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Herts WD17 1JA, UK. T: +44 (0)1923 690200 F: +44 (0)1923 690201 E: ask@angelbc.com

Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com

Silicon Semiconductor is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/€158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be downowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd Copyright 2015. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor (ISSN 1096-598X) is published four times a year for a subscription of \$198 by Angel Business Communications Ltd. (A Hannay House, 39 Clarendon Road, Watford, Herst WD17 1JA, UK. Periodicals postage paid at Rahway, NJ. POSTMASTER: send address changes to: Silicon Semiconductor, c/o Mercury International Ltd, 365 Blair Road, Avenel, NJ 07001. Printed by: Pensord Press. © Copyright 2015. ISSN 2050-7798 (Print) ISSN 2050-77801 (Online).

### Best of 2015 features

## 14 Nanoparticle silver ink to improve manufacturing

Genes'Ink and KELENN Technology spoke to Mark Andrews and explained how their system can improve printed electronics manufacturing.

## 18 Electroplating: An old technology for the future

Kevin Witt, ClassOne Technology Vice President, offers insight into ways that classic electroplating processes are being updated to address the industry's latest metal deposition requirements.

#### 24 Critical challenges in gas supply to advanced semiconductor manufacturing fabs

Shrinking device geometries challenge manufacturers to more precisely manage gases and other critical materials. Dr. Anish Tolia, Ph.D., Head of Global Marketing, Linde Electronics, explains why scale, quality, supply chain, and ustainability should dominate production planning.

#### 30 Taking charge of change

Handling product and process change on an industrial scale is no simple subject. But there are solutions to manage change that semiconductor manufacturers have embraced as both effective and profitable.

#### **36** The memory roadmap: A paradigm shift from 2D to 3D

"There will never be enough memory": this idea has driven the continuous scaling of memory technologies. Today, DRAM and Flash, both charge-based memory concepts, represent the largest memory markets. For a long time, experts have predicted that emerging memories, such as STT-MRAM, resistive RAM and phase-change memory, all resistance based, would replace the common DRAM and Flash technologies in the Terabit era.

## 40 Beyond the curve to foldable displays

Lightweight, unbreakable, flexible and wearable; these are just a few of the development targets for contemporary consumer electronics. Over the past ouple of years interest in flexible displays that meet these needs has increased significantly, with the market for this flexible display technology predicted to expand to more than \$21billion by 2020<sup>1</sup>.

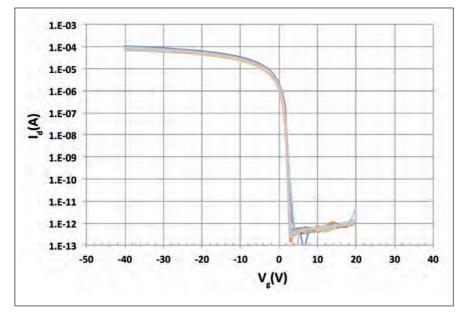

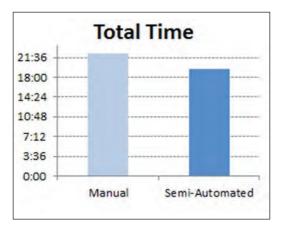

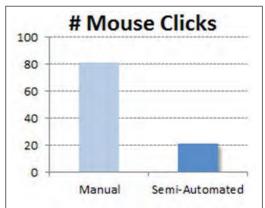

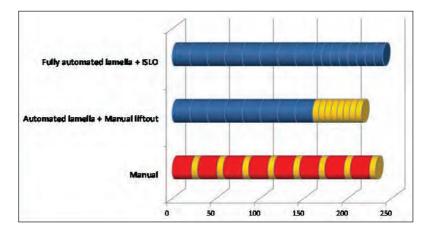

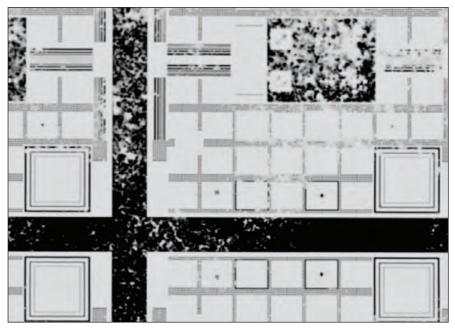

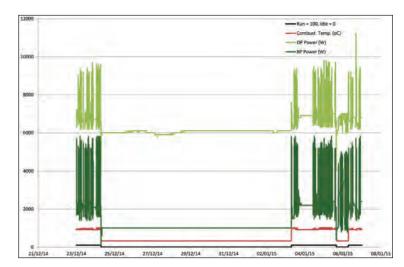

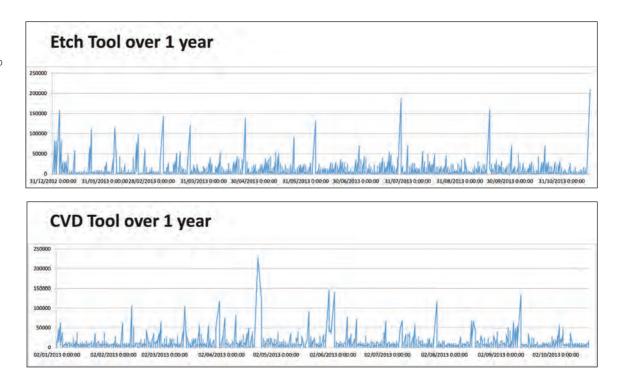

## 44 Maximizing productivity in the lab

Failure analysis labs typically involve lots of manual tasks performed by highly skilled operators. However, failure analysis labs are now adopting practices from the fab, such as increased automation, as the need for more and faster failure analysis feedback becomes critical to maximising yield.

# contents

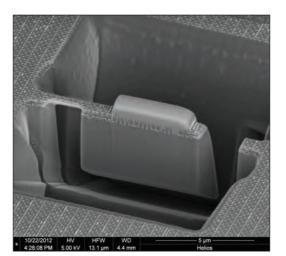

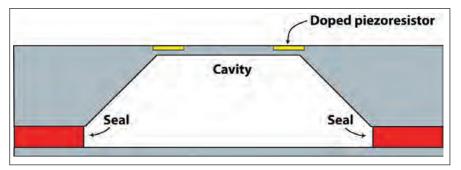

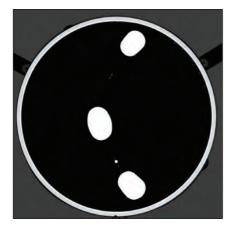

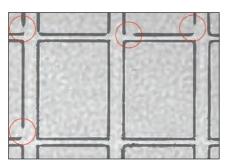

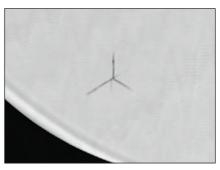

#### 50 AMI tools image MEMS devices

The long-term functioning of a MEMS device depends on the integrity of the cavity; and the imaging and analysis of the seal protecting the cavity depends on acoustic micro imaging tools.

## 54 With the 7nm FinFET, parasitics come into play

With every new technology generation, an understanding of the interdependencies between design and technology becomes increasingly important. A shining example is the scaling of FinFET technology beyond 10nm.

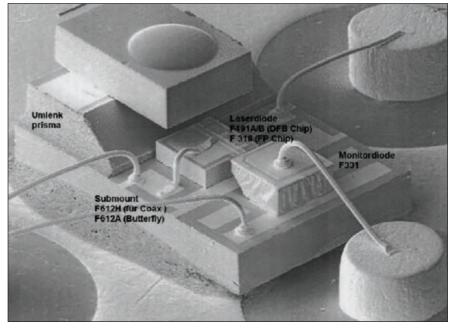

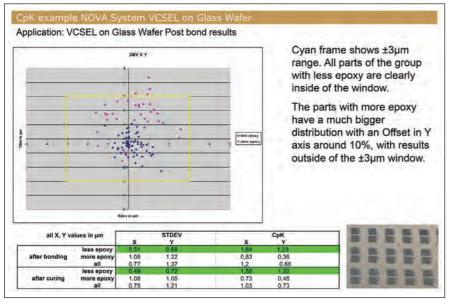

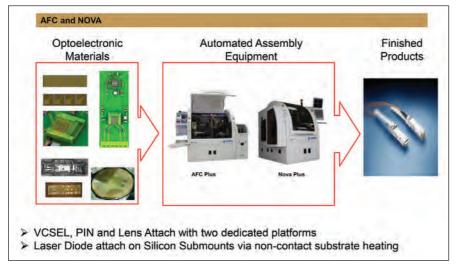

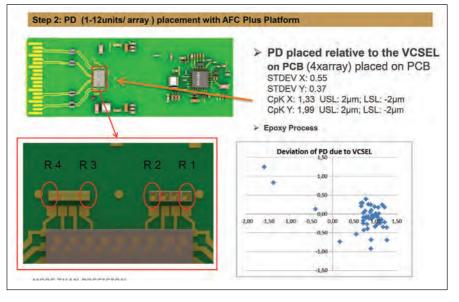

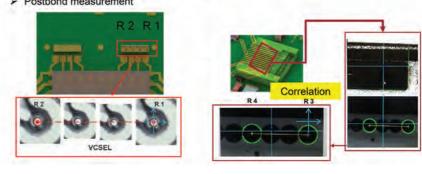

#### 56 More than Precision: Meeting the challenge of accurately assembling active optical cables

No one would dispute the fact that active optical cable (AOC) and Silicon Photonics technologies are getting tremendous attention due to the need of transferring more and more data at ever faster data rates. This is putting immense pressure on the assembly equipment suppliers to offer advanced tools and processes that push the envelope of ultra-precise die placement.

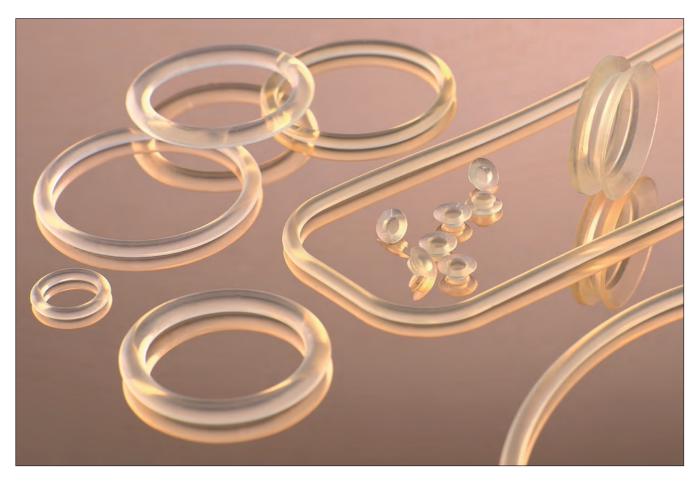

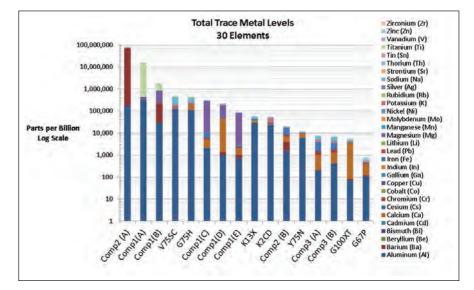

#### 61 Killer consumables: How clean are your seals?

In semiconductor manufacturing the threat of particle and especially metallic contamination to transistor integrity is a significant and potentially costly threat. This is mainly true for front end processing but, due to the high mobility of many of these contaminants, it remains a threat at all stages of the manufacturing process flow.

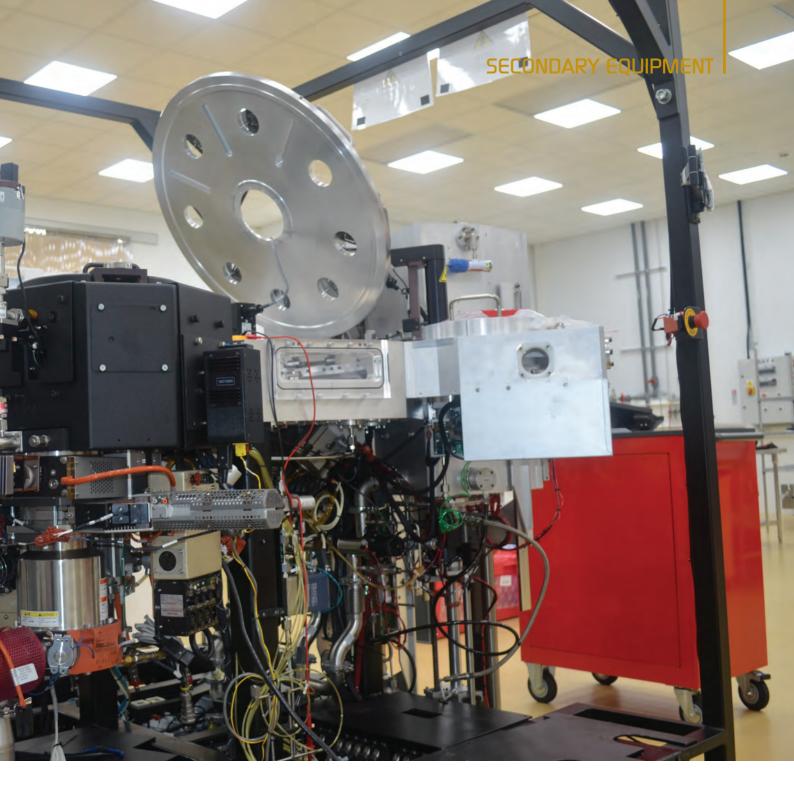

#### 64 The role of OEMS and secondary equipment in the new IoT fab

To be competitive in the IoT market, cost is key and making the successful adaptation of secondary equipment is paramount.

## 68 New paths to greener semiconductors

Manufacturers are working to reduce the environmental impacts of next-generation technologies by challenging common practices in today's semiconductor plants.

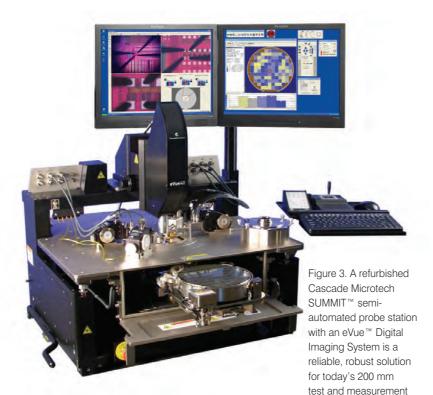

## 74 Sourcing refurbished semiconductor equipment

Erik Hanson, Refurbished Products Manager, Cascade Microtech, Inc tells Silicon Semiconductor why going straight to the OEM for refurbished equipment reduces both the risk and cost.

#### 78 Silicon tech evolves to 450 mm

Manufacturers are pooling resources to double global IC capacity. Will achieving the next milestone in silicon evolution give members a competitive edge?

# A year of merger mania in semiconductor manufacturing

2015 set records for merger activity as the China slowdown created global economic headwinds. While some markets contract, new opportunities are poised to strengthen 2016 growth.

2015 WAS A RECORD-SETTING YEAR across the semiconductor industry. Merger mania hit new highs, with 18 deals of \$100 million or more making headlines. Mergers closing by October 31st were valued at \$110 billion. Yet some major deals did not happen, as was the case with the Tokyo Electron/Applied Materials match-up. Meanwhile, the acquisition of KLA-Tencor by Lam Research Corporation announced in fourth quarter moves forward with the approval of most industry watchers even though regulators have not officially weighed-in.

Contributor Mark Andrews saw that some of the biggest headlines came from China, where the country's long-standing expansionist business climate ran into substancial headwinds that shook financial markets this past summer. World markets largely recovered thanks to infusions of capital by the Chinese central bank and the resilience of the United States' economy. Despite China's negative pull, Asia is still on-track to be the world's major producer of semiconductors by 2020.

While technological advances continue to drive product innovation, headlines in 2015 often spoke of incremental advances for many applications. That having been said, new ground was broken in memory, photonics, 5G, IoT and progress towards 450mm technologies.

As 2015 draws to a close, industry analysts remain optimistic that growth—perhaps at a slower pace—will continue in the New Year thanks to the ever-inventive minds of the world's best manufacturers, suppliers, researchers and entrepreneurs.

#### 2015 Year in Review

#### January

Researchers at IC Insights got off to a busy start, forecasting seven percent growth in semiconductor manufacturing. This prediction was within the range of SEMI's forecasts as well.

While several researchers foresaw a China slowdown, none were looking for the fall-off that markets would experience by the summer. leaders in Beijing signalled that China intended to fund semiconductor expansion to the tune of \$10 billion (USD.) Meanwhile a new report from IC Insights listed the top 50 foundries of 2015; nine were in China. At the Consumer Electronics Show in Las Vegas (USA), Intel announced a new chip family that included 14 new designs targeting PC and notebook applications. Intel also showcased what it claimed to be the smallest wearable system on a chip (SoC) device that was clearly targeting the wearables market.

Taiwan Semiconductor Manufacturing Company (TSMC) announced record quarterly 2014 profits, but also signalled that a slowdown might be coming. As if they heard the forecast in Taiwan and wanted to exert their own influence,

#### February

A week into leading the SEMI trade group, John Neuffer helped celebrate record setting revenues in 2014 of nearly \$338 billion, up 9.9 percent over 2013. China was first on his list of stops as the world's number-two economy sought expanded roles in high-tech manufacturing, placing more emphasis on key capabilities that have up to this point typically been located elsewhere across the globe.

As China topped many analysts' mustwatch lists, America's Silicon Valley again made news, this time for its continued expansion. Perhaps seeing ahead to the rocky road we'd find by mid-2015, Silicon Valley executives reported continuing expansion of the type not experienced since the 'bubble' days of the dotcom boom that burst in 2001, but of a type that they believed was more sustainable compared to the breakneck pace set before 2000-2001. February saw TSMC announcing a \$16 billion investment in its plants. Spoiler Alert: That ambitious plan would be trimmed later in 2015, with capital investment falling from \$10.5 to \$8 billion, reflecting the reality of a shrinking market.

Even though February saw shouting matches over whose semiconductor fabs might grow the fastest, Internet of Things (IoT) technology grabbed headlines as well. Security experts at ARM outlined what they saw as the road ahead for realizing the technology's potential, putting cash into the gambit by acquiring Offspark, a company specializing in Transport Layer Security (TLS), technology that was already used widely across commerce and communications infrastructure. Elsewhere in the IoT universe, experts meeting at the Boston Embedded Systems Conference said that the competing platforms for realizing IoT secure connectivity were still sorting themselves out and would be for years to come, which could affect how quickly IoT devices are brought to market.

#### March

Merger mania continued in a big way on March 1st with the announcement by NXP and Freescale that they planned to combine resources, creating a \$10 billion revenue machine. If finalized the merger would create the world's 9th largest chip maker, and dominate the market for automotive and general purpose microcontroller semiconductors. NXP and Freescale valued the deal at \$40 billion.

As if to put an exclamation point on the issue of global fab hot spots, analyst at IC Insights said that Asia would have nearly 70 percent of all fabs by 2019, with the bulk (40 percent,) located in Taiwan and South Korea. China made the list with a forecast of 10.9 percent of global fabs by 2019.

In a move that surprised no one except those with their heads in the sand, exhibitors at Wearable TechCon noted that smart glasses from Epson, Google and Sony were resetting expectations and were turning their attentions to business applications. The appeal of Google Glass and similar products in work environments that challenge staff to maintain constant contact across multiple applications as well as 'interface' with their human counterparts seems intuitive. One has to wonder why the developers didn't seek those markets at the same time they were promoting smart glasses to mainstream consumers.

Technology news came on several fronts, with researchers at North-eastern University announcing that they had uncovered basic principles that should enable the development of quantum Wigner crystals, predicted as theoretically possible in 1934. The breakthroughs could enable ultra-high-electron mobility several orders of magnitude superior to either silicon or graphene. On the optical front the University of Washington in Seattle and California's Stanford University announced development of nano-scale lasers that could be ideal for transmitting data optically around semiconductor chips.

March ended with analysts 'cooling' to the idea of an Intel/Altera combination. Although speculation about Intel acquiring an FPGA leader has persisted for years, that market is tiny compared to Intel's primary computing markets. Analysts wondered why the chip maker would spend \$13 billion for a company with perhaps \$2 billion in annual revenues.

#### April

IoT again made headlines as EuroCPS pledged to fund as many as 30 teams across Europe with up to \$25 million to underwrite a three-year initiative in fundamental and practical research. The goal was to enable greater capabilities and market growth for all things wearable tied to Internet of Things applications. The initiative particularly targets smaller research groups that often are challenged when competing against major global enterprises with deep R&D pockets.

At midpoint, engineers commemorated the entry of Gordon Moore's 'simple' assertion that transistors could double in capacity within the same area of a silicon chip every two years. While the ramifications of this idea are still being argued the impact of Moore's Law is undeniable. The successful pursuit of greater computing capacity led to not just faster and cheaper computers, but also myriad applications from communications and the Internet to smartphones, tablets and now the dawn of IoT.

April saw announcements from the Internet Engineering Task Force (IETF) about new, faster chips and the software to drive them, all tied to software-defined networking (SDN). Meanwhile, the Optical Internetworking Forum (OIF) is leading initiatives to create bonded Ethernet channels. The ultimate goal of both groups is to create 400 Gb/s channels bonded to create pipes as 'fat' as 1.6 Tb/s.

Analysts also went out on a limb to predict Intel's process technology of choice for its next two generations, driving toward 10nm devices. Analyst David Kanter (based on the contents of papers released by the company and other assorted data,) predicted Intel would rely on quantum well FETs using two new materials—indium gallium arsenide (InGaAs) for n-type transistors and strained germanium for p-type devices. Only time will tell, but if he is correct Intel could leap frog competitors one more time.

Closing out a busy April was Apple's achievement of yet another sales record: \$58 billion in the second quarter compared to the same time in 2014. Although Apple declined at the time to make forecasts on its then-anticipated Watch segment, iPhone and Mac sales dropped. Nevertheless the world's largest electronics company reported a \$13.6 billion profit. Not bad for a 'cooling' market.

#### May

We all know how frustrating it can be to find the right component for a new design, and engineer Javier Solorzano responded by co-founding a new company called Elektet that he believes will aid designers, and manufacturers searching for just the right component. This isn't your basic parametric search engine like many chip vendors have built into their websites. His approach is a 'Google-like' system that could work across the web to help engineers locate parts despite widely varying product IDs and descriptions across the industry.

It was no surprise to discover the industry heavy weights Qualcomm and Broadcom again found something to dispute, this time in how the LTE-Unlicensed (LTE-U) spectrum is being utilized alongside Licensed Assisted Access. The US Federal Communications Commission is interested in whether the two companies are sharing spectrum and not

looking into ways that incumbent Wi-Fi technologies might be infringed upon. The inquiry could potentially pit cellular network providers against the 'cable guys' as well as users of unlicensed spectrum. Stay tuned....

Infineon made additional headlines by announcing that the Munich, Germany based company was looking for a buyer to take over its Newport (Wales) wafer fab that came to the company as part of its acquisition of International Rectifier. Although seen as an eventual blow to the local economy, Infineon stated it expected work to continue in Newport through the end of 2017, indicating that demand is sufficient for a potentially protracted sales process.

News from the wearables market included opinions from the Embedded Systems Conference in California that indicated relatively modest sales figures could be tied to the fact that while devices such as Apple Watch have many capabilities, they haven't achieved the kind of data throughput that medical practitioners would need to use the devices for patient diagnoses or monitoring. One problem lies in the sensor design, which is fine for other systems today but lacks the contextual data that a doctor or other practitioner would need.

Samsung made headlines by announcing it would ramp production of its 10nm devices starting in 2016. The new node is expected to be in full production by the end of next year. International Business Strategies CEO Handel Jones said that if Samsung can achieve 10nm at production volumes, the impact could be very disruptive in the market.

#### June

The month began with good news for Taiwan Semiconductor Manufacturing Company (TSMC) when MediaTek announced that it would continue using the company as its leading-edge chip foundry. This announcement laid to rest fears that MediaTek might be shifting its business to TSMC rival Samsung.

Defending his company's decision to buy Altera, Intel CEO Brian Krzanich said the combined companies would ship integrated products starting in late 2016 for servers and some still-undetermined embedded systems. His message was met with some scepticism by Linley Gwennap, a principal analyst at The Linley Group and a veteran Intel analyst. Krzanich estimated new business could be "...be quite a bit bigger than a billion dollars..."

'Sanity' became the watchword at an early June conference attended by Internet of Things (IoT) experts who labelled projections of up to 50 billion IoT devices by 2020 as 'Fantasy.' A more realistic projection is 1.9 billion IoT devices shipping by 2020, according to Linley Gwennap who said he took a bottoms-up look at real world stats, such as the global middle class population (about 2 billion by 2020) and the number of homes expected to have Wi-Fi or other broadband connections (around 600 million.)

Analysts at the Computex Taipei event looking for ways to realize maximum penetration for wearable IoT devices stated that 72 million wearable devices worth \$17 million will ship this year, pointing to a compound annual growth rate (CAGR) of 18 percent. They projected up to 156 million units worth \$39 billion by 2019. Bruce James, director of mobile solutions for ARM, with chip designs in 90 percent of with world's smartphones, is betting on watch and watch-like wearables as emerging leaders.

By mid-month, reports were surfacing noting that demand for semiconductors was weakening in the second quarter with some assemblers in Asia suggesting double-digit fall offs compared to second quarter in 2014. The iPhone supply chain and automotive markets remained a bright spots in 2015 forecasts.

While current semiconductor shipments were falling compared to 2014, China's top foundry, Semiconductor Manufacturing International Corporation (SMIC), forged a joint venture with Huawei, Qualcomm and the imec research institute to develop its own technology for 14nm process production at a SMIC fab by 2020. Beijing had earlier committed to spending \$10 billion for domestic semiconductor production, which could include the 14nm development project analysts said.

#### July

IBM and GlobalFoundries got the month off to a busy start, announcing that they had closed the deal transferring IBM's Burlington, Vermont (USA) foundry to GF. The deal was worth \$1.5 billion and as a condition IBM agreed to make

Sanity' became the watchword at an early June conference attended by Internet of Things (IoT) experts who labelled projections of up to 50 billion IoT devices by 2020 as 'Fantasy.'

GlobalFoundries its supplier for the next 10 years while Global also obtained ownership of 10,000 IBM semiconductor patents.

5G took another step towards becoming the next cellular communications standard when it was announced that demonstration projects, trials and specifications work would begin within months of the July announcement. 5G is expected to deliver a number of benefits compared to 4G technologies, including maximum data rates of 10- to 20 Gb/s, likely confined to dense urban areas.

Analysts at Credit Suisse in Taipei said MediaTek (the world's third largest chip designer,) is expected to continue making market share gains in the LTE market at the expense of top-rated Qualcomm because of its position in the fast-growing Chinese smartphone market. MediaTek's market share in LTE is likely to double (up to 45 percent of the China market) by December 31st.

In other news from Asia, the Tsinghua Unigroup (China) bid \$23 billion to buy Micron Technology. While the deal would fill one of the biggest strategic holes in China's chip industry it was expected to raise political issues all the way to the US White House. Micron is the second largest chip maker in the US (behind Intel) with revenue of \$16.8 billion in 2014.

By mid-July analysts were reporting that semiconductor sales were in a two-year slump due primarily to weak demand for PCs and some smartphones. Gartner Group reported that chip sales rose a mere 2.2 percent by the middle of 2015, with growth of just 1.3 percent predicted by year's end. At the same time, Gartner predicted that growth would return to a more typical 4-5 percent range starting in 2017, thanks to expected growth in IoT, the expansion of smartphone sales in growing markets such as India and China, and more positive momentum in other markets including Europe and the Americas.

The Consumer Electronics Association, also presenting at the Flash Memory Summit, said that while wearables constitute the fastest growing segment they are also the smallest and most fragmented

Taiwan Semiconductor Manufacturing Co. (TSMC), the world's largest chip foundry, said the outlook for the rest of 2015 is worse than the company previously expected because customers were digesting an inventory glut built earlier this year. While the company expected an increase in demand for computer, consumer and industrial segment devices, it expected smartphones and other handset device markets to decline.

The impact of declining growth in China was fully felt across global financial markets starting in July. Even though the official sources in Beijing reported 7 percent annual growth, outside economists and analysts pointed to the government's widely observed miscalculation of 'deflator' factors that are a broad measure of prices affecting a country's economy. Economists stated that Chinese gross domestic product (GPD) figures were wrong by up to 2 percentage points.

The vulnerability of devices linked to the internet hit home in July as car maker Jeep and its parent, Fiat Chrysler Automotive (FCA), admitted that Jeep vehicles were vulnerable to hacker attacks. FCA stated that blame for the vulnerability was shared with Sprint, FCA's system integrator, and Harmon Kardon, designer of in-vehicle infotainment systems.

The revelation came at the end of the month when a hacker team succeeded in taking over vehicle functions by exploiting software weaknesses. A sweeping recall of 1.4 million vehicles resulted to proactively address the problem; no driver injuries were reported at the time.

NXP celebrated strong financial

performance as the month drew to a close. The company reported \$1.506 billion in revenue, a 12 percent increase compared to 2014. High performance mixed signal products for security, connectivity and mobility made the second quarter the 12th consecutive double-digit growth period for the company.

#### August

At a meeting of IoT professionals at the Embedded Systems Conference (ESC), the group conceded that Internet of Things technology will not take off until two lynchpin requirements are met: development of wide area networks and lower costs for hardware crucial to seamless connectivity. While hardware costs typically decline as deployment accelerates, the lack of networks hinders overall market development. While the group referenced good efforts to create networks by the LoRa Allience led by Semtech, and SigFox (France), the group foresaw that IoT devices would slowly enter the market since cellular networks appear to be, '...the only viable option for that kind of coverage for the next ten years....'

At the Flash Memory Summit Samsung announced solid-state drives (SSDs) and systems geared to drive 3-D NAND into mass markets. But analysts and even other vendors suggested that it may take most of 2016 before the technology is ready for mainstream implementation. The Consumer Electronics Association, also presenting at the Flash Memory Summit, said that while wearables constitute the fastest growing segment they are also the smallest and most fragmented. This led other analysts to conclude that fitness trackers and

smart watches both show signs of gaining traction with consumers, yet they have penetrated just 11 percent of US households, nowhere near the 60 percent penetration of smartphones in the US.

Altera executives seemed edgy about prospects of life under the Intel umbrella. Analysts, speaking with current senior executives and those who have already departed the company, cited fears of how well Intel integrates acquired companies given its PC-oriented leadership. Despite Intel's long-standing attempts to shed its dependence on personal computing, they cited what happened to past acquisition targets including Level One, DSP Communications, Sialogis Corporation, Giga A/S as cause for concern over how well Altera might fare. Smart meters are driving the IC market supporting IoT in utility markets. Global revenues for semiconductors used in water, gas and electric meters reached \$1.2 billion in 2014, with growth standing at 11 percent according to IHS researchers. Growth opportunities remain as more public utilities change over to the technology, which better tracks customer utilization. The future points toward integrated ICs to do the work now being done by individual components; manufacturers with integration expertise are best positioned to take advantage of this growing market.

MediaTek's rapid growth in 4G smartphones is likely to be undermined by handset makers in China who are designing their own chips, according to Hong Kong based Bernstein Research. Spreadtrum Communications and Huawei are eroding MediaTek's position because the maturing market is favoring Chinese players that are backed and subsidized by the government. At the same time MediaTek is gaining market share from Qualcomm in the 4G and high-end segment.

#### September

Chinese upstart Phytium Technology made headlines with is aggressive 'Mars' design that was released at the Hot Chips event. The Mars architecture is designed for ARM-based servers and utilized advanced SoCs not seen before in mass market applications. But despite the fact that Phytium is only three years old, the company has deep roots in Chinese electronics—it is a subsidiary of China Electronics Corporation, one of the oldest state-run enterprises.

Gartner researchers reported that chip sales in September continued to slow largely due to stagnant sales of semiconductors headed into PCs, tablets and smartphones. They forecast that growth could dip to a fraction of one percent, but might rebound once third quarter sales figures were finalized. TSMC announced that it expected to begin early production utilizing a 10nm process later in 2015, and planned to achieve 7nm production capability by 2017. The road map that the company unveiled in Silicon Vallev meetings also pointed towards a reduced cost version of its 16nm process in 2016 and a broad portfolio of specialty processes for IoT, automotive and sensor applications.

Perhaps leaping ahead of consumer acceptance and comfort, analysts at the Linley Group announced their research points to the availability of fully autonomous, self-driving cars by 2022. This new technology will help double the size of today's \$10 billion automotive semiconductor market by 2025. Feedback from automotive industry insiders suggest that today's driver assistance and automation systems are mere 'appetizers' for the main course of self-driving cars.

The technology is already there and being tested, remarked Linley Gwennap, principal of the Linley Group. The researcher did not elaborate on how willing consumers will be to hand steering wheels over to microprocessors. Anyone for a replay of 'I Robot'?

#### October

Google's' Nest Labs announced it planned to release its Weave protocol in 2016 and will involve partners that will use it to connect smart home products such as locks, light switches and cameras. The advancement is seen by industry observers as another way that IoT devices are moving into more mainstream applications visible to a wider range of consumers.

The slump in PC market semiconductor sales was reflected in Micron Technology's report of declining sales revenue for a third straight quarter. Even though PC sales remain sluggish, the company reported healthy demand for memory chips in other end markets,

Analysts at the Linley Group announced their research points to the availability of fully autonomous, self-driving cars by 2022. This new technology will help double the size of today's \$10 billion automotive semiconductor market by 2025

pointing to the continued shift away from traditional computing and towards other small form factor computer options such as tablets and smartphones.

Marvell announced that it is sampling the first products based upon its MoChi approach to building modular SoCs. One of the company's two new 64-bit ARM processors is the first to implement finallevel cache (FLC) technology, which aims to shrink external DRAM requirements. The MoChi design concept is Marvell's approach to creating products that operate like SoCs when interacting with application software, but may actually be composed of multiple die in one or more packages. The concept enables chips made in different processes to work together as closely as if they were grouped together on the same die.

Extreme Ultra Violet (EUV) technology got a boost from imec researchers in Belgium working with Cadence Design Systems. The two organizations partnered to create two 5nm test chips using a mix of 193i and EUV techniques. The researchers believe this approach represents the best alternative to breach the barrier limits of Moore's Law in transistor evolution.

Dell bid \$67 billion to buy storage giant EMC in a mid-October acquisition proposal. The deal was billed as the largest high-tech purchase to date, but received mixed reviews from industry watchers. The analysts were unenthusiastic largely because both companies—though large and successful—are seeing flat or declining sales in their segments. Industry insiders wondered how the company would deliver growth to investors given little prospect for innovation beyond the company's existing portfolios.

The town of Bristol, England took innovation to a new height by turning itself into a 'petri dish' for experiments in communications and the Internet of Things (IoT.) Bristol received grants and gifts totally 75 million (GBP) to create wired and wireless infrastructure for a smart city. It aims to build applications ranging from assisted living programs for seniors to driverless cars and solar energy.

Taiwanese semiconductor giant TSMC reduced early-2015 planned capital expenditures of \$10.5 billion to \$8 billion, a 25 percent cut. The move came on the heels of slowing global demand for semiconductors.

Lam Research Corporation announced its intention to purchase KLA-Tencor, marking the start of the industry's largest merger of high performance process tool makers. The \$10.6 billion deal was observed by some analysts as an effort to put the new company ahead of its arch-rival, Applied Materials. The merger was approved by both boards, but comes at a time of increasing regulatory scrutiny of M&A activity. In April Applied Materials and Tokyo Electron cancelled a planned \$29 billion mega merger, citing opposition from antitrust interests at the US Department of Justice. Yet most analysts approve of the Lam/KLA deal, saying it will give the combined entity a decisive edge in global competition through pricing power it likely would not enjoy as separate companies.

#### November

Fears about automobiles being vulnerable to hacking led to more media coverage of the dilemmas facing car makers. While manufacturers have guietly sought to patch firmware and software holes, evidence remains that many newer car infotainment and computing systems are vulnerable to attacks that gain access through radio or cellular frequencies, or piggybacking on the short range signals from a consumer's key fob. According to the US Federal Bureau of Investigation (FBI), between April 2014 and June 2015, there were 992 'ransomeware' related complaints, with victims reporting losses totalling more than \$18 million.

The Semiconductor Industry Association (SIA) reported that global chips sales declined 3 percent to \$85.2 billion in third quarter. The decline followed trends from earlier reports, with declines in traditional PC sales and smartphones as leading indicators. At the same time sales picked up in September, leading some analysts to hope for a better year-end tally. Qualcomm reported to shareholders that it believed smartphone growth would continue to slow in 2016, and that prices for chips going into handsets will continue to fall, though less sharply than they did in 2015. Qualcomm also expects China OEMs will command a growing share of the market.

While Qualcomm fretted over its future with Samsung and with other key handset makers, its prospects may be looking up when it comes to printed electronics. Raghu Das, CEO or IDTechEx, hosted an industry forum on the subject in Silicon Valley, saying that the technology had matured to a point that engineers need to 'get printed electronics out of the lab and utilize their capabilities.'

Those poised to take advantage of these possibilities include Qualcomm and a handful of other companies. Qualcomm later presented new products at the forum, including a label that can gather data from a golf club and feed info to the player's smartphone. A thin-film battery maker, Blue Spark Technologies, displayed a bandage that can deliver a patients temperature information to a handset.

The strengthening US dollar compared to the position of other world currencies has taken a toll on the semiconductor industry, among many, and is forecast to lead to contraction in worldwide chips sales in 2015.

Samsung is set to make inroads into Intel's position as the world's largest chip maker in 2015, according to market forecasts compiled by researchers at IC Insights. The researchers say that Intel continues to suffer from its dependence on the weakening personal computer market and its limited success breaking into mobile phone applications. IC Insights expects Intel sales to contract 2 percent in 2015 compared to Samsung growing its chip revenue 10 percent, which should bring them in at \$6 billion behind Intel's forecast of \$50 billion in chip sales.

Merger mania continued in November

as Renesas Electronics became an investment target attractive to a number of suitors outside Japan, including China's Tsinghua Unigroup and Germany's Infineon Technologies. Tsinghua's ambitions in memory chips are well established since it is seeking a foothold in the logic business, especially in automotive and MCU segments.

Infineon is said to regard Renesas as an ideal fit, based on the Japanese chip vendor's strength in infotainment, head unit and digital cockpit technologies and other areas of automotive electronics where Infineon lags. It's also important that Renesas has a strong position with both Japanese and European automakers. A rocky 2015 did not deter Taiwanese semiconductor giant TSMC from predicting this month that it will achieve double-digit growth during the coming year and that its 10nm process is on schedule for production in 2016. The company's CEO also predicted similar results for 2015 at the end of 2014, so it remains to be seen how well the company will fare against headwinds now buffeting the

#### December

T.J. Rodgers, outspoken CEO and President of Cypress Semiconductor, said this month that he expects 'merger mania' which is now driving consolidation across the industry may continue for another two years. The CEO cited a causal relationship between what executives see in the market and fears that not merging with a like-minded company could mean they are losing out on potential market share gains. Chip companies executed more than 18 M&A transactions worth more than \$100 million in the last year; M&A activity totalling \$110 billion was reported as of October 31st.

A rocky 2015 did not deter Taiwanese semiconductor giant TSMC from predicting this month that it will achieve double-digit growth during the coming year and that its 10nm process is on schedule for production in 2016. The company's CEO also predicted similar results for 2015 at the end of 2014, so it remains to be seen how well the company will fare against headwinds now buffeting the industry. TSMC also announced that its 7nm process was on track; the company could see 10nm as a transitional node leading directly into 7nm.

For only the second time in the last 25 years, business growth for the top chip manufacturers in 2015 is expected to beat the growth of top fabless companies, according to researchers at IC Insights. The change in fortunes is largely credited to Samsung's decision to use its own Exynos application processor in smartphones at the expense of Qualcomm. This growth notwithstanding, IC Insights said they also expect 2015 will be rather flat overall for the top 10 integrated device manufacturers (IDMs), while the top 10 fabless companies are expected to slip into slightly negative figures this year.

The International Electron Devices Meeting (IEDM) in Washington, DC was the setting for word from senior ARM researchers that even though it is getting harder and more costly to make chips smaller and faster, there is hope to be found in advancing Moore's Law. To combat an increasing set of design limitations, engineers will need to employ a host of remedies that could fragment and possibly dilute economies of scale.

This may result in significant sacrifices in density for the sake of schedules, combined with balancing the need for cost effectiveness with market timing. The researchers see hope in what is industry **77**

already being done and will be done to increase productivity and cut costs, noting as an example that multiple passes through lithography will increase costs while new steppers coming online for 7nm will be 50 percent faster than those used at 28nm.

United Microelectronics Corporation (UMC), the world's third largest foundry, said it expects to open a joint venture 300mm fab in China about two months earlier than expected. Production should begin in the third quarter of 2015. A spokesperson credited the aggressive readiness posture to faster than expected construction in China. Meanwhile, UMC arch rival, Taiwan's TSMC, also announced plans to open its first wholly owned 300mm fab in china, slated to begin production in the second half of 2018.

A Chinese government-backed firm has initiated a bidding war for chip maker Fairchild Semiconductor International. In November Fairchild accepted an acquisition offer from ON Semiconductor Corporation. The offer it accepted was for \$2.4 billion, while the offer from the unsolicited bidder was for \$2.6 billion. While Fairchild said it will review the new offer, its board has already accepted the ON Semiconductor bid, so it is unclear whether the Chinese company has a chance to acquire Fairchild.

© 2015 Angel Business Communications. Permission required.

## Nanoparticle Silver ink to improve manufacturing

Genes'Ink and KELENN Technology spoke to Mark Andrews and explained how their system can improve printed electronics manufacturing.

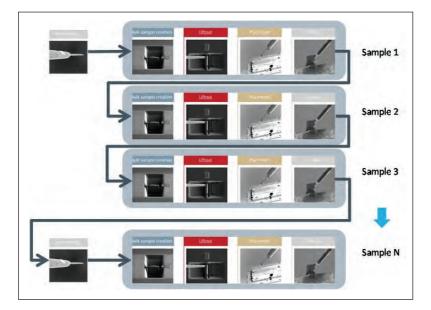

GENES'INK and KELENN Technology recently announced co-development of a new proprietary nanoparticle silver ink for KELENN's new high speed printer, the KSCAN PE300. According to both companies, these new technologies can radically accelerate production and efficiency of printed electronics for RFID antennas, capacitors, OLED active layers and many other applications. We asked Genes'Ink and KELENN Technology to detail how their system can improve printed electronics manufacturing.

$igodoldsymbol{Q}$  Speed appears a central attribute of the new KSCAN PE300, moving at 'several meters per minute' compared to only 'a few centimeters per hour' in existing systems -How do you achieve such a performance leap?

A Such performance is achieved thanks to a combination of innovations and technologies. KELENN Technology and Genes'Ink have worked together to create an industrial digital silver ink that can be used with KELENN Technology's proprietary high speed piezo jetting modules. KELENN Technology has redesigned the architecture, electronics and fluid management to be able to properly handle approximately 30 key parameters, in relation with printed electronics, such as rheology, nozzle clogging and many others.

$igodoldsymbol{\Theta}$  Has speed been an impediment to more widespread adoption of inkjet printing of electronic circuits in the overall marketplace?

A Yes. Actually 90 percent of printed electronics is handled by screen printing. Companies are focusing on prototyping circuit design and ink formulation with low speed table top inkjet printers. However, the whole work has to be done once again when moving into industrial production scale. For the industry, before the KSCAN PE300 was announced, it was safer to put the emphasis on screen printing for production.

$igodoldsymbol{\Theta}$  The partnership between Genes' Ink and KELENN Technology seems a natural outgrowth of a conductive ink maker working with a developer of improved electronic circuit printing technology – How do (ink and printer) complement one another to offer a better solution?

${\sf A}\,$  To be able to print at fast speed, the volume of ink per droplets must be reduced compared to traditional methods. This matches perfectly with nanoparticle silver

ink, which requires less quantities for a given conductivity compared to traditional silver ink. From a consumable cost point of view, KELENN Technology's printer (uses) less ink for a given conductivity compared to screen printing. So the customer benefits from two major cost areas: improved productivity and reduced consumable costs.

Genes'Ink cites several applications of the new technology – active layers in OLEDs, RFID antennas, production capacitor printing. Can the technology also be used for printing the silver bus bars, lattice fingers or other elements in photovoltaic cells (printing on polysilicon wafers)?

A Yes, for example, in a very interesting case study, we have demonstrated that one litre of ink could produce approximately 1 million patterns.

Line accuracy seems another advantage of the new technology – Is this a benefit of the new nanoparticle ink, the printer itself, or both?

A Both technologies bring their advantages. The Nano ink specific formulation can be jetted very precisely. The printer has a native resolution of 1200 dpi with a positioning precision of the print head of up to  $2 \mu m$ . But mostly, the precision is due to a number of innovations in the design of inkjet deposition that are brought to the market by KELENN Technology.

Ink silver content reduction (50 percent less) in your new system is another clear advantage – Can you elaborate about what enables the new printer and ink to use so much less silver?

A The (ink) formulation is a key feature. Nanoparticles of silver have the ability to coalescence and show conductivity with a very limited amount of ink and at low

temperature. Reliability of inkjet deposition is a key feature as well; we are looking for a first pass yield of 95 percent. The quantity of ink waste per job has been greatly reduced by KELENN Technology compared to screen printing or other inkjet (systems).

- C The new technology mentions usage of photonic annealing in a controlled environment with a specialised atmosphere Is the vacuum system and gas supply control self-contained, or does the manufacturer need to have out-board vacuum and gas delivery/evacuation?

- A Yes, the whole technical environment is self-contained to facilitate installation and commissioning. The KSCAN PE300 is fitted with carbon filters for exhaust. In basic configurations, these filters can cope with small to medium productions. For volume production, or a more complex configuration, it is best to add external filters and output.

- What have we not covered that is an additional benefit of the new system?

- A software package is included with the KSCAN PE300 to manage job productions; it interfaces with standard CAD electronics output vector files such as GERBER and simple image files such as TIFF, BMP and JPG. The KSCAN PE300 can also be fitted with a feeder and a stacker.

- O po you believe the new system (ink + printer) offer decisive advantages?

- This system is opening the printed electronics market to industrial printers, not only electronics people. It is easy to use and they already use this kind of system in their plants.

- © 2015 Angel Business Communications. Permission required.

## ADVANCED PLATING For the rest of US – A <u>total</u> package

#### Performance, price — and unbeatable process development support

You've probably heard how much performance ClassOne's ≤200mm electroplating systems deliver — for roughly *half* the prices you'd pay elsewhere. Well, that's just the start. Where ClassOne *really* shines is in helping you develop your plating processes.

#### Get serious help from world-class plating experts

Some users tell us they want to start electroplating for process improvement, but they're not sufficiently experienced in it. That's OK, because our team has literally hundreds of combined years of experience in developing ECD processes and processing equipment; and we *love* to help our customers!

Some equipment makers just drop off your new tool and wish you luck! But at ClassOne, our most important job is helping you to get up and running — and get your processes optimized!

#### We've got you covered, start to finish

Our new Applications Lab in Atlanta is world class and fully equipped with all the right tools. It's not only for showing plating systems in operation — it's where we help you set up processes, start to finish.

We can support you in putting together new processes from scratch. We can process wafers and measure results. We can help you screen and select the right chemistries. And we can advise you on options and integration each step of the way — to dial in your processes exactly the way you want them.

#### Come see for yourself

We're here to help you succeed, and world-class process development support is a key part of that plan. Visit our Atlanta apps lab and see what we mean! Call us: (406) 755-2200. Or email: info@classone.com.

**Class** TECHNDLDGY Advanced Plating For the Rest of Us

www.ClassOne.com • See us at SEMICON West, booth 2521

## **Electroplating** An old technology for the future

Kevin Witt, ClassOne Technology Vice President, offers insight into ways that classic electroplating processes are being updated to address the industry's latest metal deposition requirements.

ALTHOUGH IT MAY SEEM counterintuitive, a great many of the industry's most advanced devices, such as compound semiconductors, MEMs and smart sensors that are used in the latest electronics applications, are not built using the most advanced process technology on the largest wafers. There are a couple of reasons for this. In many cases, such as analog devices, the desired level of functionality can be achieved using 90 nm or larger critical dimensions rather than today's leading-edge 14 nm standard. In others, it can be cost. It makes no sense to invest in a 300 mm process line if market demand can be met using 200 mm wafers.

While large semiconductor manufacturers, especially those producing large volumes of logic or memory devices, have adopted the latest in metal deposition technology, many others have found that time-tested methods of depositing metal onto substrates — such as sputtering and evaporation — have cost-effectively met their requirements. That is changing. As technologies such as wafer-level packaging are increasingly adopted, these useful and relatively inexpensive techniques are reaching their limits. This article will briefly describe some of these limitations and suggest a proven alternative that can overcome them.

#### Capability limits

Sputtering and evaporation are limited in three main areas when it comes to wafer-level packaging applications: poor step coverage; limited feature fill; and poor metal lift-off for small features. Sputtering, for example, is mostly a line-of-sight process that relies on probability and randomness to uniformly deposit the desired thickness of metal on the substrate. High-aspect features, such as deep vias, the thick resist used for copper pillars, or the narrowly spaced lines found in redistribution layers cannot be properly filled. For structures that span different elevations within a die, it can be virtually impossible to achieve greater than 20-30 percent step coverage, even if continuity can be maintained. At the same time, once aspect ratios increase much beyond 3:1, filling features with metal, whether

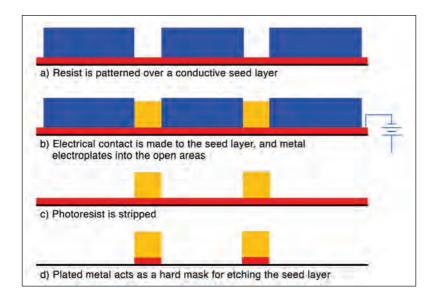

Figure 1. A simplified metal lift-off process.

via sputtering or evaporation, can be compromised by overhangs and step coverage limitations that can result in defects such as voids. Both techniques typically require the removal of excess metal from the substrate. As feature sizes become smaller, however, metal lift-off (Figure 1) becomes a problem because the features are so small they no longer adhere well to the substrate during subsequent processing. Similarly, the edges of features become less well defined and ragged, leading to an increased susceptibility to other types of defects, as well as introducing additional integration issues and challenges.

#### Cost

Sputtering and evaporation both cease to be costeffective techniques when depositing the types of thick films required to build advanced devices used

in wafer-level packaging. Sputtering, for example, is a slow process that becomes extremely expensive when depositing films over a few tenths of a micron in thickness. It would cost a relative fortune and take an unreasonable amount of time to sputter the metal needed for a 90 micron copper pillar, even if the film stress could be managed.

With evaporation, waste becomes a cost issue. By the very nature of the process, the thicker the film to be deposited, the greater the amount of metal that ends up deposited off the substrate, such as inside the system. Finally, there is the raw material cost. At a minimum, the materials used in both sputtering and evaporation techniques must meet the same purity requirements as the deposited film, thereby increasing starting material costs. These very pure raw materials are, by their nature, more expensive than more commonly available, less pure counterparts.

#### The Electroplating alternative

Electroplating is a nearly two-century-old process that uses an electric current from an anode to deposit metal from a solution (the electrolyte) onto a cathode (the substrate). There are typically two electroplating process flows used in device manufacturing. The first, damascene, deposits the metal into features that have been etched into a previously deposited dielectric film or layer. The second, the through-template process, deposits metal in the open areas of a patterned dielectric template, such as photoresist, which is later chemically dissolved or stripped away.

Whichever process flow is used, the basic physics are the same. As shown in Figure 2, a seed layer, which acts as the cathode, is first deposited onto the surface substrate. A resist layer is then deposited and patterned lithographically to create the desired features.

This is often the very same mask that was used for the metal lift-off process. The substrate is placed into a plating solution, voltage is applied, and metal ions are then selectively deposited following the lines of the electromotive force (voltage.) Once the wafer is removed from the bath, rinsed and dried, the resist is then stripped away using standard solvent processing. Finally, the seed layer is etched away using the deposited features as a hard mask, leaving behind the isolated patterned features.

The electroplating process offers significant advantages over sputtering or evaporation for applications such as wafer-level packaging, redistribution lines and interconnects. It can deliver nearly 100 percent step coverage with

The idea for Solstice electroplating tools originally came from ClassOne's sister company, ClassOne Equipment. A long-time provider of quality refurbished tools, they were seeing a trend emerging, especially in small and medium-sized semiconductor manufacturers

> excellent feature fill, minimizing defect and integration issues. A simple, self-organizing process, it also offers deposition rates in excess of 4 microns per minute for some materials, making it an excellent technique for depositing the thick films required to build features such as the 90 micron copper pillars mentioned above. Its faster deposition rate also speeds wafer throughput and lowers overall cost of ownership. Electroplating offers an additional benefit since it is a purification process by nature. As a result, the raw materials need not be of the same level of purity required for sputtering or evaporation, which further lowers production costs. Finally, electroplating offers a much wider process window than the alternative processes, thereby increasing process flexibility.

> As many university students have learned, making and using a small electroplating cell is simple and inexpensive. Outside of the laboratory and in the fab environment, the use of automated equipment and hazardous chemicals introduces concerns that need to be mitigated. There have been many different types of electroplating systems put into service over the years with varying degrees of success. Like most processes in semiconductor device manufacturing, electroplating makes

Figure 2. A simplified electroplating process.

use of potentially dangerous chemicals, so safety is a concern. Exposed or open baths of electroplating chemicals can be risky to both operations and maintenance personnel, as well as to the equipment itself. Chemicals can also pose environmental and facility contamination risks. Care should always be taken to ensure that plating equipment has integrated secondary containment and appropriate fail-safes as well as interlocks, such as those called for in the SEMI S2, CE, or FM4910 specifications. Since plating solutions tend to be corrosive, material compatibility becomes an important issue for safety as well as for maximizing asset longevity.

Once safety guidelines and process controls are taken into consideration, choosing a plating system comes down to the performance to price ratio for the production volumes in guestion. Wet benches are often used for non-critical plating operations and can be either automated or manually operated, depending on production needs. For low levels of non-critical production, the variability in results that arise from manually operated equipment may not become an issue. Alternately, hand operations can become cumbersome as volume levels increase. When reproducibility and its consequent variation reduction matters, or when a high degree of uniformity is demanded, wet benches fall short and single wafer tools are desirable.

Single wafer tools fall into two general categories: fountain platers and paddle platers. Used more widely in the industry, fountain platers place a wafer face down into an overflowing pool while the wafer rotates. By comparison, paddle platers mechanically agitate the electrolyte near the surface of a static wafer. Paddle platers often can achieve higher ultimate plating rates for the same chemistry (due to a higher amount of agitation). But this benefit needs to be considered against the mechanical complexity of the chamber and necessary automation, which lead to increased costs. These tools tend to be physically larger than their fountain plater counterparts, which may be a concern for older, more space-constrained facilities.

#### The future of electroplating: ClassOne Technology's solution

The idea for Solstice electroplating tools originally came from ClassOne's sister company, ClassOne Equipment. A long-time provider of quality refurbished tools, they were seeing a trend emerging, especially in small and medium-sized semiconductor manufacturers. These users were facing a technology transition from vacuum-based deposition to electroplating and needed new equipment; however, their budgets were limited. So, a new company, ClassOne Technology, was created specifically to address those needs. ClassOne's Solstice platform was designed for ≤200 mm wafers, to provide advanced electroplating capabilities at an affordable cost.

#### Experience-grounded innovation

ClassOne Technology immediately brought in a team of seasoned veterans, with over 400 years of combined experience both in designing and using plating systems. They set about creating a new generation of electroplating systems to replace the aging Equinox® plating tool originally developed by Semitool in the early 1990s. Aimed at users of 200 mm and smaller wafers, the design objectives were functionality, reliability and ease of use combined with broad and advanced processing capability. To achieve ClassOne's standards of quality and performance the Solstice team utilized elegant design and best-of-breed components to deliver dependable performance while maximizing cost-efficiency. The Solstice control system employs Windows 7 and is based upon systems that have been in use for over 10 years in other industries. These elements form the basis of all three Solstice systems:

- S8: a fully-automated, cassette-to-cassette production tool with up to eight chambers;

- S4: fully automated like the S8, but with up to four chambers;

- LT: a semi-automated development tool with up to two chambers.

All Solstice tools share components, subassemblies, software and controls. This provides economies of scale and also gives users a seamless path from plating development to full automated production. Using the same chambers for all wafer sizes, for example, allows users to make changes in materials or wafer diameters by simply and quickly changing-out a few relatively inexpensive components. The Solstice ECD family is an excellent example of how an older technology can gain new life by solving emerging problems. Electroplating has significant potential to provide a cost-effective alternative to the sputtering or evaporation of metals for advanced applications. This time-tested technology is now becoming a key enabler and cost reducer for many small and mid-sized device manufacturers who have neither the need nor the budget for larger deposition systems.

© 2015 Angel Business Communications. Permission required.

KEVIN WITT is the VP of Technology at ClassOne Technology and has worked more than 25 years in semiconductor and related high-tech industries.

Prior to ClassOne, he consulted for a variety of techbased companies including VEECO, ESI, BioNano Genomics, TruTag, Advanced Inquiry Systems, SolarSemi Engineering, and The Thompson Group/SEMSYSCO.

#### MODULES

#### FROM CONCEPT TO PRODUCT

COMPACT CLEAN EFFICIENT SERVICES

24/7 GLOBAL SUPPORT

SPARE PARTS LOCAL REPAIR UPGRADES

#### VALVES

#### LEADING TECHNOLOGY

HIGH PURITY ENGINEERED SOLUTIONS CUTTING-EDGE TECHNOLOGY

## Critical challenges in gas supply to advanced semiconductor manufacturing fabs

Shrinking device geometries challenge manufacturers to more precisely manage gases and other critical materials. Dr. Anish Tolia, Ph.D., Head of Global Marketing, Linde Electronics, explains why scale, quality, supply chain, and sustainability should dominate production planning.

Linde

-

RAPID CHANGES in the technical and business environment of semiconductor manufacturing have intensified challenges throughout the supply chain. Semiconductor manufacturers are pushing the limits of physics and driving a constant need for new materials. Semiconductor companies and materials suppliers must formulate mutually profitable models for developing new products to achieve continued success.

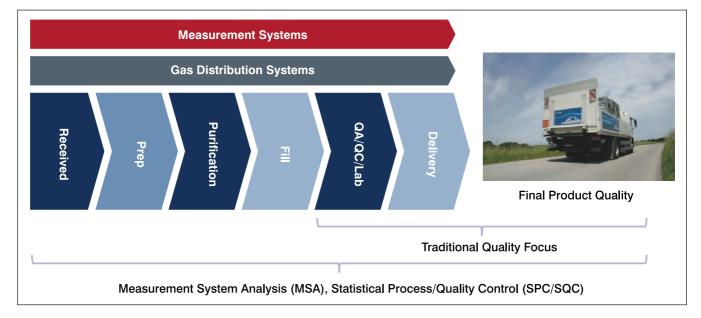

At the same time, process control and purity demands are reaching unprecedented levels due to increasing complexity of the processes and related yield challenges. Tighter production process control and advanced metrology solutions (aka 'fingerprinting') are key to addressing these issues.

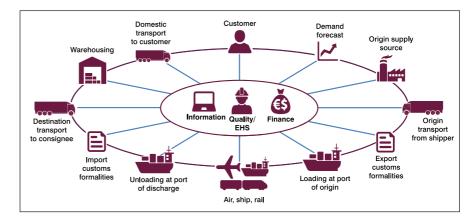

On the business side, industry consolidation continues and fewer customers are building ever larger fabs, which presents materials delivery and environmental challenges. The materials supply chain is increasingly globalized; managing risk and delivering uninterrupted product is critical. Larger scale and more on-site gas generation and delivery schemes are cogent approaches to solve the problems.

Finally, as the global semiconductor industry grows, environmental concerns

and limited natural resources, which include rare gases like helium, krypton, and neon become an area of increasing focus. Innovative solutions like materials recycling can be a useful tool in reducing environmental impact.

This article explores the four key factors in gas supply to advanced semiconductor manufacturing fabs – Scale, Quality, Supply Chain, and Sustainability – as well as the drivers and solutions for each factor.

#### SCALE - Larger fabs + more complex and smaller devices = more gases

Consumers want ever more technologically sophisticated smartphones, tablets, smart watches and other wearables, not to mention automotive, household, and medical electronics. Semiconductor companies are increasing capacity to meet this demand – a 10 percent integrated circuits upsurge worldwide in 2014.

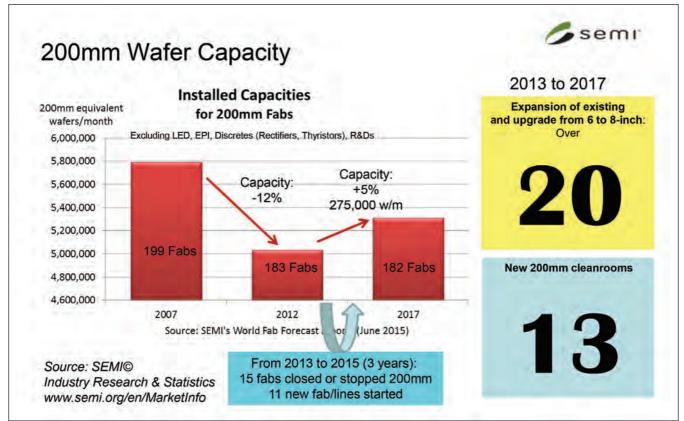

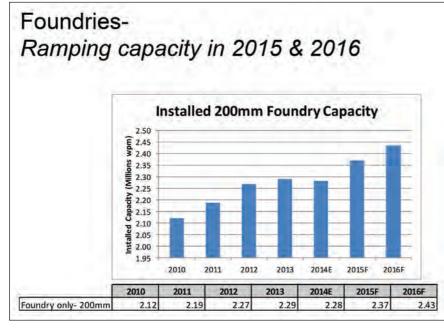

This increase has also predicated a move from MiniFabs (monthly production of 10-30,000 wafers) to MegaFabs (30-80,000 wafers a month) to now GigaFabs (80-100,000 wafers a month). A typical logic foundry is now at 80,000 WSPM (wafer starts per month); a typical memory fab now exceeds 120,000 WSPM. Additionally, many large fabs are now concentrated in clusters (science parks).

The highly competitive mobile devices market is forcing fabs to ramp to higher volumes faster than ever before.

Additionally, development costs for new technology can exceed \$2B (USD). In such an environment, economies of scale are essential for profitable operation.

In order to meet the demand and technological challenges, a larger volume and variety of gases is needed. These gases are used in multiple process steps such as etching/cleaning, deposition, doping, purging, and lithography/patterning in the manufacture of semiconductors.

Not only is the increased size of fabs contributing to the need for more gases, the move from single patterning to multipatterning requires more gases for the production of each wafer.

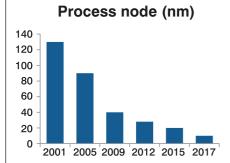

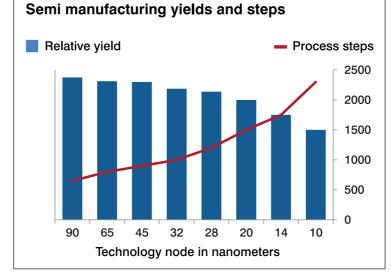

As feature sizes are driven downward. new challenges emerge in maintaining the cost and performance gains. Until about 2006 at the 65 nm node, gains were obtained by shrinking physical devices using direct optical lithography. After that, more benefits were derived by introducing new materials into the process; for example, germanium in the transistor. By 20 nm, the minimal feature size became smaller than the wavelength of light and necessitated workarounds like multi-patterning to overcome physical limitations. All these factors have increased the consumption of gases per wafer.

Because of the need for low power and high performance, which 2D devices cannot handle, the industry is moving to 3D devices, which increases circuit density. This move to 3D FinFET and 3D NAND and the corresponding move to

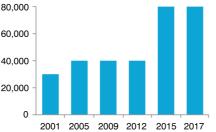

Typical fab size (WSPM)

N<sub>2</sub> consumption (Nm<sup>3</sup>/h)

increased transistor processing – epitaxy, etch, and ALD (atomic layer deposition) – drive the need for new and increased materials to construct more complex devices.

The gas most consumed in the production of electronics is nitrogen  $(N_2)$ . Nitrogen is used for purging vacuum pumps, in abatement systems, and as a process gas. As process nodes have been driven down and the typical fab size has increased, nitrogen consumption has grown substantially. In large advanced fabs, there can be as much as 50,000 cubic meters per hour of nitrogen consumed, which compounds the need for cost-effective, low-energy, on-site nitrogen generators.

Another electronics manufacturing gas that is seeing an increase due to larger fabs and increased capacity is hydrogen. Hydrogen is utilized during epitaxial deposition of silicon (Si) and silicon germanium (SiGe), as well as for surface preparation. Significant volumes

of hydrogen are also anticipated to be used in extreme ultra violet (EUV) in the future as 450mm wafers enter production streams. Hydrogen can be delivered economically as compressed gaseous hydrogen (CGH<sub>2</sub>) or liquid hydrogen (LH<sub>2</sub>) for smaller amounts and distances. However, due to the growing need for hydrogen, more fabs are now demanding onsite production through steam reforming or electrolysis. There is also an upswing in the need for rare gases such as

neon, krypton, xenon, argon, and helium. This increased usage of gases that are not as readily available as nitrogen has driven sporadic temporary worldwide shortages, particularly helium and neon. Rare gases are also used for wafer cooling (helium), as source gases in lasers (neon), and as sputtering gases (argon and krypton).

So what are the critical challenges for fabs when the volume and type of gases multiplies due to added processes and more complex technology?

#### QUALITY - Changing needs due to complex technology

The first consideration for fabs is maintaining quality. Typically as the technology node gets smaller, the number of processes goes up and yield potentially goes down with each added process step. Manufacturers are diligently trying to overcome limits to stay on track with Moore's Law; doing so requires more stringent controls.

Critical process steps in high-volume semiconductor device manufacturing at aggressive feature sizes require stringent control of variability. For a silicon wafer with 100 or more advanced logic chips, each with up to 4 billion transistors and billions of connections, it is critical to remember:

- Essentially all the transistors and connections have to work as intended on each chip.

- The process has to be repeatable from wafer to wafer while chip production proceeds at rates of up to 80,000 wafer starts or more per month through a fab.

Variation among transistors on a chip leads to poorer overall chip performance and must be minimized. Even trace contaminants – including those that are not specified on a standard Certificate of Analysis – can cause measurable shifts in semiconductor processes and affect chip performance in advanced devices. Given that process materials are a critical input in wafer processing, it is easy to see how

> the quality of electronic materials (EM) products becomes increasingly important for chip manufacturers at leading technology nodes.

Another important consideration is the challenge of the unknown: engineers don't know how a specific impurity might impact performance. This can lead to needing additional processes and controls, which can mean higher operational costs and more risk from higher investments. Any misstep along the way –

an impurity in a gas, for example, might interact in the process in unknown ways. Such a misstep can cost thousands or even Management millions of dollars per month.

Product

Quality

Strategy

Ensuring Engineering consistent and Operations product requires a holistic approach to quality. Account Instead of limiting Management responsibility to a quality department, it must be a priority that runs through the entire organization. As is seen in this wheel, a comprehensive quality strategy cuts across all functions that touch a product.

To meet the demands for rigorous quality control, organizations may need to hire materials scientists, chemists, and process engineers and change the culture of their organization so that every department has a strategy and plan that contributes to the overall quality vision.

Process stability across the supply chain is made possible through SPC (Statistical Process Control), SQC (Statistical Quality Control), MSA (Measurement System Analysis), and BCP (Business Continuity Planning) systems. Fingerprinting furnishes the means for rigorous measurement, reducing variability, and

integral part of the Analytical and final product. R&D SUPPLY CHAIN -Drivers reflect Quality complexity The increased demand and complexity of gases used Sourcing in electronics manufacturing not only impacts quality, but also the supply chain. Many external factors can affect the supply chain including transportation

tightening controls. Gas purity,

consistency, and reliability

are then delivered as an

or labor strikes and natural disasters. For example, after a magnitude 9.0 earthquake and subsequent tsunami hit Japan on March 11, 2011, all shipments coming in and out of Japan had to be checked for radiation.

A change in government regulations can also affect the supply chain, with an example being the 2008 Olympics. During the Beijing Summer Games, the Chinese government blocked hazardous materials from coming into multiple ports, including chemicals such as sulfuric acid, which is used in semiconductor manufacturing. Materials had to be trucked in, which required a lot of extra planning and two months extra time to deliver.

Limited raw material suppliers can impact availability for manufacturers. In order to secure supply, there is a move toward local and regional suppliers. Semiconductor manufacturers must partner with electronic materials suppliers and allow visibility into ramp demand of materials for new technologies and to do capacity planning so that together they can determine usage volumes for specialty gases.

To successfully maneuver all the complexities and potential pitfalls, it is crucial to cultivate an interlinked, comprehensive, customer-focused supply chain. Manufacturers can address these issues through Business Continuity Planning (BCP). They can start by assessing where and how to invest to diversify their supply chain on multiple continents. This includes doing procurement forecasting and planning with customers and suppliers to meet demand and identifying potential supply gaps by plotting product-source mapping.

It is essential to have at least two sources for raw materials and to have customers qualify both sources. Fabs should create raw materials, manufacturing, transportation, and labor shortage contingency plans and develop supply gap mitigation and implementation plans. Bringing materials closer to customers through localization and on-site plants cuts down on logistics complications and makes materials more readily available. It is essential to coach suppliers along

per wafer at 14 nm node x 80,000 wafers per month x 12 months =

9,600,000 cubic meters of water used per year (enough for 39,506 people in U.S.)

used per wafer at 14 nm node x 80,000 wafers per month x 12 months =

1,152,000,000 kilowatt hours or 1,152,000 megawatt hours electricity used per year (enough for 94,846 people) in U.S.)

Natural Gas 61 cubic meters used per wafer

at 14 nm node x 80,000 wafers per month x 12 months =

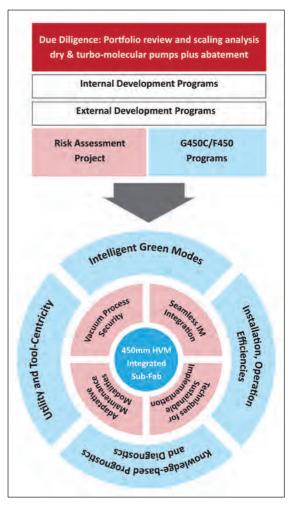

58,560,000 cubic meters of natural gas used per year (enough for 26,899 people in U.S.)